基于FPGA的远程USB高速传输系统设计

2012-06-28张继军刘小平陶治洲顾适夷范少池

张继军,刘小平,陶治洲,杨 芳,顾适夷,范少池

(1.中国电子科技集团公司55所,南京210016;2.重庆三峡职业学院,重庆404155;3.海军驻重庆453厂军事代表室,重庆400021;4.重庆江陵机械厂,重庆404020)

0 引 言

USB具有热插拔、即插即用、数据传输可靠等优点,已成为当前计算机的主要接口之一。由于USB总线具有高速传输的特性,其广泛应用于高保真图像视频传输、大容量数据采集等场合。但是,USB也存在不可逾越的限制——传输距离。

传统的延长USB传输距离的方案主要有2种:一种是使用USB 2.0专用芯片和单片机配合完成USB 2.0协议,然后通过网线或电话线等实现远距离传输,这种方案存在开发困难(涉及固件程序、上位机程序和驱动程序的开发)、成本高和速度低等缺点;另一种方案是将USB 2.0协议用FPGA的IP核实现,利用FPGA的高处理能力和可编程性作为主机和设备的中介,从而实现远距传输。但是,开发USB 2.0协议的IP核难度较大,同时要占去FPGA很多的资源,而且更重要的是如果要实现480Mb/s的高速传输,FPGA的时钟需要达到2GHz,这是困难而且不现实的。

采用了一种专业公司生产的高速USB物理层收发器(PHY)与现场可编程门阵列(FPGA)相配合的方式,利用高速USB物理层收发器来完成物理层协议,然后与现场可编程门阵列开发的符合业界标准的接口相连,进而控制了上行数据和下行数据有序的流通,实现了USB 2.0传输距离的延长,在保证信号传输正确的前提下,减少了开发周期,增加了实际运用价值,达到了高速远距透明传输的目的。

1 系统总体设计方案

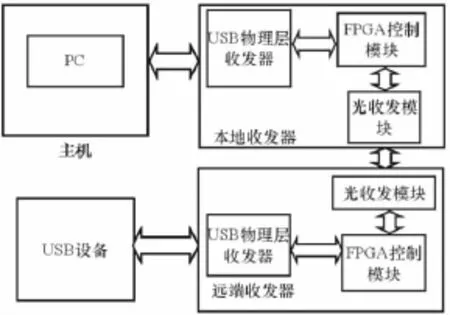

提出的USB高速远程系统设计方案可实现高速(480Mb/s)远距(10km 以上)USB协议的传输。系统整体设计方案如图1所示。系统分本地和远端两部分,分别由PC主机、USB设备、USB电缆和收发机组成。它们都严格遵从USB协议规范。PC主机对整个系统进行控制,收发机完成传输信号的转换并实现USB信号长距离传输,设备完成对PC机的响应。

图1 系统框图

设计的核心是远端和本地收发机,它延长了USB信号的有效传输距离,打破了USB协议对传输距离的限制。在系统正常工作的情况下,PC主机可以实现对设备的“透明”访问,如同将设备直接通过USB电缆连至主机一样。收发机由3个主要模块组成:

(1)USB物理接口;

(2)光收发模块;

(3)FPGA控制模块。

此外,还应有必要的供电模块及辅助电路。

2 系统的具体实现

2.1 USB物理接口

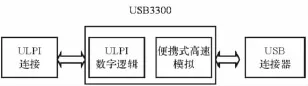

选用美国国家半导体公司提供的USB3300作为USB物理接口模块的核心芯片[1]。USB3300是一种在工业温度下工作的高速USB物理层收发器 。该芯片使用低引脚计数接口(ULPI)连接ULPI兼容链路层。ULPI接口采用在链路层和PHY之间传输频带内信号和状态字节的方法,将引脚数从UTMI+接口的54降低到现在的12[2]。

ULPI全称为UTMI+低引脚接口(UTMI+LPI),用于消除USB开发者在高速USB 2.0逻辑设计中的困难,负责处理USB总线的底层协议和信号,完成USB协议电气层上的处理任务。UTMI的关键特性主要有:向逻辑电路提供标准的UTMI接口;支持480Mb/s高速模式;数据的并-串/串-并转换;比特填充和比特解填充;比特填充错误的检测;SYNC/EOP的产生和检测;从USB的串行流中进行数据和时钟的恢复;保持寄存器用于暂存要发送和接收的数据;检测和发送恢复信号;检测复位和挂起/唤醒功能;支持在全速和高速之间切换及终端阻抗的切换。这些特征都为实现高速远距传输提供了实用的帮助。

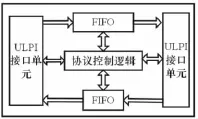

通过开发符合业界标准的ULPI接口,将高速USB3300收发器整合于设计中。通过对USB3300内部寄存器的访问来实现对该芯片的控制,ULPI USB设备框图如图2所示。该芯片与FPGA的接口只有12个,除8条数据线外,其它均可进行控制。节省了设计开发时间,简化了验证和产品测试过程,还能保证嵌入式USB核心逻辑器件与高速USB收发器的互联互通。

图2 基本ULPI USB设备框图

2.2 FPGA控制模块

2.2.1 USB协议传输过程

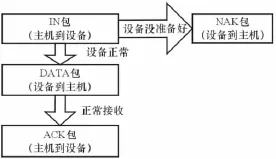

USB的事务处理包括主机发起任务、数据传输和设备应答[3]。事务处理必须在1帧内完成,而1帧的时间为1ms。如果在1帧时间里主机没有得到设备的答复,则造成1次传输错误。同时,USB协议还规定,在事务处理中,应答的等待至多为18个位时间,约为1.5μs。因此,如果传输距离太长,传输导线上的延时就会超过1帧的时间,导致传输错误。为了实现高速远距离的传输,必须对USB协议中的事务包进行相应的处理。

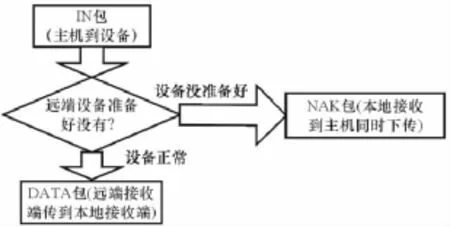

USB的事务处理主要包括IN事务处理、OUT事务处理和SETUP处理[4]。这些事务处理的本质类似,在此以IN事务处理举例说明。一般情况下如图3所示,USB主机向总线发出IN令牌包,通知某个设备准备向USB主机发送数据;当所指定的设备接收到令牌并验证后,将准备好的数据组装成DATA包由USB主机传送出去;接着当USB主机接收到数据,经校验确认其位填充、PID和CRC均无差错后,创建一个ACK握手包返回给设备,通知它主机已经正确地接收到了数据,后面再进行新的事务处理。当主机收到的DATA包错误时,握手包将不会产生,表明此事务处理过程没有成功,而主机等待一定时间后将会重新启动任务。当设备没有准备好时,它会给主机发送一个NAK握手包,表示现在还不能传输数据,而主机会在一定时间内重新启动此事务。正是基于USB协议的此特征,为USB传输延长设计提供了理论基础。

图3 IN事务处理

主机发起任务,而设备没有准备好的情况下,可以发送NAK来让主机等待,利用这一特性,设计了高速远距USB传输方案。具体的实现方案如图4所示。

主机发送IN令牌给本地收发端,由于要远距传输,设备不可能在USB协议规定的时间返回数据,于是本地收发端在将数据下行传输给设备的同时给主机返回一个NAK信号,让主机一直等待。而远端的收发端收到信号后将会直接发给设备,并将设备返回的信号上传给本地的收端。本地收发端接收到信号后,便会继续上传给主机。因此,在延长USB传输距离的同时,实现了主机和设备的透明传输。

图4 IN事务远程传输

2.2.2 FPGA设计

由于不需在FPGA内部完成USB协议IP核,采用ALTEAR公司的CYCLONE III系列EP3C10芯片完全能胜任此工作[5]。并且其功能强大、成本低廉,降低了开发风险。

FPGA内部模块如图5如示。模块由三部分组成:协议控制逻辑单元、ULPI接口逻辑单元和数据存储单元。当主机向设备发送数据时,首先由高速的USB PHY完成物理层协议,然后通过8位并行总线传输给FPGA的ULPI接口单元,协议控制逻辑单元根据所接收到的数据进行相应的处理,向主机返回NAK命令同时又将数据下传,或是直接给主机回复ASK命令以结束本次事务。当将数据下传时,则会通过下行的ULPI接口与设备进行通信。同理,如果设备要向主机传送数据时,过程类似。从上面的分析可以看出,在保证信号高速、远距传输的前提下,简化了FPGA的设计难度,降低了开发周期,减少了开发成本。

图5 FPGA内部模块图

2.3 光收发模块设计

选用美国国家半导体公司生产的S92LV1224来完成与光纤的通信。DS92LV1224是300~600Mb/s的串并转换器,支持高速的单向串行数据传输。由于其支持480Mb/s传输速度,才完成了USB 2.0协议规定的高速传输。

3 结束语

讨论了USB 2.0协议远程高速传输的原理,提供了一种基于FPGA的远程USB高速传输系统的实现方案,验证了方案的可行性。该系统主要特点包括:

(1)远距离。由于使用FPGA完成了USB 2.0协议的转换,并用光纤传输突破了协议对传输距离的约束,使传输距离达10km以上。

(2)高速性。采用专业公司生产的USB PHY高速完成物理层协议,从而真正实现了USB 2.0协议的高速传输。

(3)经济性。采用价格低廉的CYCLONE III芯片以及一些简单的模块实现了USB 2.0协议的远程传输,从而可以轻易地组装在现有大量支持USB 2.0协议的设备上,所以客户使用本系统时无需另外更换硬件,达到了经济实用的效果。

(4)简易性。FPGA只是完成了一些简单的逻辑控制,而不用设计复杂的USB2.0IP核,从而降低了开发难度,减少了开发风险。

综上所述,现有方案设计简易,经济实用,能突破USB传输距离的限制,并且保证其高速传输特性,具有较高的实用价值。

[1]SMSC.Hi-Speed USB host device or OTG PHY with ULPI low pin interface revision 1.08[EB/OL].http://www.smsc.com/index.php?tid=143&pid=28&cid=&tab=4,2007-11-07.

[2]Mentor raphics Corporation,Philips,SMSC,etal.UTMI+low pin interface specification revision[EB/OL].http://www.ulpi.org/documents.html,2004-10-20.

[3]周立功.USB 2.0与OTG规范及开发指南[M].北京:北京航空航天大学出版社,2004.

[4]肖踞雄,翁铁成,宋中庆.USB技术及其应用设计[M].北京:清华大学出版社,2003.

[5]杨登峰.基于FPGA的USB芯片设计[J].微电子与计算机,2004,21(6):39-41.