RS-485图像数据并行传输协议的FPGA设计与实现

2012-06-26蒋玉峰张志明崔麦会尹业宏

蒋玉峰,张志明,崔麦会,尹业宏

(1.海军装备研究院,北京 102249;2.华中光电技术研究所武汉光电国家实验室,湖北 武汉 430073)

同步数据链路控制(Synchronous Data Link Contro1,SDLC)是20世纪70年代IBM公司开发的面向比特的通信传输协议,采用基于SDLC同步协议的RS-485串行总线具有低差错率、强纠错力和高速远距离传输的特点[1-2],被越来越多的光电系统作为图像信息传输使用。采用专用SDLC协议控制芯片在实际中存在以下不足:1)速度受限,现有专用控制芯片传输速率约2 Mbit/s,难以满足大容量图像传输要求;2)系统中不同设备使用不相同的控制芯片,传输兼容性差;3)扩充接口数量依赖于硬件的增加。用FPGA来构造SDLC协议,在一片FPGA内能设计两路或多路总线接口,同步并行传输数据,速率成倍增加,且通过编程能修改协议,可移植性好,应用更加灵活。本文通过两路并行协议实现了高清视频的远距离传输。

1 图像传输协议的FPGA实现

1.1 图像传输系统组成

要传输的视频为高清黑白图像,像素为1024×1024。如图1所示,视频信号经10位A/D编码和8∶1压缩后,由FPGA控制存储于RAM中待传输。上述图像按照25 f/s(帧/秒)计算,传输速率需要31.25 Mbit/s。为实现高清图像的远距离传输,采用2路相同的RS-485核同步进行传输,即一个FPGA中的两个RS-485核各自完成一场图像数据的传输,再在远端图像接收装置中进行合成解码。

图1 图像传输系统框图

1.2 图像传输协议的设计

图像传输协议包括两个相同功能的RS-485核,每个核由接收和发送模块组成,其数据传送借用SDLC协议帧格式,如表1所示,协议控制框图如图2所示,下文将详细说明具体工作过程。

表1 SDLC协议帧格式[3]

图2 SDLC协议的控制框图

1.2.1 接收工作过程

本设计中,电路上电后串行数据和时钟处于接收状态,串行数据和时钟进入接收控制器后,送入删零器,同时送入串/并转换器和控制电路,当删零器检测到连续5个“1”后,产生一个脉冲给控制电路,如果5个“l”后为1个“0”,则控制电路将送到串/并转换器的时钟扣除1个,从而达到删零的目的,如果5个“l”后仍然为“l”,并且帧长度寄存器中的数据值不为零,则中止接收,并将中断向量写入中断寄存器,同时产生中断信号。控制电路还负责对帧寄存器中的数据进行计数减,当帧长寄存器中的数为零时,则中止接收,比较l6位CRC校验是否正确,如正确将接收正常中断写入中断向量寄存器,如不正确将CRC校验错写入中断向量寄存器,同时产生中断信号通知微处理器发送数据到FPGA的FIFO模块,同时启动数据发送模块[4]。

1.2.2 发送工作过程

接口电路工作在发送方式时,发送器收到启动发信号后,先发送“01111110”,然后从地址寄存器中取出控制地址发送,之后开始发送数据,待发送数据在送入移位寄存器的同时,也送入CRC校验器和插零器,如果插零器检测到5个连续的“1”,发“0”位插入脉冲给控制电路,控制电路将暂停移位寄存器工作,并且产生“0”位插入时钟,在5个“l”后插入1个“0”,从而完成“0”插入过程。控制电路还负责对帧长寄存器中的数据进行计数减,当帧长寄存器中的数为零时,将16位CRC校验码发送出去,将发送完成中断写入中断向量寄存器,并产生中断脉冲,通知FPGA将RS-485置于接收状态。

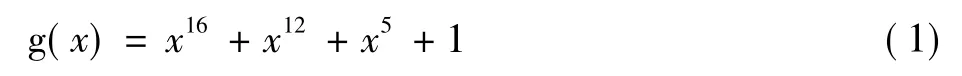

1.2.3 CRC校验

SDLC采用16位循环冗余校验码对整个帧的内容进行差错控制,其生成多项式为

根据循环系统码编码原理,编码电路示意图如图3所示。16级移位寄存器的初始状态全清零,门1开、门2关,信息位移入编码电路。一方面数据信息经或门输出,另一方面自动乘以x16后进入除g(x)除法电路,完成除法后,寄存器中的内容即为16 bit的校验元。

图3 CRC校验示意图

此时门1关、门2开,再经过16次移位后,将移位寄存器的校验元全部输出,与输入信息的校验位进行比较,若内容相同,则说明信息传送正确;否则报错,丢弃该帧。

2 仿真调试结果

采用以上方法,选用Altera公司型号为EP2S30F672I的FPGA,使用Quartus9.0对功能设计进行仿真,得到仿真波形如图4所示。图中第1行为系统复位信号SysRst.n;第2、第3行分别为串行接收数据信号RS485Rxd和接收时钟RS485RxdClk;第4行为基准时钟信号RS485ClkIn,频率为96 MHz;第5行为发送的并行数据RS485Data;倒数第2行为发送数据信号RS485Txd;倒数第1行为发送时钟信号RS485TxdClk;其余为FPGA控制逻辑信号;发送时钟信号由第4行的基准时钟信号编程分频后产生。为了使仿真结果易于直观判读,在FPGA内部产生TestData测试数据,并将分频系数设置为16。从仿真结果可知,输出时钟和数据与设计输入相吻合。

图4 基于FPGA的仿真波形图(截图)

3 结论

在某型光电产品中采用两路并行SDLC协议完成1024×1024图像的传送,传输速率可达32 Mbit/s,动态图像无失真、拖尾现象,工作稳定可靠,该方法可扩展至多路并行数据传输。

[1]NI Haiyan,HU Chao,MA Changwang.Research on a 485-serial network architecture in intelligent uptown management[C]//Proc.2006 IEEE Conf.Mechatronics and Automation.Luoyang:IEEE Press,2006:400-405.

[2]李果萍,成龙,柴波.基于SDLC协议的同步RS485总线控制器的设计[J]. 现代电子技术,2009,291(4):152-154.

[3]耿立中,王鹏,马骋,等.RS485高速数据传输协议的设计与实现[J].清华大学学报:自然科学版,2008,48(8):1311-1314.

[4]刘岩俊,闫海霞,何昕.基于FPGA的HDLC协议的实现[J].电子器件,2009,32(3):707-710.