基于USB和Camera Link的数据传输系统设计

2012-06-25王晓东曲洪丰薛盼盼

张 鑫,王晓东,曲洪丰,薛盼盼

(1.中国科学院长春光学精密机械与物理研究所,吉林 长春 130033;2.中国科学院研究生院,北京 100039)

CCD是Charge Coupled Device(电荷耦合器件)的简称。被广泛应用于工业检测、医疗仪器、天文观测、航天遥感等成像领域[1]。CCD相机的数据传输电路主要采用USB或Camera Link接口进行设计。USB是Universal Serial BUS(通用串行总线)的缩写,具有连接简单,易于扩展,支持热插拔和标准统一等优点[2],是目前使用最广泛的计算机外设接口。Camera Link接口以Channel Link芯片组为硬件基础,定义了基于图像采集系统的信号和接口形式,具有传输距离远(使用光纤传输时可达几千米),速率高(最高达650 Mbit/s)等优点,被广泛应用于图像数据采集[3]。然而使用USB作为数据传输接口时,传输速率受上位机的硬件配置,软件的运行速度以及传输距离等因素制约,实际应用时的传输速率远低于理论速度(480 Mbit/s),不能满足高速数据传输的要求。使用Camera Link接口进行数据传输时,上位机需要配置专用的图像采集卡,成本高,且使用不方便,不具备通用性。

与目前的CCD相机数据传输时,只单独采用USB和Camera Link接口不同,设计中将两种接口相结合,使上位机可以方便地通过USB接口发送命令,对CCD相机进行控制和配置。而且可以根据不同的应用要求,在传输速率较低时,选择USB接口进行输出;在USB接口不能满足传输要求的高速数据采集时,使用Camera Link接口。设计的系统结合了两种接口的优点,使CCD相机的数据传输变得简单,方便,灵活,可靠。

1 硬件电路设计

1.1 芯片选择

FPGA采用Xilinx公司的XC3S400-PQ208。它的系统门数为40万,提供288 kbyte的内部RAM和141个用户I/O引脚。FPGA的资源能够满足硬件设计和接口芯片管脚连接的要求,以及复杂逻辑电路的设计要求。

USB的接口芯片采用的是Cypress公司EZ-USB FX2系列的CY7C68013A。芯片内部集成有1个增强型的8051核、1个智能USB串行接口引擎(SIE)、1个USB收发器、16 kbyte RAM和4 kbyte FIFO等。芯片支持USB2.0协议,支持控制传输、中断传输、批量传输和同步传输模式等,且可以通过固件程序,按照使用要求对CY7C68013A进行配置。将CY7C68013A配置成Slave FIFO模式时,控制电路可以像使用普通FIFO一样对CY7C68013A端点的数据缓存进行读写操作。

Camera Link接口芯片采用的是DS90CR287。DS90 CR287最高的像素时钟为85 MHz,可以将并行的28 bit数据以及时钟信号转化为4路串行LVDS信号和1路同步LVDS时钟信号进行发送,而且能够根据数据引脚连接的不同,将Camera Link接口配置成不同的传输模式。

1.2 电路结构

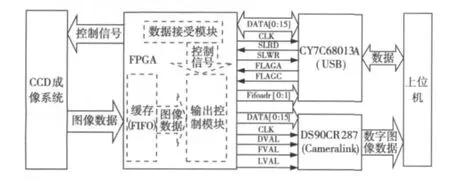

数据传输系统硬件结构如图1所示。

图1 硬件电路结构

使用FPGA作为控制芯片,接收CCD相机发送的数据,进行缓存,然后控制接口芯片向上位机进行发送。由于数据传输系统对CCD相机输入的图像数据是实时发送的,缓存的作用为匹配数据输入和输出之间速率的不同。因此设计中没有使用外部缓存,而是将FPGA提供的内部RAM配置成双端口FIFO,实现数据的缓存,降低了设计难度。使用USB接口进行数据传输时,FPGA通过标志信号(FLAGA,FLAGC),端点选择信号(FIFOADDR),读控制信号(SLRD),和写控制信号(SLWR)实现和CY7C68013A的通信控制,进行16 bit数据的传输。同步时钟由FPGA根据传输速率,输出不同频率的时钟信号。使用Camera Link接口进行数据传输时,FPGA输出DVAL(数据有效)信号、FVAL(帧有效)信号和(LVAL)行有效信号,作为数据传输的同步控制[6]。FPGA根据不同的数据传输要求,输出不同频率的同步时钟,实现向DS90CR287发送数据。

2 逻辑电路设计

设计中使用VHDL硬件描述语言实现逻辑电路的功能。逻辑电路分为数据接收模块和数据发送模块,分别完成对命令数据的接收和成像系统图像数据的输出。

2.1 数据接收模块

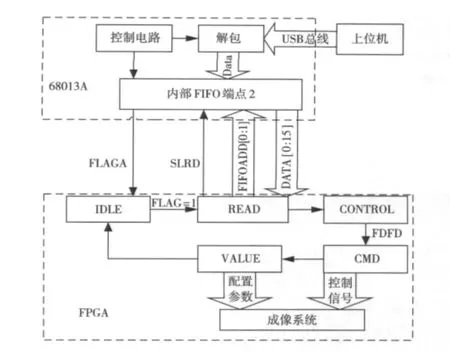

数据接收模块的作用为控制USB接口,接收上位机发送的命令数据,并输出相应的控制信号。通过固件将CY7C68013A的端点2配置成数据接收端点。使用VHDL语言设计状态机来实现逻辑电路功能。数据接收模块状态转换如图2所示。

图2 状态转换示意图

上位机发送的命令由4个16 bit数据构成:同步头(FDFDH),命令,参数,同步尾(FBFBH)。工作时,状态机首先处于IDLE,当CY7C68013A的标志信号FLAGA为高电平时,表示端点2已经接收到上位机发送的数据,并存储在内部FIFO中;READ状态时,使FIFOADDR输出“00”(选择端点2),并使SLRD信号输出低电平,在SLRD有效的期间,读取数据。当FLAGA为低电平时,表示端点2的数据已经被完全读出;CONTROL状态时判断数据内容,如果数据为FDFDH,则之后两个16 bit数据为有效命令参数;CMD状态时,读取第二个命令字,根据相应的命令给出控制信号;VALUE状态时,读取第三个命令字,对成像系统进行参数配置,完成后进入IDLE状态,等待进行下一次命令数据的接收。

2.2 数据发送模块

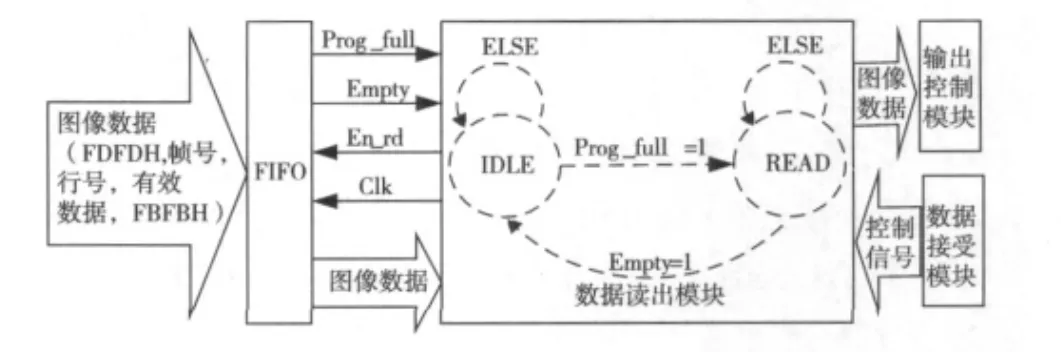

数据发送模块的作用是对CCD相机输入的图像数据通过FIFO进行缓存,并将数据通过USB接口或Camera Link输出。使用状态机来实现逻辑电路的功能。数据输出模块结构如图3所示。

图3 数据输出模块结构

将FPGA内部的RAM配置成双端口FIFO,数据读出模块通过Prog_full,Empty,En_rd信号对FIFO进行读出控制。Prog_full有效时表示FIFO内已经存入2000个16 bit数据(由配置FIFO时设置);Empty信号有效时表示FIFO中数据被完全读出;En_rd为读FIFO使能信号。为了在对数据的处理时能够正确的识别和显示每一幅图像,在每一行的图像数据中分别添加了标识:同步头(FDFDH),帧号,行号,同步尾(FBFBH)。数据读出模块中,当状态机处于IDLE时,如果Prog_full有效,状态机跳转到READ状态;在READ状态时,使En_rd信号有效,读出FIFO中的图像数据,并传输给接口控制模块进行输出;当Empty信号有效时,状态机跳转到IDLE状态,等待下一次数据的读出。通过状态机的循环控制,将每一帧图像数据完整地传输到Camera Link或USB接口控制模块。

选择Camera Link接口进行传输时,控制信号为DVAL、FVAL、LVAL,高电平有效。设计中使 DVAL 和FVAL在每一帧数据传输时有效,在一帧的时间内保持高电平;LVAL信号则是在读出FIFO数据时有效,当数据为同步头(FDFDH)时,LVAL开始输出高电平,当数据为同步尾(FBFBH)时,表示一行数据结束,LVAL输出低电平。使DVAL和FVAL信号对一帧图像数据进行同步,LVAL对一行图像数据进行同步。

选择USB接口进行传输时,FPGA选择CY7C68013A的端点6进行数据输出。通过状态机对数据输出进行控制:处于IDLE状态时,如果FLAGC信号为高电平,则表明上位机发出读数请求,端点6的FIFO未满,可以向CY7C68013A发送数据,使FIFOADDR输出“10”(选择端点6),跳转入SEND状态。SEND状态时,使SLWR信号输出高电平,将FIFO1中的数据输出。如果FLAGC为低,表明端点6中FIFO已满,停止数据传输,并跳转到IDLE状态,等待重新开始数据传输[7-8]。

3 软件设计

软件设计主要包括两个部分:USB固件程序设计和应用程序设计。

3.1 固件程序

固件程序是指运行在CY7C68013A中8051核的程序,负责初始化,设置工作模式等。使用Keil软件,对Cypress公司提供的固件程序框架进行修改,下载到芯片中,进行重新配置,实现USB设备的重枚举。设计时,调用用户函数TD_Poll(),对重要寄存器进行赋值:IFCONFIG=0x03,选择数据传输的同步时钟由FPGA提供;EP2CFG=0xA0,将2端点配置为数据输出端点,设置4倍缓存;EP6CFG=0xE0,将6端点配置为数据输入端点,设置4倍缓存[9]。固件程序通过上位机进行配置,打开应用程序时,自动读取指定路径的固件程序bit文件,完成对固件程序的加载。

3.2 应用程序

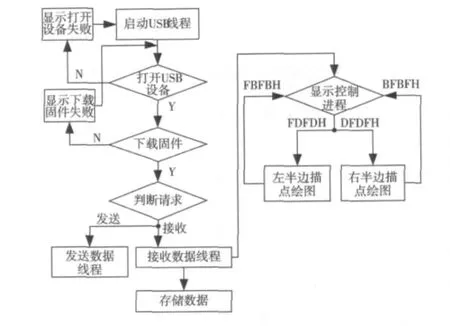

Camera Link使用接口发送数据时,使用的是数据采集卡,配有专用的软件,应用程序主要完成的是控制USB接口进行数据接收和发送,以及图像数据的存储和显示。使用VC++6.0进行设计,应用程序的流程如图4所示。

图4 应用程序流程图

使用Windows提供的CreateFile函数来完成对USB设备的操作,该函数返回设备对象的句柄,设备的句柄是Windows指定给每个设备唯一的标示符。应用程序得到设备的句柄后,就可以使用各个Win32函数访问,如ReadFile、WriteFile、DeviceIoControl和 CloseHandle 等。通过这些函数完成启动USB线程,打开USB设备,自动加载指定路径的固件程序,以及数据接收和数据发送。

发送数据时,应用程序向CY7C68013A写入512个16 bit数据,前4个16 bit数据为有效的命令数据,包括同步头(FDFDH)、命令、参数、同步尾(FBFBH)。数据接收时,在上位机内存中开辟缓存,然后将数据以TXT文本的形式存入硬盘。图像显示时,通过判断同步头,帧号,行号,同步尾,将一帧图像的每一行识别出来,将同步头FDFDH和同步尾FBFBH之间的有效数据,按照像素顺序,进行显示。通过不断的识别每行数据的帧号、行号,将一帧图像完整的显示出来[9]。

4 实验验证

采用以背照式CCD47-10为传感器设计的相机对数据传输系统进行验证。该相机用于对微弱目标的探测,CCD的像元数为1072×1027,双通道输出。相机工作时,上位机通过USB接口发出命令,设置CCD的像素读出速率为5 MHz,设置积分时间为100 ms,配置视频处理器中的增益和偏置等参数,控制相机开始或停止工作。成像系统输出的数据速率为160 Mbit/s,采用Camera Link接口向上位机进行数据发送。如图5所示,是CCD47-10相机对光栅所成的图像。实验结果表明,数据传输系统能够将图像数据完整、准确、实时地传输到上位机,并正确的显示。

5 结论

图5 光栅成像图(载图)

采用USB和Camera Link接口设计的数据传输系统,结构简单,性能稳定,使用灵活方便,结合了 USB和Camera Link接口的优点。数据传输系统使CCD相机和上位机之间可以进行控制命令和高速率、大容量图像数据的传输。能够适用于不同数据传输要求的CCD成像系统中,有很好的通用性和使用价值。

[1]王庆有.CCD应用技术[M].天津:天津大学出版社,2002.

[2]戴进,徐志祥.基于USB2.0的红外图像采集系统的设计与实现[J].激光与红外,2005,35(1):22-25.

[3]徐志跃,张田甜.基于Camera Link的串行图像采集系统设计[J].计算机应用,2010,30(6):1071-1073.

[4]CCD47-10 AIMO back illuminated compact pack high performance CCD sensor[EB/OL].[2011-06-15].http://www.ccd.com/pdf/ccd_47.pdf.

[5]周彬,牛俊邦,魏娇.基于USB2.0低功耗实时数据采集系统的设计[J].仪表技术与传感器,2009(4):33-35.

[6]李宁,王俊发.基于Camera Link的高速数据采集系统[J].红外,2005(7):31-37.

[7]戴小俊,杨绪光,丁铁夫,等.基于USB2.0的高速数据通信接口设计[J].电子器件,2006,29(4):1320-1324.

[8]李文宫,武传华.采用CY7C68013A的USB系统固件程序设计[J].电子工程,2007(4):33-35.

[9]Huanor,USB2.0+FPGA 开发文档[EB/OL].[2011-06-12].http://www.huanor.com.