基于FPGA的数字存储系统硬件设计

2012-06-25李石林段吉海晋良念谢跃雷

李石林,段吉海,晋良念,谢跃雷

(桂林电子科技大学信息与通信学院,广西 桂林 541004)

数字射频存储器(DRFM)是一种微波和射频存储系统,它以数字存储和高速采样为技术基础,一般用于射频和微波信号的存储及转发,主要应用于电子对抗和雷达等领域。它主要由射频前端部分和数据处理部分组成,射频部分主要包括下变频模块和上变频模块。本文主要阐述基于FPGA的数字射频存储器数据处理部分的硬件设计。数据处理部分的设计思想主要是通过充分利用FPGA内部的丰富资源和高速时钟管理资源,与其他件器件如DDR2,ADC,DAC,MUC通过专用接口与之相连,使FPGA作为数据传递的桥梁和选择数据通路的控制中心[1]。数字射频存储器的数据处理部分可以完成数据采集、数据存储、数据回放及上位机通信等不同功能[1]。

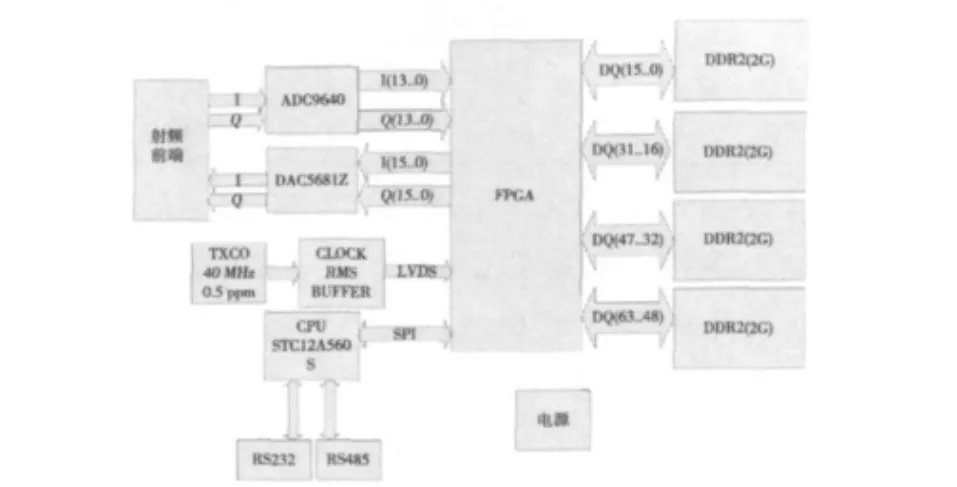

1 系统的整体架构

该设计的出发点就是为了实现把1个宽频基带信号进行定时存储,即在数据处理部分实现数据采集、数据存储、数据回放及上位机通信等功能。该系统以EP3C40F484I7为核心,由存储模块、AD/DA转换模块、MUC控制模块及电源模块等构成。设计思想是射频信号经射频前端模块下变频后,变成I/Q两路模拟基带信号,送给AD9640进行模数转换,然后送给FPGA进行数据处理和数据缓存,而后把数据送到DDR2中进行定时存储,存储时间通过上位机设定。再把数据调出送给DAC5681Z进行数模转换。最后射频前端把数据进行上变频重新发生出去。从而实现上述应用要求,系统整体架构如图1所示。

图1 系统整体架构

2 系统的硬件设计

2.1 AD和DA模块

本文采用ADI公司的AD9640作为模数转换芯片。AD9640为双通道,是1款高度集成的14位高速A/D变换芯片。其具有 80 MS/s(兆采样/秒),105 MS/s,125 MS/s,150 MS/s 4种速度级别可供选择。AD9640供电电为1.8 V模拟电源,输出电平可以设置为1.8~3.3 V COMS电平或1.8 V LVDS电平,支持SPI控制[2]。它主要应用在通信系统、智能天线系统、I/Q解调系统、多模式数字接收机、宽频数据应用等方面[2]。数模转换部分选用 TI公司的DAC5862Z作为数模转换芯片[3],DAC5682Z是1款双通道、16位、1GSPS DAC,具有宽带LVDS数据输入、片内集成2x/4x插值滤波器、板上时钟乘法器和内部电压基准。DAC5682Z在线性度、噪声、串扰及PLL相位噪声等方面都有较好的性能。它主要应用在宽带无线接入技术、电缆调制解调器终端系统、WiMAX/802.16、蜂窝基站等方面。

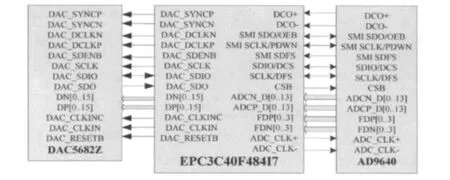

该设计输入的模拟信号是带宽高达48 MHz的I/Q两路基带信号,根据奈奎斯特采样定理和FPGA锁相环提供的时钟情况选用采样速率为125 MS/s的AD芯片,信号传输中采用的LVDS电平传输模式,LVDS电平模式可以极大程度地抑制共模噪声。AD9640在设计中的作用就是将I/Q两路基带转换成LVDS电平模式的数字基带信号,AD9640的启动和控制通过 SPI接口来设置。DAC5682Z用来把延时处理好的数据转换成模拟基带信号,系统中的核心处理芯片选用EP3C40F484I7。由于采用LVDS电平模式进行传输,而CycloneIII芯片在进行LVDS 接口设计时芯片左右bank 上,也就是1,2,5,6bank,设计了“专用输出缓冲区”,即左右bank发送差分信号不需要外接匹配电阻,结合DDR2对速度的要求,把FPGA左边bank用来作为AD9640的接口端,右边bank作为DAC5682Z接口端。采用CycloneIII芯片来传输差分信号时有两点需要特别注意:1)FPGA 上下bank,即3,4,7,8 bank,没有“专用输出缓冲区”,如果要做差分信号输出使用,需要匹配电阻网络;2)FPGA LVDS接口输入差分信号时,无论哪个bank,都需要100 Ω匹配电阻。这个电阻一定要在最远的接收器输入端,最好使用高精度的贴片电阻跨界在差分线上。AD9640和DAC5682Z的差分时钟由FPGA的PLL提供,需注意的是DAC5682Z为优化PLL电路在LVDS时钟内部接口电路中没有设计终端匹配电阻(DAC5682Z的LVDS宽带数据输入内部电路中有终端匹配电阻)。在布线时有如下要求:1)时钟信号线、输入端信号线尽量等长,以减少时延误差和时钟抖动。2)时钟线尽量短,100 Ω的终端匹配电阻和交流耦合电容应尽量靠近输时钟输入端引脚,对时钟线尽量采用保护地,需要特别注意的是同层或相邻层不能有走线与时钟线在位置上近距离平行,时钟线路优先采用单点直到的主动方法。3)采用数字部分与模拟部分单点接地,单点接地的地方在AD/DA芯片变换的地方,这样可以保证数字信号线参考地的回路路径较短,阻抗连续。图2为AD9640与DAC5682Z外围接口电路图。

图2 AD9640与DAC5682Z外围接口电路图

2.2 DDR2接口电路设计及分析

该设计的主要硬件指标就是能把1个射频信号进行定时存储一段设计,存储的最大时间为1 s。由于模数转换芯片是14位,采样速率为125 MS/s。即其1 s的转换数据达到了1.75 Gbyte,也就是说如果要使差分信号延时1 s就需要向2片大于1.75 Gbyte的存储芯片写数据。系统中数据输入流是连续不断的,FPGA必须对数据进行读写同时操作,也就是进行乒乓操作,则需要4片大于1.75 Gbyte的存储芯片。为了解决设计中要求对高速和海量数据缓存的问题,该系统选用2 Gbyte DDR2芯片MT47H128M16-16 Meg x16 x 8 banks作为海量存储系统的的存储芯片。

DDR2是由JEDEC(电子设备工程联合委员会)定义的新下一代内存技术标准,是DDR内存的换代产品。相对应DDR,DDR2拥有更少的能耗和发热量,更高的密度和频率,更好的高速效能,拥有2倍于DDR的预读取能力(即4位预存取技术),能以4倍于外部总线的速度进行数据的读取,及4倍于内部控制总线的速度运行。此外,DDR2还采用了离线驱动调制(OCD,off-Chip Drive)、片内终结器ODT(On-Die Termination)、前置CAS(Post Column Address Strobe)3项新技术,提升了内存带宽的利用率。因此,DDR2已经取代DDR成为主流存储器配置[4]。

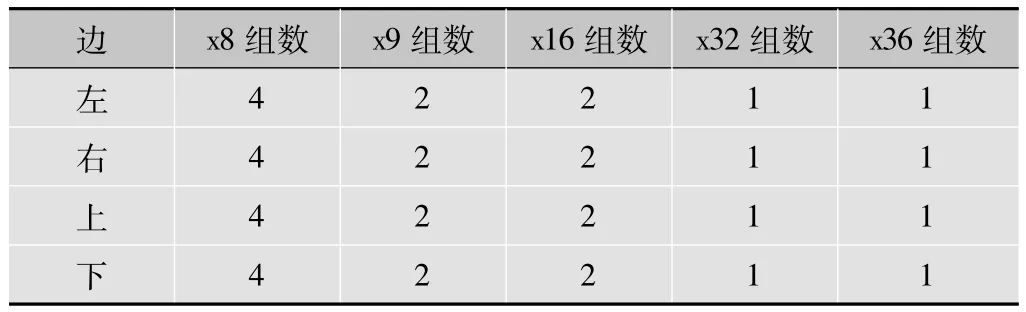

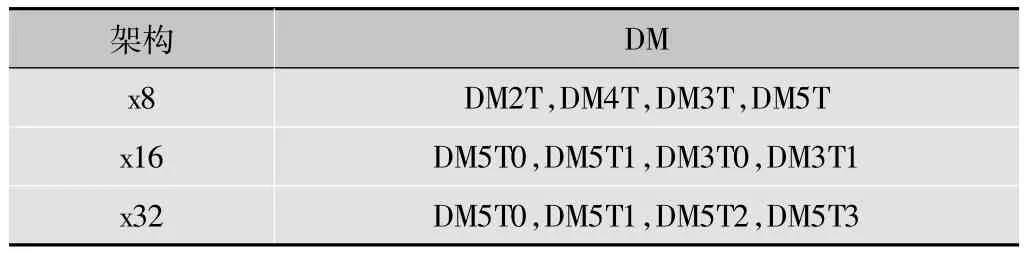

该设计选用EP3C484I7作为DDR2的控制器。采用2个IP核对4片DDR2进行控制。所以每2片DDR2以地址控制线共用、数据线独立的方式进行连接。由于FPGA Top和Bottom的bank管脚速度比Right和Left的bank管脚速度快。该设计把4片DDR2分别挂在FPGA的Top和Bottom的4个bank上。DDR2中若干条数据线(DQ)伴随个1个采用时钟信号(DQS)进行采样,与FPGA连接时FPGA内部须以若干个DQ和1个DQS为最小单位进行分组。EP3C484I7 bank的DQ分配情况如表1所示(x8组表示1个DQS和8个DQ组成的1个组,表格中的“4”表示FPGA的每边都支持4个x8组,而每边有2个bank,即每个 bank 拥有2 个 x8 组)[5]。

表1 FPGA DQ分布

由于设计中采用Top和Bottom边的bank,下面利用FPGA Top上的2个bank介绍DDR2的设计的思想及注意事项。Top的2个bank为bank7和bank8,bank7中有DQS0T,DQS2T和DQS4T,若干个DQ和1个DQS组成1个组,但是这里要特别注意DQS0T没有自己的DQ,bank8拥有DQS3T和DQS5T。在设计DDR2接口电路时,首先要知道DDR2分为x8,x16,x32这3种架构。在设计x8架构的DDR2接口电路时,FPGA中的DQS4T和DQS2T各有8个自己的DQ,DQS3T和DQS5T各有9个属于自己的DQ,DQS0T没有自己的DQ。对于x16架构的DDR2,FPGA中的DQS3T和DQS5T有18个属于自己的DQ。而设计x32架构的DDR2接口电路时,FPGA bank7和bank8中的DQS5T共有36个属于自己的DQ[4]。

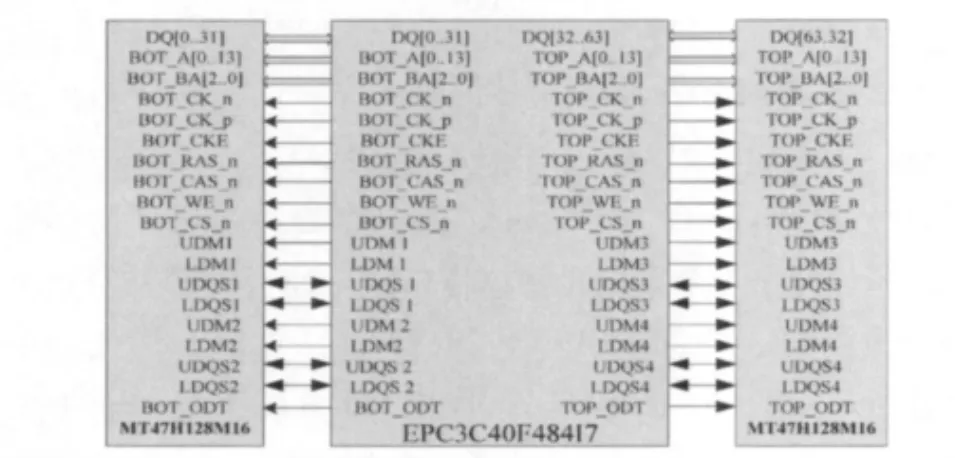

该设计中使用的DDR2芯片为镁光公司的MT47H128M16–16 Meg x16 x 8 banks,其芯片的容量大小128 M ×16 bit,即2 Gbit,每1 片分为8 个bank,每个bank 为16 M×16 bit。这里需要特别注意的是此处×16,并不是设计中要用x16架构的DDR2,如果设计时按照FPGA上x16架构的管脚去设计,就会出错。虽然该DDR2是16位的带宽,但其却有2个DQS,分别是LDQS和UQDS,也就是说其实2个DQS分别采样低8位和高8位数据[5]。所以这里只能使用x8架构来设计接口电路,DDR2接口电路图如图3所示。在DDR接口电路设计中,DQS和DQ需要有专用引脚,DM(写数据选择)也需要专有引脚进行连接。DDR2中DM为在数据信号(DQ)屏蔽位,DM是以8 bit为单位起作用的,所以理论上只要有8个DQ便会有1个DM。FPGA的Top边bank中DM的分配如表2所示[5]。

图3 DDR2接口电路图

确定DDR2架构,即确定了DDR2和FPGA的DQS,DM的连接方式。DQ需注意的是DDR2接口采用1.8V的SSTL电平进行数据传输,输入信号需要和1个高精度的参考电压(VREF)进行比较输出后才被认为是实际输入[6]。因此DDR2所在FPGA的bank电压必须是1.8 V,还要使用该bank上的VREF作为参考电压,FPGA的每个bank上都有自己的VREF。在电源芯片选择时需选高品质的电源芯片(该设计中采用高精度线性电源芯片TPS51100D提供参考电压)用来向DDR2的VREF和FPGA的VREF提供电源。DDR2的地址线和控制线在FPGA上没有专用引脚,按自己的走线要求可以任意选用空余的I/O口进行设计。DDR2接口电路设计管脚分配时建议使用Quartus II软件自动分配管。DDR2的时钟线尽量要求短,所以可以选择临近的差分I/O管脚当作DDR2的时钟。

表2 FPGA的Top边bank中DM的分配

在设计中需注意,DDR2 SDRAM的ODT技术,ODT是DDR2内部的终端使能匹配电阻,使用ODT管脚时,它对 DQ[15:0],LDM,UDM,LDQS,LDQS#,UDQS 和 UDQS#实现了内部匹配,内部终端阻抗值可以有多种选择,如0 Ω,50 Ω,75 Ω,150 Ω 等[3]。并且内存控制器可以根据系统内干扰信号的强度自动调整阻值的大小。需要注意地址和控制信号线需要外部的匹配终结。

DDR2在PCB设计时,由于它是高速走线,必须要考虑走线时的信号完整性,为满足合理的设计要求,设计中一般按下面的形式进行分组[5]:

1)DQ[0:7],DM3B,DQS3B 此10根线为1组,在同一层进行布线;

2)DQ[8:15],DM5B,DQS5B 此10根线为1组,在同一层进行布线;

3)DQ[16:23],DM2B,DQS2B 此10根线为1组,在同一层进行布线;

4)DQ[24:31],DM4B,DQS4B 此10根线为1组,在同一层进行布线;

5)DQ[32:39],DM2T,DQS2T 此 10 根线为1组,在同一层进行布线;

6)DQ[40:47],DM4T,DQS4T 此 10 根线为1组,在同一层进行布线;

7)DQ[48:55],DM3T,DQS3T 此10 根线为1 组,在同一层进行布线;

8)DQ[56:63],DM5T,DQS5T 此10 根线为1 组,在同一层进行布线。

上面8组,1)和2)为1片DDR2的管脚;3)和4)为1片DDR2的管脚,分配在FPGA Bottom边的bank3和bank4中;5)和6)为1片DDR2的管脚;7)和8)为1片DDR2的管脚,分配在FPGA Top边的bank7和bank8中,接口电路如图3所示。PCB设计时需要注意如下要求:1)在组内,要求线与线之间的误差控制在10 mil(1 mil=10-3in=2.54×10-3cm)以内,组与组之间的要求误差控制在20 mil以内。2)布线时FPGA里的DQS和DM这2个管脚不可以替换,DQS专属DQ可以相互换动。3)布线时先布重要的线,对DDR2的布线顺序一般先布数据线(数据线尽量短),即上面8组(每组10根线),再布地址和控制线,然后布时钟线,最后布电源线。4)所有信号走线都应有完整的参考平面,一般重要信号线放在邻近地平面那层,以地平面作为参考平面,不要跨越平面进行布线,要确保信号回流时完整。该设计用5 mil大小的线布信号线、时钟线和数据线,组内线与线之间的间距为10 mil,与其他DDR2数据线间距为15 mil,地址控制线的要求与数据一样。

2.3 MUC模块

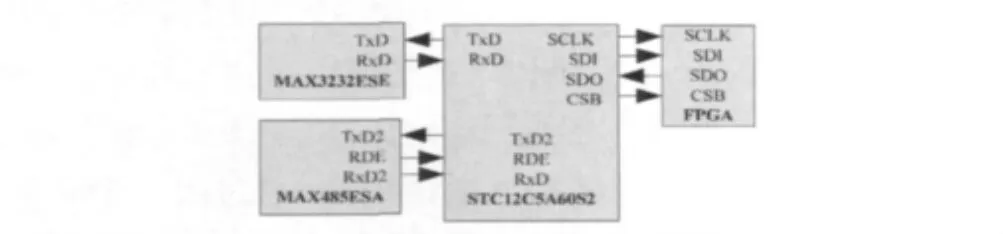

MUC主要用来做485或者232通信,以及与FPGA之间的通信[7]。其工作原理是通过上位机(PC机)发出的命令首先给下位机(MUC),下位机再根据此命令解释成相应时序信号直接控制相应设备。即通过上位机发出存储时间的命令给单片机,然后单片机通过SPI接口把相应时序传输给FPGA,从而达到定时存储的目的。下位机不时读取设备状态数据,反馈给上位机。MUC接口电路如图4所示。

图4 MUC接口电路

3 结论

本文详细介绍了一种基于EP3C40F484I7为核心的超大容量存储系统的设计思想,以及设计中需要注意的问题。系统电路板现已成功配置和运行。系统测试时输入带宽为8 MHz的QAM信号,AD/DA采样时钟选择为125 MS/s,DDR2能存储信息最长时间达到了1.14 s,结果证明系统完全能达到设计要求的1 s存储时间。在工程应用中输入带肩比为50 dB、带宽为48 MHz的基带QAM信号时,在没有对信号进行信号处理的情况下,存储器对信号进行存储后输出,信号带肩比还能大于42 dB,完全符合该工程的要求。该存储系统在数字电视、雷达等方面有较为广阔的应用前景。

[1]霍强,夏宇闻.基于FPGA的数字射频存储器的设计与实现[C]//全国第十二届信号与信息处理、第六届DSP应用技术联合学术会议论文集.[S.l.]:中国航空学会,中国电子学会,2008:243-245.

[2]AnalogDevice.AD9640Datasheet[EB/OL].[2011-08-22].http://www.analog.com/static/imported-files/data_sheets/AD9640.pdf.

[3]TEXASINSTRUMETS.DAC5682ZDatasheet[EB/OL].[2011-08-22].http://focus.ti.com.cn/cn/lit/ds/symlink/dac5682z.p-df.

[4]ExternalMemoryInterfaceHandbook[EB/OL].[2011-08-22].http://www.altera.com.

[5]基于Cyclone III FPGA的DDR2接口设计分析[EB/OL].[2011-08-22].http://www.21ic.com/app/eda/201104/81815.htm.

[6]吴继华,蔡海宁,王诚.AlteraFPGA/CPLD设计[M].北京:人民邮电出版社,2011:85-99.

[7]华清远见嵌入式培训中心.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2008.