宽带DRFM雷达干扰机信号处理模块设计

2012-06-13杨春

杨 春

(中国西南电子技术研究所,成都 610036)

宽带DRFM雷达干扰机信号处理模块设计

杨 春

(中国西南电子技术研究所,成都 610036)

给出了宽带数字射频存储器(DRFM)雷达干扰机信号处理模块组成框图以及信号处理流程,描述了模块实现的关键技术,特别是在FPGA中实现高速信号并行处理的方法。该信号处理模块可以提供1 GHz瞬时处理带宽,存储深度达到2 048 μ s,可实现对新体制宽带雷达有效干扰,具有广阔的应用前景。

雷达干扰机;数字射频存储器;信号处理;高速传输;并行处理

1 引 言

DRFM经过30多年的发展,在采样频率、分辨率、存储容量、功耗等方面都有了显著提高。例如,英国EW-ST公司的Chameleon 2 Radar Target and Simulator瞬时带宽达到400MHz,最大存储时间为500 μ s;美国KOR电子公司的Kor-1027瞬时带宽为800 MHz,分辨率为8 bit,存储长度340 μ s;Whittaker公司的MIP-810瞬时带宽为110MHz,分辨率为8 bit,存储长度达到1 048 μ s[1]。但近年来 ,瞬时带宽400 MHz以上宽带雷达的出现,已有DRFM产品已经不能满足当前大时、频宽信号的数据采集和波形产生要求,因此研制小体积、瞬时处理带宽达到1 GHz以上的弹、机载干扰机,满足未来电子战要求变得十分迫切,而高速宽带DRFM信号处理模块是DRFM干扰机的核心组成部分,研究高速宽带DRFM信号处理模块变得非常必要[2]。

2 宽带DRFM信号处理设计

2.1 信号处理平台组成

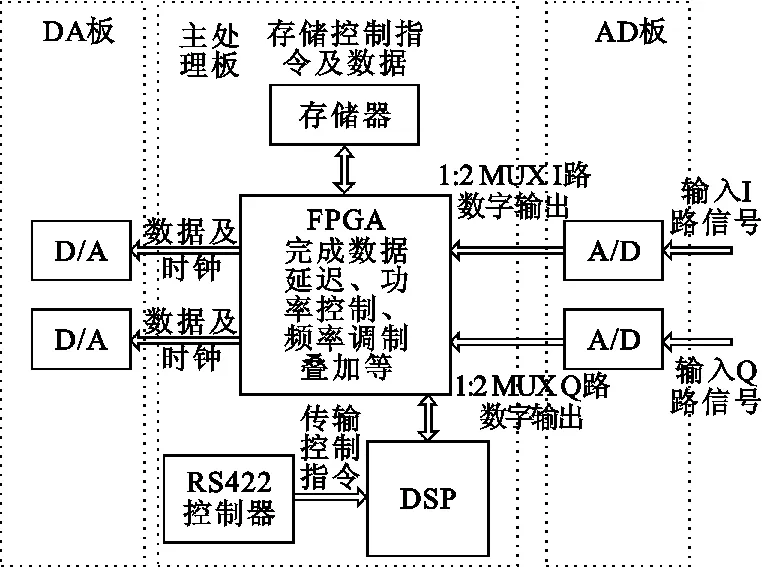

该平台主要由主处理板、A/D板、D/A板三大部分组成,如图1所示。其中主处理板主要由FPGA、DSP、RS422接口控制器、DDRII SDRAM 存储器等组成,由DSP实现对被干扰雷达工作方式识别,FPGA完成干扰信号产生,SDRAM存储接收到的雷达信号。该板主要完成对接收到的雷达信号存储,并以该信号为模板生成距离拖引、速度拖引、多假目标等类型干扰信号。A/D板完成对正交解调后I/Q两通道500 MHz宽带雷达信号放大及高速数据采集(该干扰机为全相参工作方式,为了保留接收雷达信号相位信息,因此采用正交解调得到I/Q两路正交基带信号,保证信号处理后产生与雷达相参干扰信号,同时该方式还可避免频谱折叠效应产生信噪比损失)。根据奈奎斯特第一采样定律,为保证信号能无失真还原,采样速率必须是信号带宽2倍,因此ADC必须以1GHz速率对每个通道进行高速采样。为了降低后端信号处理压力,ADC按照1∶2模式向FPGA输出2路500MHz速率数字信号。DA板主要完成调制后宽带数字干扰信号数模转换。

图1 硬件平台框图Fig.1Hardware block diagram

2.2 信号处理工作流程

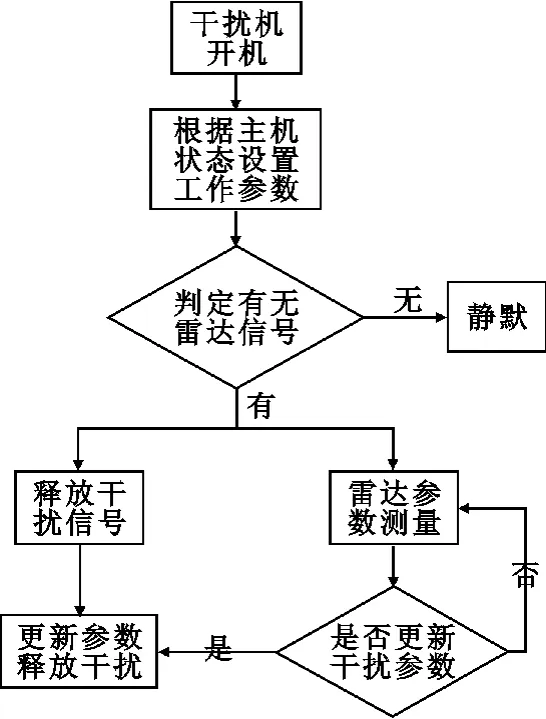

信号处理开机后首先通过RS422接口芯片接收控制主机传来的当前系统飞行状态、控制指令等信号,并将其存入DSP。同时干扰机信号处理系统工作于侦收状态,由高速A/D板采集前端宽带模拟信号,由DSP对采集后信号做多点叠加,当叠加后数值超过某门限值时,判为有雷达信号进入,然后DSP对该信号进行解算,判断其是否为线性调制信号,以及是否存在频率捷变等。随后,DSP根据存储飞行状态、起始距离以及对被干扰雷达工作状态的解算结果等信息,自动产生对FPGA控制信号,控制FPGA产生干扰信号输出延时和输出功率并对信号叠加多普勒频移,然后对存储数据段做整体放大、延迟、叠加后动态调节输出到高速DA,转换成宽带模拟信号送往前端收发组件和功放,由收发组件和功放将信号放大后,通过天线发射干扰信号。如果叠加信号未超过门限,则继续静默侦收雷达信号。其工作流程如图2所示。

图2 信号处理工作流程Fig.2 Signal processing workflow

3 宽带DRFM信号处理关键技术

当前,大多数脉冲多普勒雷达都对接收到回波信号进行脉冲压缩和相参积累,因此,干扰机发出信号必须与雷达发射信号相参,否则雷达做相干处理时会因为干扰信号与雷达发射信号不相参,导致干扰信号在雷达脉冲压缩后不能达到雷达目标判定门限,干扰信号被当作噪声处理掉,进而不能对雷达形成有效干扰。要产生与雷达相参干扰信号,首先必须采用正交解调方式以保留雷达发射信号幅度和相位信息,同时在信号处理过程中尽量保持I/Q两通道的幅度和相位一致性,做到最终信号处理后输出干扰信号与雷达信号相参[3]。该干扰机信号处理速率高,现有高速DSP与FPGA串行信号处理方式都已无法满足信号处理速度要求,因此提出了一种在FPGA内部实现并行信号处理方法,以满足高速信号处理要求。

3.1 幅度和相位一致性

在宽带DRFM信号处理中,由于ADC模数转换和DAC数模变换均采用1GHz高采样率和IQ正交双通道,因此采样速率高、通道数量多,很容易因通道间时序误差造成数据错位,进而导致输出干扰信号I、Q路幅度相位不一致,使干扰信号被雷达脉冲压缩后不能进行有效能量积累,导致无法对雷达形成有效干扰。因此要保证干扰信号的有效性,就必须保证I、Q路信号在信号处理的过程中幅度和相位高度一致。因此,建议采用以下措施保证信号处理的幅度和相位一致性。

3.1.1 宽带运算放大器进行信号放大

为了降低在宽带情况下不同频率信号的畸变,并减少I、Q两路模拟信号间幅度差,输入AD前的模拟信号放大采用宽带运算放大器。宽带运算放大器相对于射频耦合变压器,不同频率间信号幅度一致性更好,不同通道间延迟也更加稳定一致。

3.1.2 保证各通道走线长度尽量一致

ADC单通道按照1∶2降速率输出,因此AD板要向FPGA输出4组8 bit 500MHz双通道高速数字信号。如不采取走线等长控制,数字信号间的相位差,以及数字信号和时钟信号相位差,很容易导致FPGA锁存数据时发生错位,导致输出I/Q两路干扰信号相位不一致。

综上所述,头颈部神经内分泌癌患者PI3K、Glut-1、p-Akt及HIF-1α表现为高表达,其生存情况和发生远处转移有联系。

同样,DA板也存在相同问题,DAC变换器数字输入端各路数字信号与转换时钟信号走线长度也必须尽量一致,最后还要将各通道DA输出端到DA板输出接口布线长度尽量相同,以减小传输引起相位差。

3.1.3 高稳定时钟信号

由于该系统1 GHz的采样转换率,因此其通道间采样时钟抖动要求小于10 ps。为了整个信号处理的全相参,信号处理的主时钟和AD、DA转换时钟全部采用射频前端提供的基准时钟通过模拟锁相环和高速时钟分配器共同提供高稳定时钟,确保各路时钟相位和波形最小畸变,以保证系统全相参处理。

3.2 FPGA快速并行处理技术

为保证系统最小反应时间,要求从AD接收到信号到DA转发出相应信号时延最小。而采用流水线方式进行信号处理是FPGA长处,但由于输入FPGA的信号速率为500MHz的4路8 bit信号,输出给DA的信号为500MHz的4路DDR 8 bit信号,而当前FPGA的全局时钟最高为300 MHz,如何在满足响应时间前提下处理多路高速信号是一个严峻的课题[4]。

FPGA内部由多个bank组成,并且每个bank都有若干对区域时钟,其最高工作频率可达550 MHz,但只能驱动该bank所在管脚。FPGA内部每个bank上都有ISERDES和OSERDES硬件资源,ISERDES用于完成高速信号的串并转换实现对高速信号的降速,OSERDES用于实现将低速信号并串转换合成为高速信号,利用FPGA的该特性,可以完成信号的分频与合并。

基于以上特性,为了实现FPGA的快速并行处理,考虑采用以下解决方案:将AD板送来的I路或Q路两路信号分别集中于FPGA的某bank上,并以500MHz时钟作为该bank区域时钟;在区域时钟的驱动下,利用ISERDES将输入的各路500 MHz信号分频为5路100 MHz信号;分频后信号在FPGA内完成相应信号处理后,通过OSERDES合并为500MHz DDR信号,用源自D/A的500 MHz时钟同步后输出到D/A。

这样,既保证了FPGA内部对各路信号的高速处理,也实现了对输入信号的快速响应,使整个流程具有最小延迟。实现方案如图3所示。

图3 FPGA快速并行处理Fig.3 High-speed FPGA parallel processing

4 DRFM信号处理结构

当前DRFM干扰机有以下3种结构方式,现就每种结构方式进行对比分析[5]。

4.1 单通道 DRFM

输入射频信号经混频器下变频到中频后,经过A/D采样,将数字信号保存在高速存储器中。采用该结构DFRM所需器件少,技术要求低,但瞬时带宽较窄,现在大多已不采用该结构。

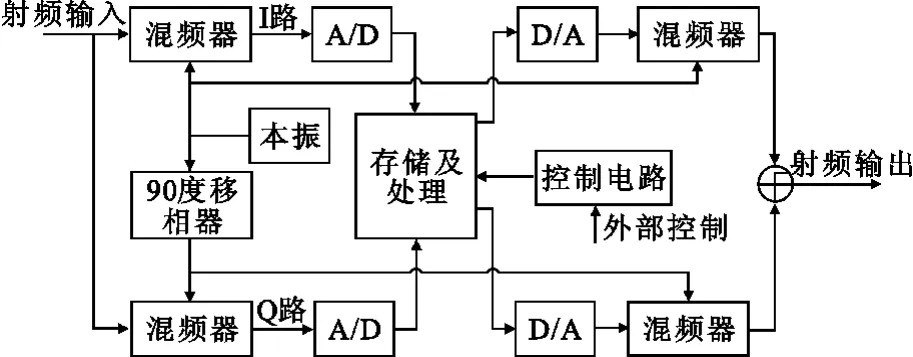

4.2 正交双通道DRFM

射频信号被功分成两路,通过混频器下变频到中频信号产生同相分量(I路)和正交分量(Q路),两路信号分别进行滤波、存储和重构,最后合成输出,如图4所示。采用该结构可以获得高瞬时带宽,但缺点是如果I、Q通道间的增益与相位不平衡将导致输出信号虚假信号较多[6]。该模式是当前使用最多的结构方式。

图4 正交双通道中频采样DRFM框图Fig.4 Orthogonal dual-channel IF sampling DR FM diagram

4.3 信道化DRFM

采用信道化方式将输入宽带射频信号通过多个混频器将其下变频为多路窄带信号进行处理,最后再上变频后将其合成为宽带干扰信号[7]。该方式可以获得较高的信号瞬时处理带宽,但要求每个信道高带外抑制比,以及每个通道信号处理的幅度和相位高一致性。一旦无法满足以上要求将导致信号混叠,并且干扰信号频率精度以及与雷达信号相干性都将降低。

5 结束语

本文设计的宽带DRFM干扰机信号处理模块采用正交双通道DRFM方式,可以实现1GHz的高瞬时带宽和8 bit的分辨率,存储深度可以达到2 048 μ s。而现常见报道的信道化DRFM设备,为达到对宽带信号的实时处理,其信道数量较多(4个以上),设备复杂度高,各通道器件的差异很容易导致通道间幅度、相位差异较大,最终合成的干扰信号与雷达信号相比有严重畸变,导致无法有效干扰雷达。而该模块可发射大时、频宽信号,可实现对各种新体制宽带雷达有效侦察、干扰。同时,该宽带DRFM干扰机具有的高速信号侦察能力、干扰的多样性和控制的灵活性,还可广泛应用于信号波形合成、威胁告警信号分选、电子情报信号分析等方面,有着广阔的应用前景。

[1]刘勇.基于DRFM的PD雷达干扰技术及其实现[D].长沙:国防科技大学,2006.

LIU Yong.Jamming Technique and Implementation for Countering PD Radar Based on DRFM[D].Changsha:National University of Defense Technology,2006.(in Chinese)

[2]杨会军,王根弟.基于DRFM的弹载自卫式单脉冲雷达干扰技术[J].航天电子对抗,2011,27(1):6-9.

YANG Hui-jun,WANG Gen-di.Missile-borne selfscreen jamming technique of mono-pulse radar based on DRFM[J].Aerospace Electronic Warfare,2011,27(1):6-9.(in Chinese)

[3]陈敬,谢启友,田晓波,等.基于固态存储技术的DRFM设计[J].现代电子技术,2011,34(8):154-156.

CHEN Jing,XIEQi-you,TIAN Xiao-bo,et al.DR FM Design BasedonSolid-stateMemory Technology[J].Modem Electronics Technique,2011,34(8):154-156.(in Chinese)

[4]赵书志,潘明海.基于FPGA的数字射频存储器设计[J].可编程器件应用,2007,30(2):118-120.

ZHAO Shu-zhi,PAN Ming-hai.Design of DRFM based on FPGA[J].Electronic Measurement Technology,2007,30(2):118-120.(in Chinese)

[5]陈勇,王冰,孙龙.一种数字射频存储器的设计[J].现代电子技术,2009,32(12):111-114.

CHEN Yong,WANG Bing,SUN Long.Design of Digital Radio Frequency Memory[J].Modem Electronics Technique,2009,32(12):111-114.(in Chinese)

[6]李勇.数字射频存储技术及其应用研究[D].武汉:武汉理工大学,2007.

LI Yong.Research on DR FM Technology and Its Application[D].Wuhan:WuhanUniversityofT echnology,2007.(in Chinese)

[7]孙国营,李云杰,高梅国,等.基于滤波器组的数字射频存储系统[J].北京理工大学学报,2011,31(11):1347-1350.

SUN Guo-ying,LI Yun-jie,GAO Mei-guo,et al.DRFM System Based on Analysis and Synthesis Filter Bank[J].Transactions of Beijing Institute of Technology,2011,31(11):1347-1350.(in Chinese)

YANG Chun was born in Chengdu,SichuanProvince,in 1976.He received the M.S.degree from University of Electronic Science and Technology of China in 2006.He is now an engineer.His research concerns radar signal processing.

Email:yangchun@swiet.com.cn,yc-mail@126.com

Design of Signal Processor for Wideband DRFM Radar Jammer

YANG Chun

(Southwest China Institute of Electronic Technology,Chengdu 610036,China)

The composition block diagram and signal processing flowchart of the signal processor for wideband digital RF memory(DRFM)jammer are provided.The key technology of realizing the processor module is described with focus on solution to parallel high-speed signal processing in FPGA.This module can give 1 GHz processing bandwidth and 2 048 μ s memory depth.It can jam new system wideband radar effectively and has wide applications.

radar jammer;DRFM;signal processing;high-speed transmission;parallel processing

TN957;TN972

A

10.3969/j.issn.1001-893x.2012.06.017

1001-893X(2012)06-0918-04

2012-02-09;

2012-05-22

杨 春(1976—),男,四川成都人,2006年于电子科技大学获硕士学位,现为工程师,主要研究方向为雷达信号处理。