基于EDMA的FPGA与DSP图像传输的设计与实现

2012-06-01张尧琴王玉凡

张尧琴,杭 娟,王玉凡

(西安电子科技大学电子工程学院,陕西西安 710071)

数字信号处理器(DSP)是采用数字计算方法对信号进行处理的专用芯片。由于其性能稳定,可大规模集成,编程性高和易实现等优点,被广泛应用。其中,以图像处理与DSP技术结合较为普遍,因为图像所包含的信息数据量大,而DSP的处理速度快,易于实现大量数据高速传输的特点能够满足这一要求。

目前,图像处理技术已在通信、信息、电子、航天及军事等领域得到广泛应用。与图像处理有关的系统设计中,FPGA加DSP构架是普遍的使用方法。为充分利用DSP的性能,需要在FPGA中对图像进行相应的预处理,再把图像数据传输给DSP进行处理。所以FPGA与DSP之间的数据传输技术变得不可或缺。

图像数据传输的速度与稳定性对整个系统的性能具有很大的影响。本文介绍了一种基于EDMA的高速稳定的数据传输方法,并在TI的DSP开发平台CCS下,对该方法的性能进行了测试。

1 方案设计

文中图像传输硬件系统结构如图1所示。该系统中采用 Altera公司的 Cyclone3系列 FPGA:EP3C80F484C6,Analog Device公司的视频解码芯片ADV7183,差分输入14位数据的LVDS接口和TI公司的TMS320C6416。该系统既可采集模拟视频信号,又可采集数字视频信号。模拟信号经过模数转换芯片ADV7183后变成数字信号,数字信号经由LVDS差分接口进入FPGA。为调试方便,模拟图像与数字图像统一使用320×256规格。DSP以EDMA方式接收,经过FPGA预处理后的图像数据,在CCS平台下进行显示以验证传输的正确性。

图1 系统设计框图

2 接口电路设计

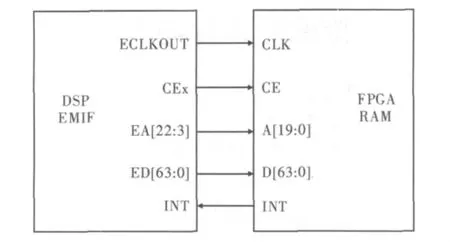

DSP以EDMA方式从 FPGA中读取数据,需要FPGA在内部配置一块大小适当的存储空间。FPGA作为一个存储器,通过DSP的外部存储器接口(EMIF)与DSP相连。硬件连接如图2所示。

图2所示为FPGA与DSP的硬件上连接示意图。实际使用时,并没有使用上述所有信号线。FPGA使用到的管脚如下:CLK,CE,A[19:0],D[63:0]和 INT。CLK是DSP提供的同步读写时钟,CE是DSP的片选信号,A[19:0]为地址线,D[63:0]地址线。INT 为中断信号。

图2 接口示意图

FPGA与DSP的传输机制:FPGA使用QuartusII开发平台往双口RAM中写数,写满后用中断管脚INT来通知DSP读数。DSP收到FPGA的中断信号后,开始读数。读数期间片选信号CE有效,FPGA把DSP片选信号CE作为双口RAM的读使能,在使能期间用DSP提供的时钟CLK读取数据。

系统中DSP提供给FPGA的时钟CLK为100 MHz。接收模拟图像时,图像数据为8位,只使用D[7:0]8根数据线;接收数字图像时,图像数据为14位,使用D[15:0]16根数据线,高两位置0。数字图像与模拟图像均为320×256。

3EDMA传输

TMS320C6000系列DSP中的,增强型直接存储器访问(EDMA)控制器执行所有二级高速缓存/内存控制器与外设之间的数据传输。

EDMA控制器包括事件和中断处理寄存器、事件编码器、参数RAM和地址产生硬件电路。事件是触发EDMA启动的同步信号,事件寄存器用于捕获EDMA事件。事件编码器解决多个事件发生时事件的优先级问题。对应事件的传输参数存储在EDMA参数RAM中,并且传递给地址产生硬件单元,进行寻址EMIF或外设执行相应的读写操作[1]。

3.1 传输流程

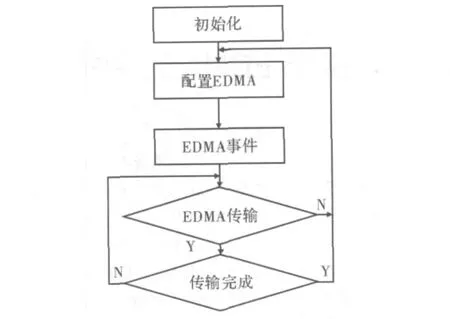

使用EDMA数据传输的方法有两种,一种是CPU初始化的EDMA;第二种是事件触发的EDMA。所有的EDMA通道都有一个特定的同步事件与之对应,如外围设备事件、外部硬件中断或EDMA传输完成事件都可以同步触发EDMA的传输。当通道对应的同步事件发生或由CPU同步该通道时,通道就完成一次数据传输请求。由事件触发的EDMA传输实时性好,是一种常见的传输方式。系统采用的就是事件触发模式,触发信号就是FPGA给DSP的中断信号[2]。图3为EDMA的传输流程。

图3 EDMA传输流程

3.2 EDMA配置

同步事件发生时,EDMA传输的数据大小和源目的地址由参数RAM中的参数决定。访问EDMA的参数RAM时需要通过外围总线。EDMA传输参数,如图 4所示[3-4]。

图4 EDMA传输参数

选项(OPT)部分主要用于传输数据的最小单元、数据传输的源地址和目的地址的寻址模式。系统中的最小传输单元为1 Byte,源地址设置为一维源,目的地址设置为二维源。数据传输模式为帧同步。传输数据块的行数设置255(实际传输行数为256),列数设置为320。

源地址(SRC)设置了源数据所在的地址,系统该参数配置为0xA0000000,指向FPGA目的地址(DST)设置了数据要被传输到的存储空间的地址。

实现传输过程为把一幅320×256 Byte的图像从FPGA缓存到了SDRAM中。传输14位的数字图像时,一个像素的图像数据占用2 Byte,所以要把选项(OPT)中的最小传输单元改为2 Byte。

3.3 程序实现

相应的EDMA通道初始化完成后,使能并打开相应的中断。FPGA每产生一次EDMA同步事件,即往INT管脚发一次中断信号,EDMA就能完成一次指定要求的传输,然后等待下一次同步事件。

4 实验结果

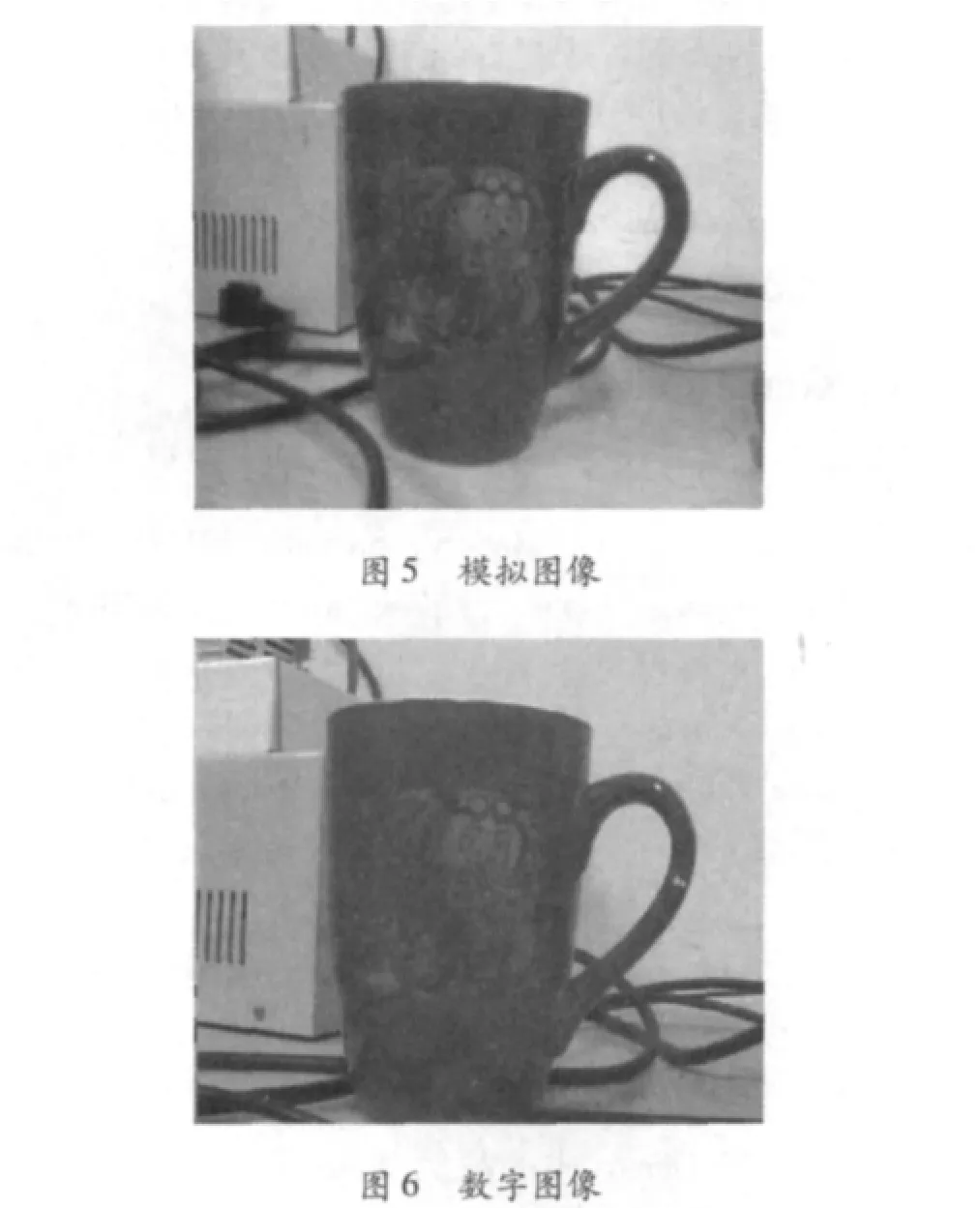

DSP提供给FPGA的时钟为100 MHz,传输一幅320×256的图像需要约为0.8 ms。传输速度较快,可以满足图像快速传输以及实时处理的要求。TI的开发平台CCS可以观察存储器中的数据,并把收到的存在存储器中的数据显示成图像,从而可以验证传输的正确性以及稳定性。数据源为模拟图像时,相机拍摄的原始图像和DSP收到的图像如图5和图6所示。

数据源为数字信号时,原始图像为14位数据,TI的仿真平台只能显示8位图像,所以DSP中收到的图像数据只能以高8位进行显示,但会丢掉图像的一些细节,图像整体偏暗。由于系统采用的数字图像由中波红外热像仪采集,由于视场差别,原始图像无法采集。图7为提取高8位图像数据显示的图像。

图7 数字图像

图5~图7中的图像经过多次传输验证,没有出现错误的图像。说明该系统实现的图像数据传输满足图像实时处理的速度要求以及可靠性要求。

5 结束语

介绍了一种FPGA向DSP的数据传输方法,描述了EDMA的特点以及由其控制的数据传输的实现过程。所介绍的方法在开发的实验平台上,进行了验证。文中介绍了FPGA向DSP的传输,更改EDMA的源地址与目的地址及相关参数可以实现DSP向FPGA的数据传输。

[1]卞红雨,纪祥春,乔钢,等.Texas Instruments Incorporated,TMS320C6000系列DSP的CPU与外设[M].北京:清华大学出版社,2007.

[2]田黎育,何佩琨,朱梦宇.Texas Instruments Incorporated,TMS320C6000系列DSP编程工具与指南[M].北京:清华大学出版社,2007.

[3]刘嵩,喻胜辉,刘海华,等.基于EDMA的多通道数据传输的实现[J].计算机测量与控制,2009,17(7):1429 -1434.

[4]贾龙,林研.基于DSP和FPGA的高速数据采集系统的设计与实现[J].电子测量技术,2007,30(5):95 -97.

[5]郭霞,杨涛,张浩.高速数据采集系统的信号完整性分析[J].电子科技,2008,21(1):35-37.