一种叠孔三阶HDI板制作技术研究

2012-05-31陈世金乔鹏程

陈世金 罗 旭 覃 新 乔鹏程 徐 缓

博敏电子股份有限公司

1 前言

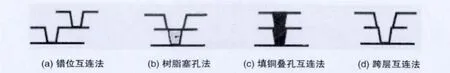

随着3G、智能手机和平板电脑等消费类电子产品的飞速发展,推动PCB技术不断向更高布线密度方向发展,同时也要求PCB设计具有小型化、轻薄化和高可靠性等。因此,传统的盲孔设计(交错孔、跨层等)已无法满足要求,其局限性主要表现在空间节约、制作难度和可靠性等方面,唯有叠孔设计可满足要求。实现盲孔与盲孔的互连方法主要有四种(如图1),随着电子产品对PCB可靠性要求的提高,当前使用最多的是第三种设计(填铜叠孔互连法)。其制作方法是:次外层盲孔制作时,把该孔直接用电镀铜填满,再压合激光下一层,层层叠加,实现层间互连。电镀填孔互连法既可减少工艺流程,也能确保更高的可靠性和更优良的电气性能。因此,电镀塞孔法是比较理想的盲孔堆叠制作方法,为现行业最常用的电镀填孔互连法[1 ]。

本文将以一款叠孔三阶10层的HDI板为例,讲述其制作难点和解决方法,突出其制作的控制重点和注意事项等,为业界工作者制作该类叠孔设计的HDI板提供一定的参考。

图1 多阶盲孔实现层与层互连方式

2 技术原理

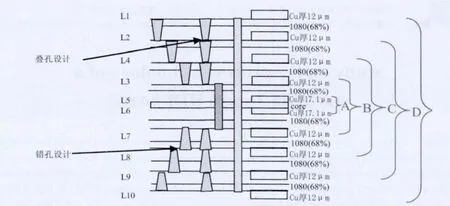

叠孔三阶HDI板的其技术原理主要是采用盲孔与盲孔堆叠的方式来实现层与层之间的导通和互连,重点是叠孔堆叠重合性(层间对准度)和互连可靠性的控制。以一款叠孔三阶HDI板为例看一下该类板的叠合结构图(如图2):

图2 叠孔设计的三阶10层HDI板

2.1 层间盲孔堆叠技术

在前言部分我们已经谈到了层间堆叠技术的几种方法,就当前的主流层间堆叠技术来看,填铜叠孔设计具有高可靠性、高布线密度等优点,也有研究表明提高印制板布线密度最有效的方法之一是减少通孔数增加盲孔数[2]。而采用填铜技术除了具有高可靠性优点外,还可在流程上得到简化,总体核算成本具有一定的优势。因此,该类设计攻破了成本与性能的难题,是当前PCB技术最佳的互连设计方法。该设计所带来的难点是如何保证层与层间的对位精准度,解决好该项难点将成为我们掌握叠孔设计三阶或多阶、甚至是Any-layer HDI技术的关键所在。

2.2 电镀盲填孔技术

该项技术的另一个难点是电镀填孔技术,填孔效果的好坏直接决定互连可靠性的成败,如dimple(凹陷度)、filling power(填充率)和面铜厚度的控制等。图3是我们对填孔效果的控制主要表征[3]。

图3 填孔能力表征示意图

由于涉及到精细线路的制作,我们还需要对填铜后的面铜进行控制,如设计线路为75 μm/75 μm线时,需要将面铜厚度控制在30 μm以内,以保证蚀刻工序能够顺利制作。否则,如填铜后的面铜厚度过厚则需要减铜或树脂磨板等,对成本是一种浪费,同时也不利于涨缩的管控。

3 制作设计

3.1 工艺流程

根据我技术中心研发人员对此项目的研究和探讨,结合实际生产制作和现有成熟的工艺技术,最终制定该叠孔三阶HDI板的工艺流程如下:

芯板(L5-L6)下料→内层线路制作→内层蚀刻、AOI→棕化、压合→铣边、减铜(L4-L7)→钻埋孔→沉铜、板电→线路制作→蚀刻、AOI→棕化、压合→铣边(L3-L8)→减铜、棕化→激光→沉铜、填孔电镀→线路制作→蚀刻、AOI→棕化、压合→铣边(L2-L9)→减铜、棕化→激光→沉铜、填孔电镀→线路制作→蚀刻、AOI→棕化、压合→铣边(外层)→减铜、棕化→激光→钻通孔→沉铜、填孔电镀→线路制作→蚀刻、AOI→阻抗测试→阻焊、文字→印选化→沉镍金→退选化→电铣成型→FQC→OSP→二次FQC→FQA→包装→入库

3.2 材料的选择

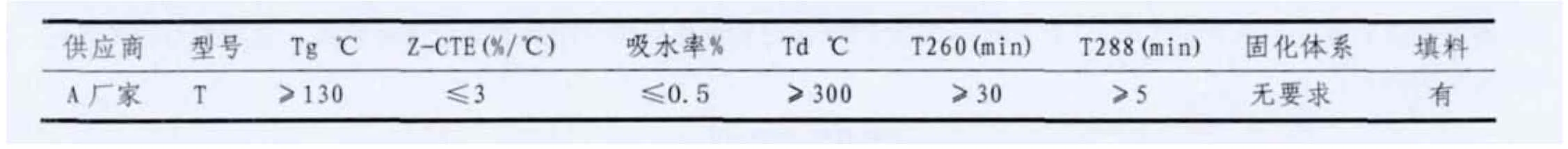

在材料的选择上,我们一方面要考虑其稳定性,如低CTE(热膨胀系数)、低吸水率和高耐热性等。另一方面要考虑对该类板材制作技术的成熟性,即选择已经多次使用,并完全掌握其加工特性的板材,同时,也兼顾成本考虑。该板材所需具备的特性要求如表1所示。

表1 使用基板材料的主要性能

板材的稳定性对我们的涨缩控制极为有利,而选择多次使用、掌握其加工特点的板材对提升我们的合格率有很大的帮助,对重点管控项目可做针对性地跟进和控制。基于以上两个控制因素的考虑,我们选择了A厂家的T型号板材(以及相匹配的pp材料)。

4 制作技术研究

针对该类叠孔三阶HDI板的制作难点,主要涉及到精细线路制作技术、层间对位精度控制技术和填孔电镀技术,下面将就这三个方面做相关讲述。

4.1 精细线路制作技术

在制作精细线路时,常见制作难点及问题频发点有:

(1)线宽补偿设计问题;

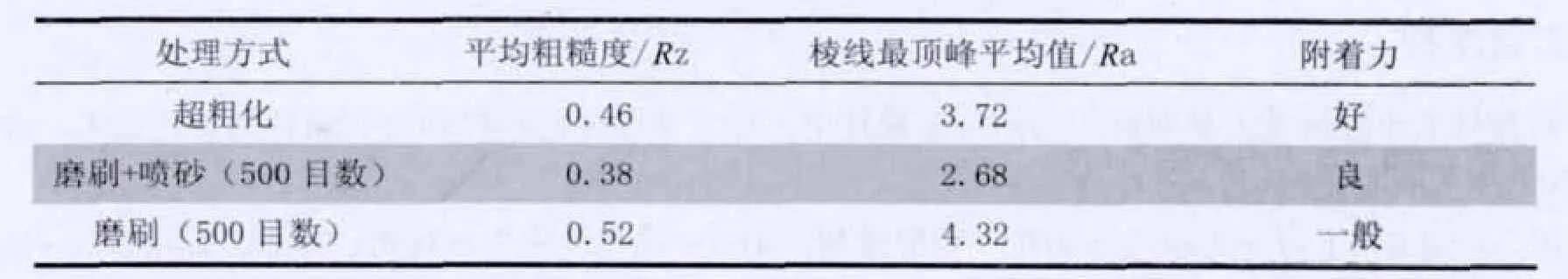

表2 几种前处理方式粗糙度和附着力对比

(2)板面粗糙度对附着力的影响;

(3)贴膜、曝光、显影条件对开短路的影响;

(4)蚀刻条件(喷淋压力、蚀刻因子等)对蚀刻效果的影响;

(5)面铜厚度及干膜厚度对精细线路制作的影响。

针对以上问题,对其成因机理进行分析,并提出相应解决方案:

(1)线宽的补偿按照相关的设计准则来执行,但针对特殊精细线路(如L/S≤3 mil),须实行特殊补偿和分段补偿,以保证L/S≤75 μm类线宽补偿5.1 μm ~ 12.7 μm,最小线距为63.5 μm。根据之前补偿设计实验结论和经验总结,可保证该款板的图形形成条件。

(2)板面粗糙度对附着力的影响可分几组对比试验进行,如超粗化、磨刷+喷砂、磨刷等,然后通过表观检查(SEM扫描电镜)和表面粗糙度检测等手段[4],干膜结合力测试原理与国际通用规范IPC-TM-650中之阻焊油墨相关规定结合力测试相同,可对比出哪种前处理效果最优,粗糙度在多少的范围内可保证干膜与铜面有良好的结合力。表2为几种前处理方式粗糙度及结合力测试情况:

对于精细线路的制作,不是说粗糙度越大就结合力越好,一般是需要根据实际测试情况来确定的。通常来说,单采用磨刷的方式来处理铜面,会出现定向的擦伤,有耕地式的沟槽、铜面划痕,严重时会出现铜被翻起,不适合精细线路的制作。而单采用超粗化(微蚀)的方式,不能保证铜面胶渍、油污、铜瘤和凹痕等缺陷的处理,采用磨刷加喷砂的方式则可保证对以上缺陷的修复。

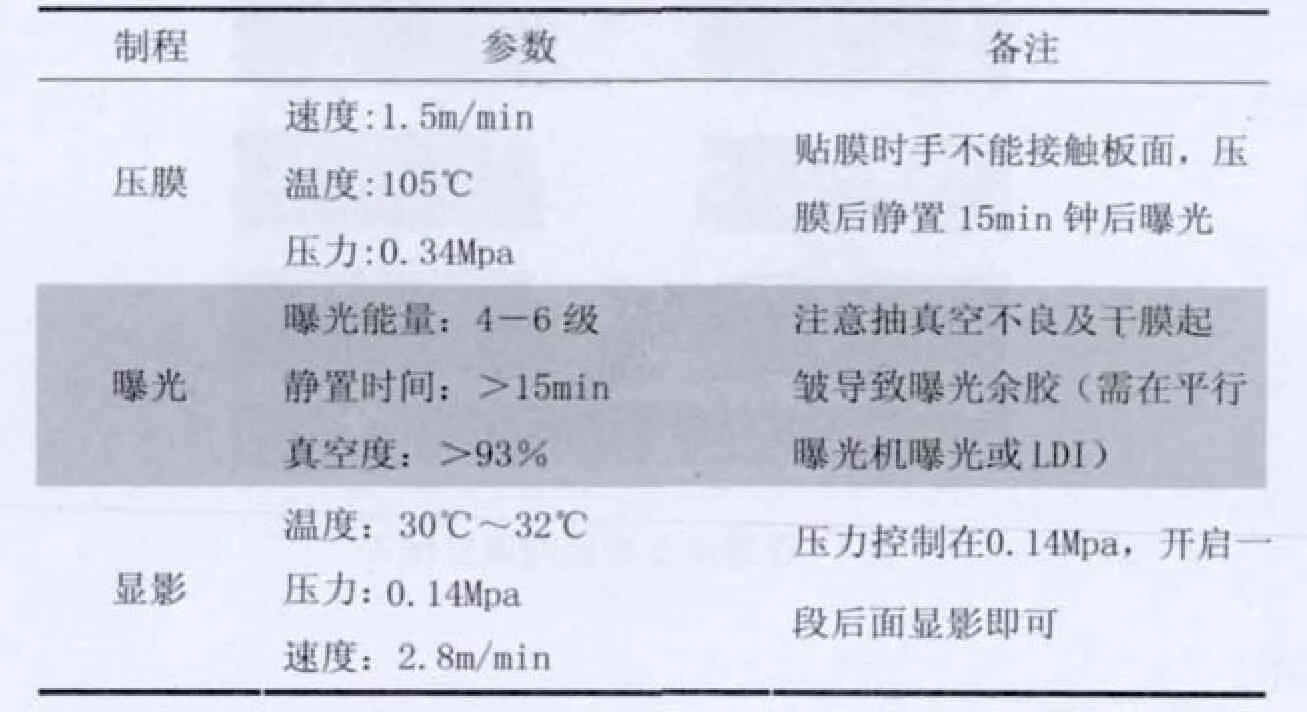

(3)贴膜、曝光、显影条件的设定是需要根据干膜的类型、线路/线距的等级和设备等具体情况确定的。对于精细线路来说,干膜厚度较低,其解像度就越高,合适的干膜厚度是保证精细线路制作的要素之一,曝光时选择合适的光源形式,尤其是对高密度、精细导线的图形的光成像,光源的特性直接影响曝光质量和效率。目前干膜的吸收光波长为325 nm ~ 365 nm,较短的波长的光曝光后成像图形的边缘清晰整齐。光能量与光波长的关系式如下:

式中:ε——光能量;h——布郎光常数;r——光的频率;c——光速;λ——波长。

从式中可以看出,光的波长越短,其能量也就越大,所以大多数曝光机都是采用波长在320 nm ~ 400 nm之间。从光源发散形式来说,平行光照度均匀,不易失真,其成像分辨率更高,更有利于精细线路的制作。曝光能量的控制也是一个重要因素,采用25 μm的干膜能量控制在40 mJ/cm2~ 50 mJ/cm2,曝光尺约4-6格较为合适。根据膜分辨率的实际,掌握适当的显影速度,使细线条能均匀的齐正。精细线条的显影速度在正常工艺规范内,一般要比粗线条的要快一些,以便使露铜的两边膜壁少受显影液的攻击造成导线变形失真或者附着力下降;但若线距也同时较小,则要兼顾到小线路图形的显影速度要稍微放慢的情况,二者要根据实验综合考虑。其具体制作参数如表3所示:

表3 贴膜、曝光和显影制作参数

(4)蚀刻条件(喷淋压力、蚀刻因子等)对蚀刻效果的影响,主要需要控制好蚀刻药水参数(浓度、温度等)、喷淋压力及蚀刻均匀性等。控制二价铜的含量,它是蚀刻铜的主剂,可以加快蚀刻速度,以减少侧蚀发生的机会,使化学反应处于稳定状态,对精细导线的蚀刻至关重要。为确保数据变化在规定的范围内,就需要严格控制蚀刻液的比重、补充液的均匀流量和基板在蚀刻机内的运送速度等。对于精细线路的制作,最重要的是要考虑如何保证密集线路区域的药水交换,对喷嘴交叠的角度、重合情况,上下喷淋压力,放板方式、位置等都有一定的要求,这些都直接关系到最终的蚀刻效果。

(5)面铜厚度和干膜厚度对精细线路的影响,这一点根据蚀刻线的能力可以计算出最大面铜厚度的控制上限,干膜的厚度越薄是越有利于精细线路的制作的。这在之前做过较多的试验,在此不再作赘述。

4.2 层间对位精度控制技术

要做好HDI板层间对准度控制的精确性,首先要搞清楚导致HDI板对准度偏差的制成因素。以靶标为参考点,HDI产品的对准度偏差主要可以分为内层图形和盲孔之间的偏差、内层图形与通孔之间的偏差、外层图形与盲孔的偏差和外层图形与通孔的偏差,即导致HDI对位偏差的因素很多[5]。

(1)层压板偏差。该类HDI板都是经过逐次层压而成,在日本也称之为积层板(BUM板),在经过多次压合后,板材必然会出现一定的收缩,而每次收缩又会存在一定的差异,故就会出现尺寸偏差。而选择高Tg材料的基板会有利于这方面的控制,另外,在压合程式或参数上进行一定的优化和控制,对改善不规则性变形引起的层偏会起到一定的改善效果。

(2)X-Ray打靶偏差。因为涉及到打靶定位问题,打靶的精确度应控制在±15μm以内,而X-Ray打靶的钻咀也应保持一定的锋利,避免产生披锋,引起孔型的变化。

(3)激光钻孔的偏差。激光钻孔机本身存在一定的精确度,一般在±7.5μm,激光钻孔时一般采用抓双靶标的方式来定位,即通孔、盲孔都抓,这类情况引起的偏差几率相对较小。

(4)菲林涨缩、曝光对位偏差等。如不采用LDI来制作,则需要考虑菲林的变形或涨缩问题,多因室内温湿度控制不好引起,有时候也会存在光绘机绘出的底片与设计存在一定的差异引起。曝光对位精度由设备的类型、性能等决定的,图形对孔位对位控制范围一般控制在±50μm,而要是精细线路则设定范围就应该更小一些。

(5)树脂磨板引起涨缩偏差。针对这一点除了保证树脂研磨时方向、次数作特别管控外,对参数的设定、研磨方式等也要做相关控制,否则,极易引起同批板出现不同涨缩的情况。但是,我们还是要尽量做到面铜控制在蚀刻能力范围内,减少树脂磨板加工。

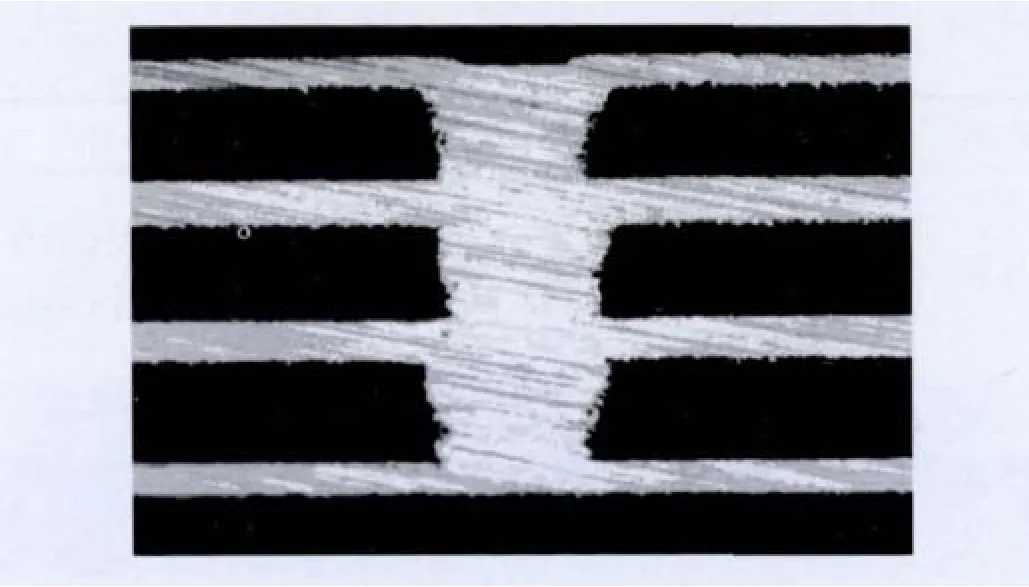

其实,层间对位精准度的控制所涉及的方面是很多的,要做到层间精准度的控制,除了对以上几个方面进行控制外,还要从靶标的设计、对位方式的选择和工艺流程的优化等方面着手,对其造成影响的每一个因素都要进行排除。图4为我们最终获得的层间对位效果盲孔堆叠图片。

图4 最终成品层间对准度情况

4.3 填孔电镀技术

关于填孔电镀的原理在行业内有较多相关的介绍[6-10],在此就不做讲述。笔者将主要对填孔电镀的控制项目进行相关讲解。

(1)流程的选择。填孔电镀一般有闪镀和不闪镀两种流程选择方式,至于是选择哪种流程都需要根据实际情况来定。如果是小批量的板子,可考虑直接填孔电镀,重要的是保证停放时间尽量短,一般控制在2小时内完成。而如果是大批量的板子,同时药水性能不是很优良的情况下,则最好选择闪镀流程,有利于品质管控。流程选择不当或过程控制不严,极有可能引起填孔效果的不良,如出现dimple过大等问题。

(2)dimple和filling power的控制。对于这方面的控制主要从药液的管控和电镀参数的设定来控制,通常来说,填孔电镀的药液管控要求要较常规的电镀药液要严格许多,如浓度、温度的控制等。市面上填孔添加剂的种类也是比较多的,我们需要选择操作条件相对较宽、性能较优的添加剂,可以通过多次对比试验来进行选择。药液的浓度、温度需要进行严格管控,最好设置有自动添加、温控等控制系统,以确保人为操作引起的失误。电镀参数的设定对电镀填孔效果的影响是相当大的,选择怎么样的电镀参数,既能保证良好的填孔效果,有能最大程度的节省时间和节约成本?这是我们需要考虑的问题,也需要我们在制作过程中不断总结经验,使我们的参数设定趋于合理化、科学化,达到最好的填孔效果。

(3)面铜厚度的控制。为什么在这里要提到面铜的控制?这是由于涉及到精细线路的制作问题,在电镀填盲孔的时候必须对此进行控制。否则,如果只追求填孔效果(filling power)的控制,不考虑后工序的制作顺利,那就不能保证此板的品质和最终合格率。对于面铜厚度的控制,要控制好药水参数,保证填孔效果的前提下,尽量将面铜厚度控制的最薄。面铜厚度的控制也是与药水性能和电镀参数的设定有很大的关系,在这里就不再赘述。

(4)其它方面。要得到好的填孔效果,除了以上控制要求外,还需要对激光盲孔的孔型、孔径等进行控制。盲孔的孔型包括over hang 、under cut和孔壁质量等,如over hang需单边控制在10μm以内,盲孔孔型呈倒梯形,不能出现腰鼓形、孔壁粗糙度过大等。要得到完好的成孔效果,一方面要从材料的选择入手,基板对电镀填孔的影响也是不可忽视的,介质层材料对填孔有影响这是十分显见的。另一方面要从激光钻孔的参数进行改善或优化,使用何种材质的介电层、厚度等对钻孔孔径的影响是比较大的,需要结合实际试验情况来确定合适的激光参数。

5 成品可靠性测试

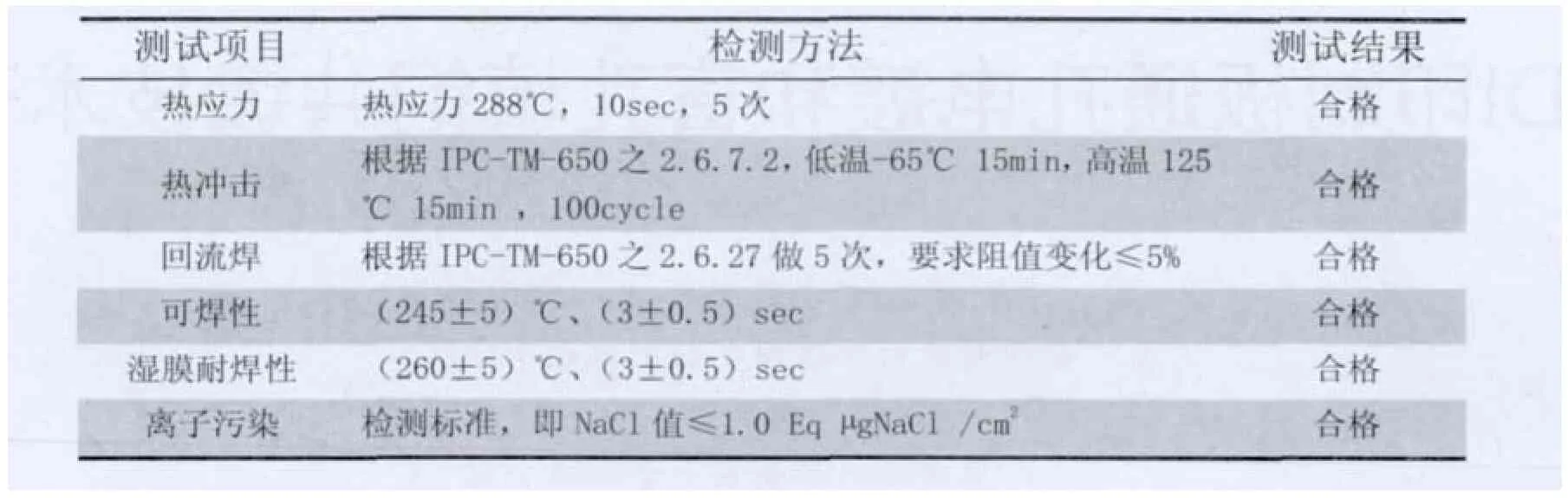

依照上述解决方案,生产的成品整板外观平整,检测弓曲度、扭曲量均满足IPC-600H标准,切片确认孔壁、面铜、层间介电层厚度等符合MI要求,热应力测试无分层、爆板、绿油气泡等不良问题出现。具体可靠性测试结果可参见表4。

表4 成品可靠性测试结果

6 结语

随着PCB技术的飞速发展,对叠孔多阶HDI板的制作要求将会越来越严,为我们提出了更多新的挑战。该类叠孔HDI板的制作关键技术仍然是层间对位精准度、精细线路和电镀填孔等方面,要使我们对该类板制作技术达到成熟化,这需要我们今后的工作中不断深入,不断总结经验、积累成果,逐渐提高我们制作叠孔多阶HDI板的工艺水平。

[1]陈世金. 填铜叠孔二阶HDI工艺技术的研究[J]. 印制电路资讯, 2012.03:107-111.

[2]杨宏强, 王洪, 骆玉祥. 多阶盲孔板制作中的关键技术研究[J]. 印制电路资讯, 2007.05:72-75.

[3]叶成镜,蓝国兴,电镀铜填孔技术之探讨[J]. 电路板会刊 第19期:53-59.

[4]白蓉生. 表面粗糙度[J]. 印制电路资讯, 2003.04:42-50.

[5]夏智, 汤攀, 于湛. HDI对准度研究[J]. 印制电路信息, 2009.S1:55-64.

[6]Barthelmes,Dr.J.,Acid Copper Plating with Insoluble Anoele-A Novel Technology in PCB Manufacturing[J]. Proceedings of the Electronics circuits word convention 8.Tokyo.september7-10.1999.

[7]Kobayashi T , Kaw asaki J , Mihara K, etal. Via2fill2ing using electroplating for build2up PCB[J]. Elec2t rochim. Acta,2001,47: 852-859.

[8]李亚冰, 王双元, 王为. 印制线路板微孔镀铜研究现状[J]. 电镀与精饰, 2007.01:32-35.

[9]Jun J N, O h S C. A study on the development of co l2o ring stainless steel (electrolytic method)[J]. Yongu Pogo2Kungnip Kisulwon (Ko rean), 1993,4(3).

[10]C.Q.Cui and Kelvin ,Cu Fully Filled UItra-Fine Blind Via ON Flexible Substrate for High Density Interconnect,International Electronic Manufacturing Technology, 2006.pp18.