LTE/GSM 多模基站收发信台数字中频模块故障诊断的新方法

2012-03-18徐婷婷王小港

徐婷婷,王小港,郭 亮

(上海贝尔股份有限公司,上海201206)

1 引 言

3GPP 长期演进(LTE)项目是近两年来3GPP 启动的最大的新技术研发项目,这种以OFDM/FDMA 为核心的技术可以被看作“准4G”技术。LTE 技术可以提供高于3G 速率几十倍、接续时延更短的无线业务体验,实现上/下行分别超过50 Mbit/s和100 Mbit/s的传输速率和更好的端到端质量保障[1-2]。今天,有超过49 个LTE 网络已经开始商业运营在全球各个国家,有超过269 款LTE 终端由各个厂商发布面市。可以看到,LTE 的全球化发展已是大势所趋。业界各通信设备厂商都纷纷抓住网络技术更新换代这一大好机遇,加快技术创新步伐,提高市场开拓能力,力求在LTE 时代占有自己的一席之地。

另一个无线技术发展的热点就是软件无线电(Software Defined Radio,SDR)。软件无线电就是宽带模数及数模变换器(A/D 及D/A)、大量专用/通用处理器、数字信号处理器(Digital Signal Processor,DSP)构成尽可能靠近射频天线的一个硬件平台。在硬件平台上尽量利用软件技术来实现无线电的各种功能模块并将功能模块按需要组合成无线电系统。该平台架构被广泛应用于BTS 的开发中,便于BTS 的升级和更新换代,特别适用于多种标准共存的情况下。LTE/GSM 多模BTS 正是在这样的背景及基础上,通过对原来GSM BTS 的升级应运而生的。其中,数字中频模块是在FPGA 芯片实现的。FPGA 以高速复杂逻辑处理能力见长,同时凭借其超大规模的单芯片容量和硬件电路的高速并行运算能力,在信号处理方面也显示出优势。数字中频模块的升级,主要是由原来支持6 路GSM 载波升级到支持1 路LTE载波加2 路GSM 载波。

FPGA 的故障诊断在整个FPGA 的开发过程中是重点和难点。目前,FPGA 开发过程中的诊断手段主要是前期的RTL 代码仿真,而上板测试阶段主要有3 种方法:利用主控CPU 读取FPGA 寄存器的状态值或修改寄存器的配置值;利用FPGA 厂商提供的嵌入式逻辑分析仪添加需要观测的信号;利用外接引脚连接逻辑分析仪观测相应引脚的信号。这3种方法要依赖于CPU 软件或外部接口,在系统测试阶段都不够灵活, 并且不能实现大块数据的采集。而本文提出的基于以太网接口采用Matlab 软件实现的软硬件协处理诊断技术, 由于利用了板上的DDR2 存储器,因此只需要编写简单的Matlab 脚本语言,利用一个以太网接口,就可以实现FPGA 内部寄存器的存取及信号链路各节点大块数据的采集。相比其他的诊断方法,该方法只需要一个以太网接口,实现方式简单灵活。

2 FPGA 数字中频模块

2.1 模块功能

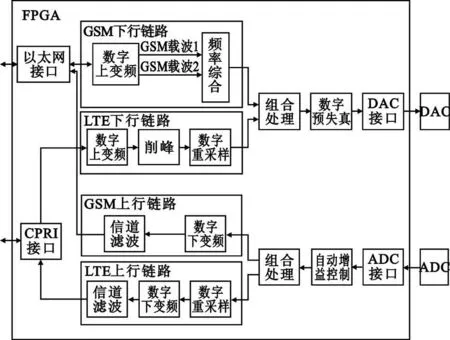

在LTE/GSM BTS 中,FPGA 实现的数字中频模块支持GSM 和FDD LTE 两种协议,其实现结构如图1 所示,其中既包含两种协议数字中频的独立处理链路,也包含公共的组合处理链路[3-4]。

图1 LTE/GSM BTS 数字中频功能结构图Fig.1 Function structure of digital IF modu le in LTE/GSM BTS

从图1 中可以看到,GSM 下行链路主要包括数字上变频和2 路载波的频率综合,而LTE 主要包括数字上变频、削峰及数字重采样,两者在相同的采样频率下合并进入组合处理模块,再进行数字预失真处理,最后经DAC 接口模块输出到DAC。其中GSM的基带数据来自以太网接口,LTE 的基带数据来自CPRI(Common Public Radio Interface)接口。

上行链路的处理则是从模拟端ADC 进入ADC接口,经自动增益控制模块,再到组合处理模块,组合处理根据不同的频点偏移,分别提取出2 路GSM载波和1 路LTE 载波。GSM 的上行处理主要是数字下变频、信道滤波及以太网接口部分,LTE 的上行处理主要是数字重采样、数字下变频、信道滤波及CPRI 接口。

数字中频模块包含了大量的数字信号处理,本文提出的诊断方法是利用Matlab 工具软件来存取寄存器及采集大块数据,而Matlab 的一大优势就是数字信号处理,因此,利用该方法采集到的数据可以直接在Matlab 工具环境里利用Matlab 丰富的信号处理函数进行分析处理。

2.2 FPGA 接口环境

在LTE/GSM BTS 系统中, FPGA 实际充当了DSP 的协处理器的角色(即DSP 为主控CPU),FPGA几乎与板上不同接口标准的其他芯片都有接口,除了实现数字中频这个主要功能,DSP 还通过FPGA控制其他芯片。FPGA 与DSP 的接口是通过以太网交换芯片。DSP 要实现各种不同的功能,如控制指令或基带数据的发送和接收,其与FPGA 之间的通信交互都是通过以太网包的形式进行的。不同的应用,需要定义不同类型的以太网包。在这样的设计基础上,本文提出了一种软硬件协处理诊断方法,该方法基于协处理协议自定义了一种特殊的以太网包类型,对于这一类型的以太网包,Matlab 可以接替DSP 的角色,直接实现与FPGA 的通信交互。

图2 FPGA 与板上其他器件的接口Fig.2 Interfaces between FPGA and other devices

3 协处理的原理与实现

3.1 协处理协议介绍

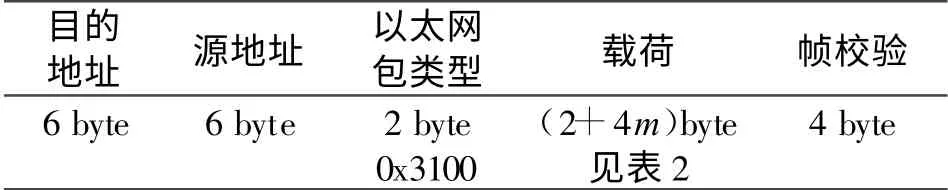

基于Ethernet 的软硬件协处理协议,简称为Co-simulation 协议, 为点对点通信, Xilinx 的System generator 工具可支持并可集成到Matlab 软件。表1所示为一典型的以太网帧结构,对于Co-simulation协议,会针对不同的命令和响应对以太网类型字段和载荷字段进行进一步的自定义[5]。为了将Co -simulation 协议的数据与其他业务的以太网包相区分,根据协议,本文定义了0x3100 的以太网包类型。

表1 以太网帧结构Table 1 Ethernet II frame

载荷字段的定义包含了Co-simu lation 协议标志符和协议数据两部分, 如表2 所示。由于FPGA硬件协处理接口的数据位宽为32 bit,因此协议数据的长度总是4 byte的整数倍。Co-simulation 协议标志符指示了协议数据的类型,本设计中用0xABCD指示该0x3100 包为Co-simulation 命令或Co-simulation 响应。主处理器通过硬件协处理接口发送命令包给FPGA,让FPGA 执行一系列相应的命令。同时FPGA 也可以通过硬件协处理接口回送响应包给主处理器。

表2 以太网载荷的定义Table 2 Ethernet payload

主处理器根据协议配置好相应的数据,就可以对FPGA 内相应的地址映射空间发起读写命令进行存取操作。一个0x3100 命令包可以包含多条读写指令。FPGA 内的硬件协处理接口会按次序顺序执行接收到的指令。

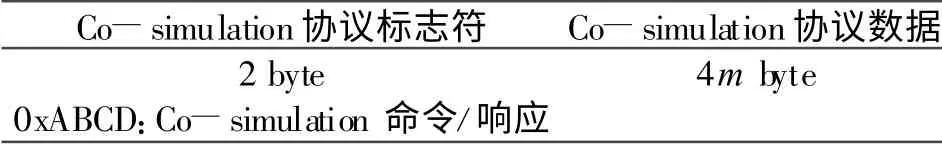

3.2 Co-simulation 协议的FPGA 实现

对于协处理的诊断方法,Co -simulation 协议的FPGA 实现是重点。在本文的FPGA 设计中,需要在以太网接口模块完成该功能。以太网接口模块负责处理CPU 通过以太网包对FPGA 的读写操作,以及业务数据的发送和接收。该模块的更新设计中,Co-simulation 协议部分采用了Xilinx 提供的IP 核,所有的存取操作都是通过地址映射进行的。对于业务数据的处理,在模块内部还需经过FIFO 来实现时钟域的转换。其中,FPGA 发送业务数据到CPU 的过程是由FPGA 自主发起的,无需CPU 发起读请求。

以太网接口模块通过SGMII-1 接口与板上的以太网交换芯片相连,通过local link 接口与FPGA内部的其他模块相连。从图3 中,我们看到有一路数据经local link 到Co-simulation Processor,再到地址映射模块。类型为0x3100 的包走的就是该数据路径。在本文所述的协处理诊断方法中,Matlab 代替CPU 与地址映射模块交互。在该诊断方法中,FPGA 将为相应的主处理器开放整块的地址映射空间,供主处理器进行读写操作,此时,Matlab 对该映射空间的操作将没有任何限制。

图3 以太网接口模块框图Fig.3 Ethernet co-simulation module diagram

4 诊断方法所需的其他模块

4.1 Ethernet 地址映射模块

从图3 中,我们看到所有从Co-simulation 处理器上传和下发的数据都是通过地址映射模块再到FPGA 内部的各个模块的。在BTS 系统中,DSP 与FPGA 的数据交互都是通过以太网包,因此,在FPGA设计之初,为FPGA 内部的各个功能模块都定义了相应的地址映射空间,为所有需要直接存取访问的寄存器都分配了相应的地址空间。通过协处理的诊断方法,我们可以对一个模块的整块地址空间进行存取操作。

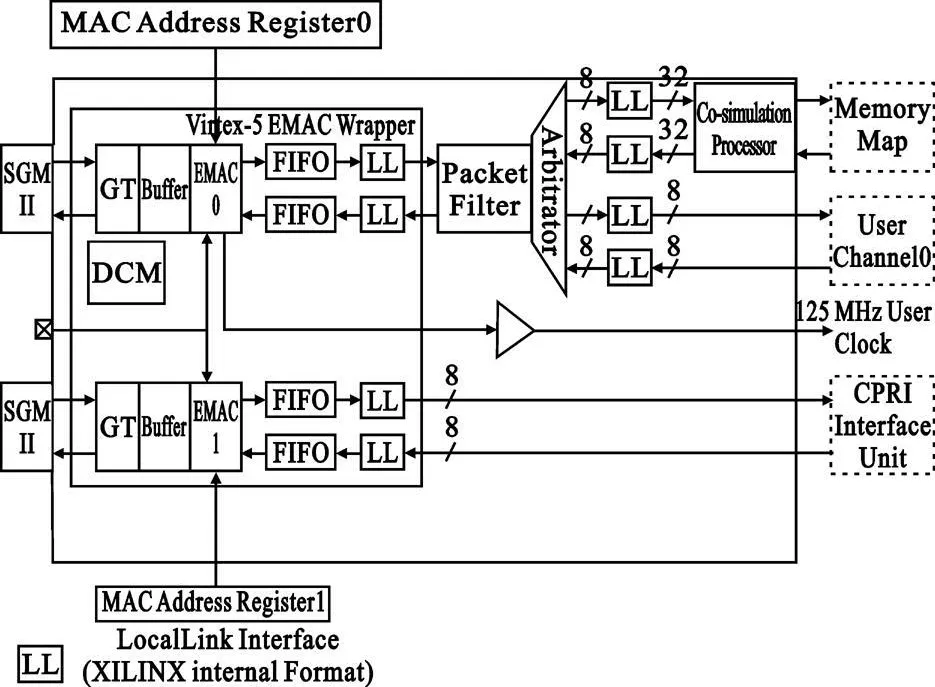

4.2 数据采集模块

协处理诊断方法的另一特点就是大块数据的采集,这就需要数据采集模块的开发。该模块完成了对FPGA 实现的中频处理模块内部某些关键节点的数据进行采集。

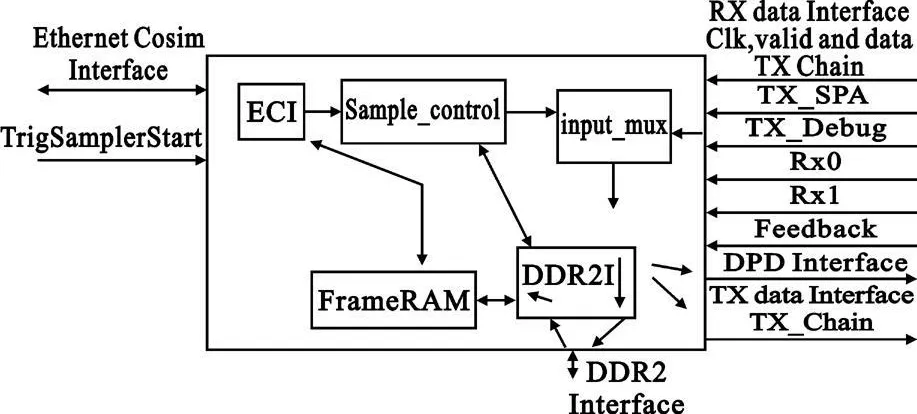

图4 数据采集模块框图Fig.4 Sampler module diagram

从图4 可以看出,数据采集模块包含发送和接收数据两部分功能。首先,接收功能包括采集TXpath、RX ADC 及FB ADC 3 个节点的信号。模块工作时,节点的选择是通过配置source-select 寄存器,采集数据的长度再通过配置长度寄存器。采集到的数据会首先存储到DDR2-RAM,存储的起始地址会存放在接收地址寄存器。DDR2-RAM 的存储容量为512 Mbyte,因此可以根据具体的诊断需要来配置长度寄存器的值。所有需要采集的信号都会有一个高电平有效的同步信号。由于需要采集的信号可能处于不同的时钟域,因此,数据采集模块内部会利用FIFO 来进行时钟域的同步。DDR2-RAM 中的数据是通过Frame-RAM 来分块读取的。系统为Frame-RAM 定义了2 048 byte的数据空间,其中地址空间为512,数据位宽为32 bit,该512 的地址空间就是接收数据的地址映射空间,DSP/Matlab 就可以通过Co-simulation 接口多次存取该空间的整块数据,完成大块数据的存取。图4 中的ECI(Ethernet Co-simulation Interface)即为上一小节的地址映射模块,每一个FPGA 功能模块都会包含一个这样的模块。其次,数据采集模块的另一个功能是通过DDR2-RAM发送数据到TX-chain,该功能的处理流程是主处理器通过以ECI 接口写数据到Frame-RAM。

5 诊断方法的应用

5.1 项目中应用

该软硬件协处理的FPGA 诊断方法被应用于LTE/GSM MSR 项目的各个阶段。图5 所示为MSR(Multi-Standard Radio)项目的层一系统集成测试验证平台。可以看到,在该平台上,很难采用常用的FPGA 诊断方法。在项目初期,DSP 的程序还未开发完成时,我们利用该方法,通过Matlab 来配置FPGA的控制寄存器,并通过读取状态寄存器来检查FPGA的工作状态。通过一个Matlab 脚本,我们可以方便地完成寄存器的配置和读取。在测试验证阶段,我们主要利用该方法来诊断FPGA 中频处理模块出现的问题,进行定位和分析。在下行信号链路的测试中,当发现频谱仪上的信号异常时,我们会通过该方法来采集DAC 之前的数字信号,并在Matlab 里分析,从而快速地对问题是由FPGA 的下行数字信号处理链路引入的还是模拟部分引入的作出判断。如果问题是由数字部分引入的,就进一步展开更深入的分析,如算法模型的进一步仿真分析,或是RTL仿真分析。在上行信号链路的测试中,当我们发现接收到的数据异常时,我们会利用该协处理的方法采集ADC 之后的数字信号,并在Matlab 分析,查看该节点的信号有无问题,若无问题,该信号则会作为测试矢量,用于提供给上行信号链路的算法模型或RTL 代码作仿真用;若该节点有问题,则可以判断是模拟部分的处理出现问题。这种分段定位诊断问题的方法在项目开发过程中提高了诊断定位问题的效率,实践证明非常有效。

图5 LTE/GSM MSR 测试平台Fig.5 Test platform of LTE/GSM MSR

5.2 应用实例

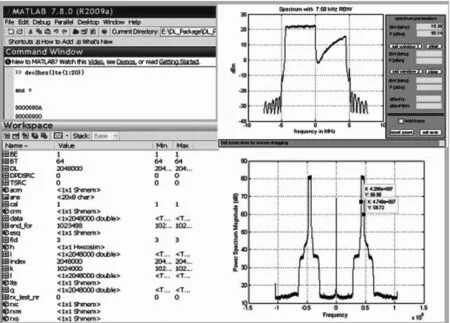

以下用一个FPGA 数字中频诊断的实例做进一步具体说明。图6 所示为利用该诊断方法诊断具体故障的Matlab 工作环境。图中右侧所示的例子为,在测试10 MHz带宽的LTE 上行链路时,实际信号发生仪发出的有用信号的带宽为5 MHz,而在CPRI 接收侧,分析接收到的数据时,发现有用信号的右侧有一个镜像频谱,如图6 右上方的波形所示。利用协处理的诊断方法,在ADC 之后利用数据采集模块采集数据,发现模拟部分输出的数据频谱如图6 右下方所示,有用信号为5 MHz,没有镜像频谱,说明该问题为数字中频模块引入。因此,我们利用采集到的数据作为数字中频模块的仿真激励,对数字中频模块进行RTL 仿真,发现该问题是由LTE 上行信号链路的数字重采样模块引入的。该子模块主要功能是实现数字重采样及时钟域的转换。模块输出接口负责时钟域转换的FIFO,其中I 支路和Q 支路的FIFO 处理机制不一致,Q 支路的FIFO 会发生溢出,导致I 支路和Q 支路的数据不对称,从而引起问题。

图6 Matlab 工作环境及故障诊断举例Fig.6 An examp le and results in Matlab

6 结 论

本文所论述的基于以太网接口采用Matlab 软件对数字中频FPGA 设计进行故障诊断的方法在LTE/GSM MSR 项目开发的各个阶段均被采用。在项目之初,DSP 软件没有开发完成时,利用该方法使用Matlab 软件和以太网接口完成数字中频模块的寄存器配置及状态寄存器的查询。在集成测试的系统验证阶段,通过采集和分析关键节点的信号数据,使中频处理模块上下行链路输出异常的问题能快速定位,并为仿真提供了真实的激励。受FPGA 内部资源的限制,该方法用到的数据采集模块中的采集节点数量相对有限,因此,数字中频设计内部具体子模块的故障定位还需要结合RTL 仿真分析才能最终定位。由于该方法易用且不需要额外硬件接口,被应用于本公司多个MC(Multi-Carrier)项目中。对于该协处理的诊断方法,只要在FPGA 设计中包含有支持Co-simulation 协议的处理模块,就可以普遍应用于FPGA 数字系统的故障诊断。

[1] 3GPP TS 36.104 v9.5.0,Base Station(BS)radio transmission and reception(Release 9)[S] .

[2] 3GPP TS 36.141 v9.5.0, Base Station (BS)conformance testing(Release 9)[ S] .

[3] 3GPP TS 37.104 v9.3.0,Multi-Standard Radio(MSR)Base Station(BS)radio transmission and reception(Release 9)[S] .[4] 3GPP TS 25.104 v9.4.0,Base Station(BS)radio transmission and reception(FDD)(Release 7)[ S] .

[5] Chan C B,Ballagh J B,Shirazi N,et al.Point-to-Point Ethernet hardware co-simulation interface:US,7,636, 653[P/OL] .2009-12-22.http://www.google.com/patents/US7636653.