采用低端FPGA 实现直接数字频率合成的优化设计

2012-03-18李可为张玉平

李可为,张玉平

(成都工业学院 通信工程系,成都611730)

1 引 言

频率合成器广泛地用于通信和电子仪器中,常见的频率合成技术包括初期的RC、LC 振荡电路和被人们熟知的锁相环(PLL)技术,以及直接数字频率合成(DDS)技术[1]。DDS 技术以其相位噪声低、频率稳定度高、频率转换速度快、低功耗、输出频点灵活、集成度高、成本低等优势被广泛采用,而且为了满足高速数据处理的需求,对DDS 技术合成的频率要求也越来越高。之前基于单片机和DDS 芯片的快速频率合成方案[1]已不能满足实际工程的需要,所以DDS 频率合成技术正在向基于FPGA 实现快速频率合成方案趋近[2]。用FPGA 实现DDS 技术比较灵活,可以产生任意信号波形,可以实现多种DDS专用芯片的功能,并且可以任意组合这些功能。但是大多数通过FPGA 实现DDS 技术要满足实际工程要求,对软、硬件和成本要求都很高,所以本文给出了一种利用低端FPGA 实现DDS 的优化设计。该方案系统原理简单,易于实现,软、硬件成本低。

2 DDS 组成及工作原理

DDS 主要由频率控制器、相位累加器、各种波形的ROM 表、D/A 及低通滤波器、放大电路构成,系统原理框图如图1 所示。其中,K 为频率控制字(控制生成波形信号的频率),N 为地址(寻址ROM 的地址),P 为相位控制字(控制生成波形信号的初始相位),Fc为参考时钟频率。累加器在Fc的驱动下以频率控制字K 为步长做累加,输出变化的地址量N;加法器通过P 改变波形的相位(即波形ROM 的初始地址);变化的N 对波形ROM 进行寻址,波形ROM 输出事先将存储的波形经抽样量化以后所得到的值,再经D/A 转换为阶梯波形,再经过低通滤波器平滑后就可以得到合成的信号波形。

图1 DDS 原理框图Fig.1 Schematic diagram of DDS

目前通常使用的频率合成技术有两种[3]。

(1)从频率的角度合成,即通过改变读取波形量化表的频率来改变生成波形的频率。该方法优点是实现简单,但信号频率受限于读取波形量化表的频率。因此该法通常用于所需频率不高、特定固定频率的场合。

(2)从相位的角度合成,本文主要讲述相位合成的实现。

下面介绍基于相位合成实现DDS 的原理。设系统的时钟频率为Fs, RAM 存储波形表的深度为N,频率控制字为K,累加相位为Step,输出波形频率为Fo。在相同时间内且Fs、N、K 均不变的前提下,要得到DDS 输出频率为Fo,输出波形输出的相位为2π×Fo,系统提供的总相位为2π×Fs,则有:

经化简得:

例如:假设Fs为100 MHz,N 为1 024,Step 为2,则Fo输出约为20 kHz;若将Step 改为4,则Fo输出约为40 kHz。

由式(2)可以得出结论:在Fs、N 一定的前提下,可以改变Step 的值得到不同的输出频率Fo,或者灵活配置Fs、N、Step 的值得到需要的输出频率。

对于FPGA 而言,可以通过内部PLL 得到一个频率较高且稳定的Fs,可以使用FPGA 自带片内灵活、丰富的ROM 资源实现波形存储,可见基于低端FPGA 的DDS 实现是可行的。

3 系统主要硬件电路设计

(1)主控系统

频率合成部分以FPGA 为核心,本设计采用Altera 公司的Cyclone-1 EP1C3T144C8 作为系统的核心。该款FPGA 芯片具有逻辑资源丰富、价格适宜、配置简单的优点,其主控系统电路原理如图2 所示。

图2 主控系统电路原理图Fig.2 The control system circuit

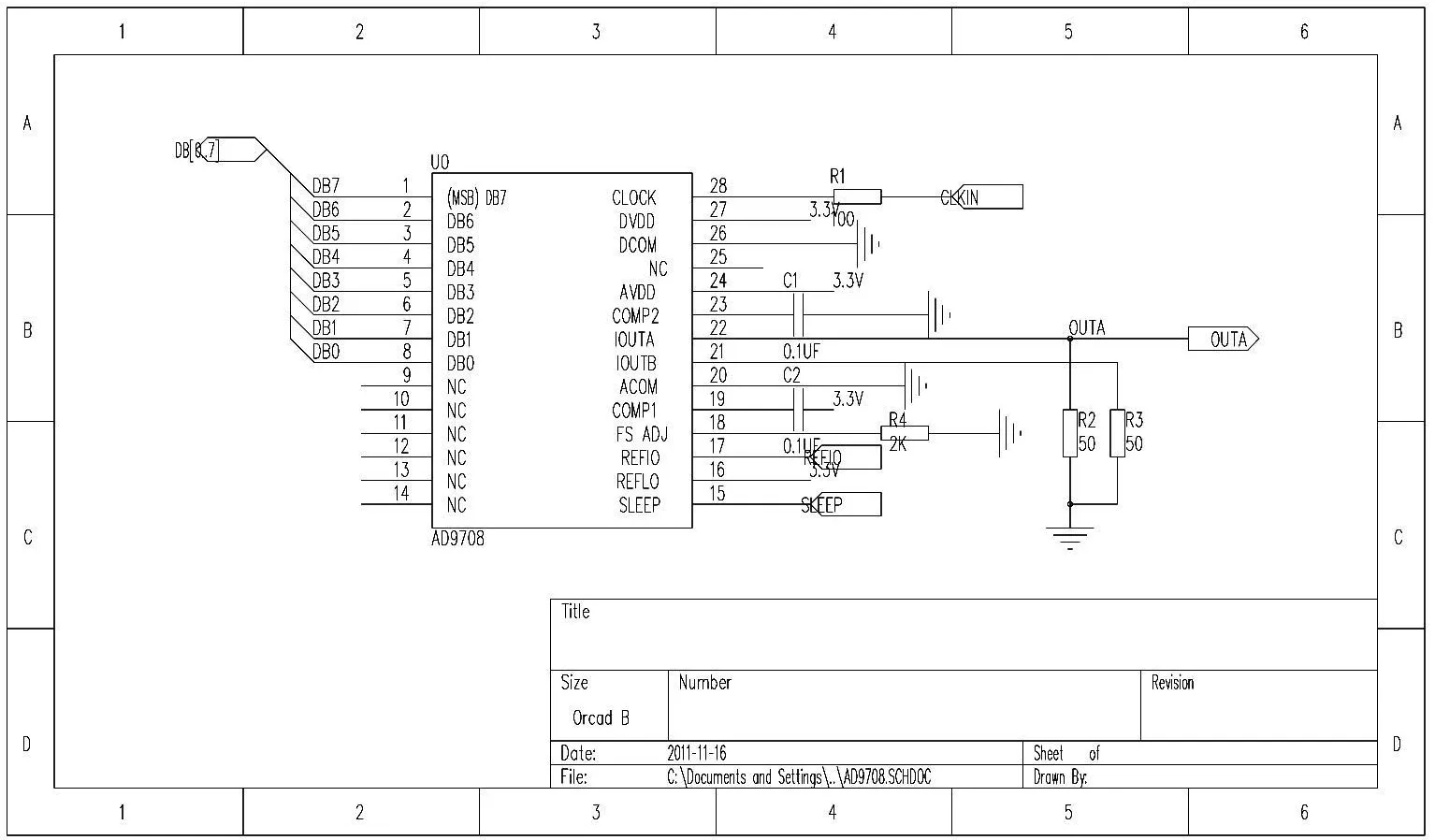

(2)高速DA 系统

高速DA 的电路原理如图3 所示。因为从FPGA的ROM 表中读出是波形的量化值,该值为数字量,因此我们需要使用DA 将波形输出,而此处考虑到本设计输出最大频率为50 MHz,因此需采用高速的DA。本设计采用的是AD 公司的AD9708,该芯片更新速率及低廉的价格能很好地符合我们的应用,并且可通过控制DA 参考电压的方法来实现波形幅度的调节。

图3 高速DA 原理图Fig.3 Circuit of high speed DA

(3)滤波系统[4]

滤波电路采用Chebyshev 10 阶无源滤波电路,其结构如图4 所示。

图4 滤波电路结构图Fig.4 Structure of filter circuit

从DA 转换出来的波形会带有多次谐波,因此需要使用滤波电路来滤掉这些无用的干扰,从而保证波形平稳,而采用多阶滤波可以使波形的变化更陡峭,陡降系数更好。

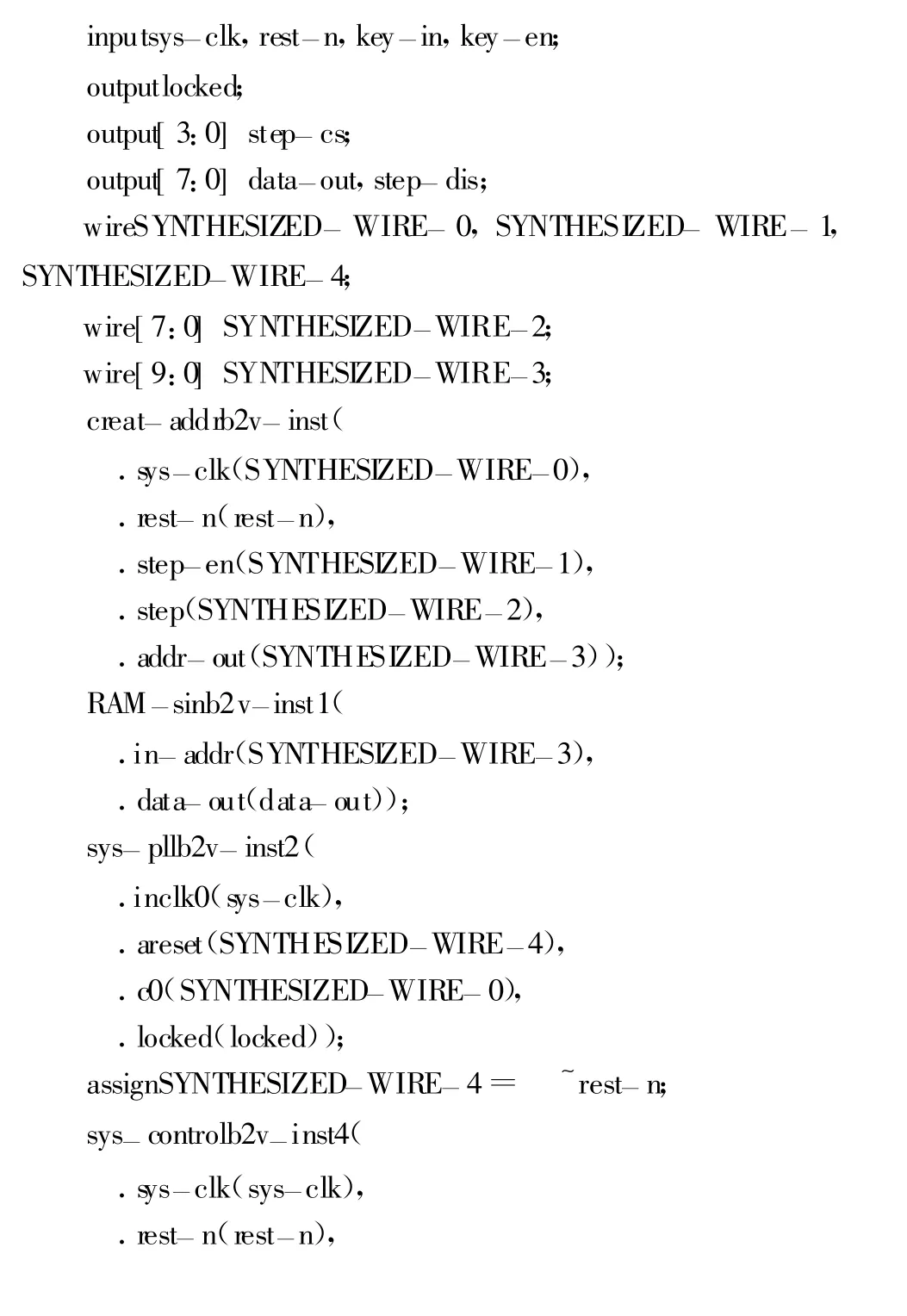

4 系统软件设计

系统软件模块根据系统整体划分为四大部分:相位步进值设置及系统交互模块sys-control, 锁相环模块PLL,读取地址生成create-addr 及波形量化数据存储ROM。

系统顶层代码如下:

5 测试及结果分析

将整个通过编译的工程用Quartus9.0 软件打开,进行全编译,通过Quartus 软件自带的仿真器仿真。由于工程代码仿真波形较复杂,下面的图片只提取了最重要的信号波形进行说明。在仿真中,为了能够简单、明了地观察仿真结果,从仿真开始,整个系统处于复位状态,延时一段时间后,撤销复位状态,整个系统开始工作。在系统时钟设置为100 MHz的前提下,进行仿真。

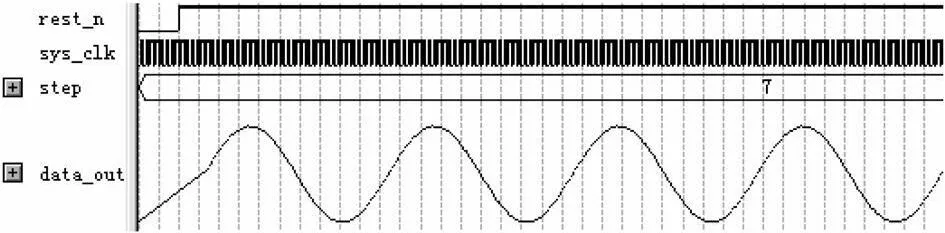

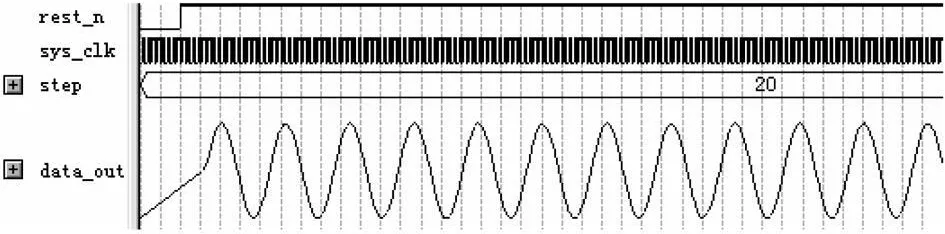

为了方便观测仿真结果,分别给出当Step 为7和20 时的仿真波形,如图5 和图6 所示。

图5 Step 为7 时, data-out 输出仿真波形Fig.5 The output waveform of data-out when Step=7

图6 Step 为20 时, data-out 输出仿真波形Fig.6 The output waveform of data-out when Step=20

从仿真波形可见:通过改变Step 的值(即从相位合成实现DDS),可以得到不同的输出频率;相应地,将波形ROM 中抽样量化波形值替换为其他波形的抽样量化波形值,不但可以实现任意波形DDS,且输出波形频率可以灵活改变。

结果表明:采用低端FPGA 实现直接数字频率合成的优化设计,从相位的角度入手的优化设计是可行的,简化了复杂的实现步骤与处理方法,得到了同样的效果。该优化设计频率分辨率高,输出频点多(可达2N个,N 为波形ROM 的地址位宽);频率切换速度快,可达微秒量级;可以实现任意波形发生;输出相位噪声低,对参考频率源的相位噪声有改善作用;可以产生正交信号;全数字化实现,便于集成,体积小,重量轻,适于模块化应用在实际工程项目中。

6 结 语

本方案利用低端FPGA 实现DDS 的优化设计的实际电路样品经测试,输出波形稳定、精度高,系统原理简单,软、硬件复杂度不高,达到了预期的设计要求。通过在程序中增加相应的功能算法,可实现波形任意发生、频率灵活可调、输出波形频带宽、容易移植及扩展,因此,具有很好的应用价值。

[1] 史彦斌.软件无线电技术基带信号处理的研究[ D] .西安:西北工业大学,2006.

SHI Yan-bin.Research on SDR baseband signal processing[ D] .Xi′an:Northwestern Polytechnical University, 2006.(in Chinese)

[2] 任晓东.CPLD/FPGA 高级应用开发指南[M] .北京:电子工业出版社,2003.

REN Xiao-dong.CPLD/FPGA senior application development guide[M] .Beijing:Publishing House of Electronic Industry,2003.(in Chinese)

[3] 宋晶晶.基于FPGA 的信号源设计与实现[ J] .无线电工程,2003,33(4):27-29,32.

SONG Jing-jing.Design and Implementation of Signal Source Based on FPGA[ J] .Radio Engineering of China, 2003, 33(4):27-29,32.(in Chinese)

[4] 张永顺, 童宁宁, 赵国庆.雷达电子战原理[M] .北京:国防工业出版社,2006.

ZHANG Yong-shun,TONG Ning-ning,ZHAO Guo-qing.Princip les of Radar Electronic Warfare[M] .Beijing:National Defense Industry Press,2006.(in Chinese)