基于FPGA 的S 模式信号处理

2012-03-18黄晓卿

黄晓卿

(中国西南电子技术研究所, 成都610036)

1 引 言

S 模式是一种用于空中交通管制(ATC)的协同式监视数据链,提供了更高的监视精度、性能和效率。随着S 模式在空中交通管制、敌我识别系统(IFF)、机载防撞系统(TCAS/ACAS)、自动广播相关监视(ADS-B)等系统中的越来越广泛应用,对于S模式信号处理终端的信号数据处理能力提出了更高的要求。

S 模式询问/应答机除了兼容处理A/C 模式信号外,还需要准确快速地完成S 模式的全呼、监视和广播等信号的处理。S 模式提供了25 种询问和应答格式,在ICAO 附件10 中对大部分的信号格式进行了规定, 其报文格式分短型(56 bit)和长型(112 bit)两种。S 模式询问/应答机在实现大量数据通信处理的同时,如何能更高效准确快速地完成对其信号处理终端提出了更高要求。

本文着重介绍了S 模式信号处理的硬件设计,针对S 模式询问/应答信号长、携带数据信息量大、干扰脉冲多等特点, 将传统由数据处理器(DSP)完成主要的数据处理设计通过硬件电路现场可编程门阵列(FPGA)实现,充分利用FPGA 的并行高速处理能力,提高S 模式信号处理终端的性能。

2 S 模式信号处理

2.1 信号处理终端组成

S 模式信号处理终端是询问/应答机信号数据处理的核心部分,询问机信号处理终端主要完成对询问信号的编码和对应答信号的解码处理功能,应答机信号处理终端主要完成对询问信号的解码和产生应答信号。信号处理终端组成框图如图1 所示,硬件电路主要由DSP+FPGA+AD+DDS 等器件组成,器件AD 主要实现对中频信号的数据采样(模拟信号转换成数字信号);FPGA 主要完成信号数据处理,包括数据编码、调制、解调、解码、检错和纠错等,具体实现过程见2.3 ~2.6 节,对于询问应答信号的调制解调过程和对应答信号数据的纠错处理这里就不详细介绍;DSP 主要实现与外部设备的数据通信功能(询问机参数、应答机参数和部分数据处理等);DDS 主要完成将数字信号转换成模拟信号。充分利用FPGA 性能好、资源丰富、并行处理能力强以及开发环境优越等特点,将主要的信号处理、数据处理、编解码等功能通过FPGA 来实现完成。

图1 信号处理终端组成框图Fig.1 Block diagram of the Mode S signal processor

2.2 S 模式询问信号格式

S 模式询问信号和应答信号格式[1]如图2 所示。

S 模式询问信号脉冲的P1、P2为前导同步脉冲,P5为旁瓣抑制脉冲,采用脉冲幅度调制(ASK),脉冲宽度为0.8 μs,脉冲间隔为2 μs。数据块脉冲为P6,宽度为16.25μs或30.25 μs,采用的是差分相移键控调制(DPSK),调制速率为4 Mbit/s,包含56 bit或112 bit的信息。最后24 bit数据是询问信息(前3 2bit或88 bit)的循环校验码与飞机地址码和多项式相乘结果的异或数据。

S 模式应答信号由前导同步脉冲和56 bit 或112 bit的数据块组成,前导同步采用脉冲幅度调制(ASK),数据采用脉冲位置调制(BPPM)。前导脉冲共由4 个脉冲组成,脉冲宽度为0.5 μs。前导脉冲用于S 模式应答引导脉冲。数据块每1 μs的时间间隔对应于信息的一个比特。前0.5 μs有脉冲,则信息为“1”;后0.5 μs有脉冲,信息为“0”。传输速率为1 Mbit/s。与S 模式询问信号一样, 数据块最后24 bit是应答信息(前32 bit或88 bit)的循环校验码与飞机地址码的异或数据。

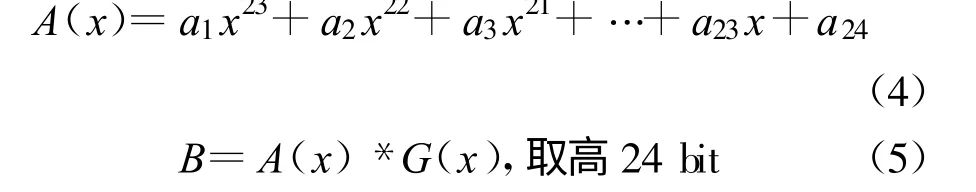

2.3 S 模式询问编码产生原理

S 模式询问机启动S 模式询问时,由DSP 处理器根据询问机启动模式及询问机状态设置,计算出询问信息数据M(x)以及地址码A(x),FPGA 对数据进行编码调制(数据编码原理[2]如图3 所示),并通过DDS 产生询问中频信号启动询问发射。

图3 询问编码过程Fig.3 Uplink encoding process

询问信号数据信息由M(x)(28 bit或88 bit)和AP(24 bit)组成,每种询问格式(详细格式内容见ICAO 附件10)对应具体的M(x),将询问数据信息M(x)与生成多项式G(x)进行循环冗余校验(CRC)得到数据P ,在S 模式的信号处理中,无论是编码还是译码过程都使用了相同的生成多项式G(x)进行数据的循环冗余校验,实现对数据的保护,也为询问机对应答信号的数据检错[3]纠错提供了依据,提高了系统的应答解码能力。

数据B 为地址A(x)与生成多项式G(x)乘积的高24 bit,其中地址码A(x)在询问机全呼询问和广播时为全1,点名询问时为点名的应答机的地址。

数据AP 为多项式P 和多项式B 相异或后的24 bit数据。

2.4 S 模式应答机译码

S 模式应答机在工作过程中,接收机一直处于接收状态(应答机处于应答发射和广播发射除外),并将下变频后的中频信号送入信号处理终端,终端接收并进行询问信号解码。终端处理流程如图4 所示。

图4 应答机询问信号FPGA 处理流程Fig.4 FPGA-based interrogatation signal process flow for transpondor

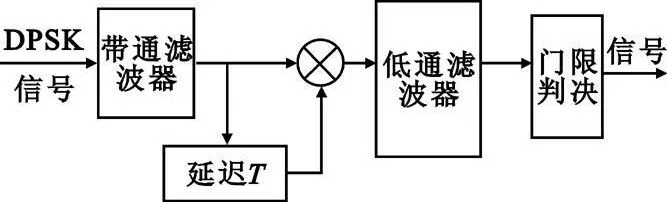

FPGA 接收两路AD 中频采样数据(应答机配备两个全向应答天线),并进行二进制转换,再将数据分别进行ASK 解调和DPSK 解调(解调模型见图5),再进行门限及窄脉冲处理,根据询问格式提取同步脉冲P1和P2,如果满足同步头脉冲条件,则进行上下天线比幅,对幅度强的信号询问旁瓣抑制处理,同时提取DPSK 解调后的脉冲数据,根据脉冲的幅度宽度等信息进行判断, 提取询问数据(56 bit 或112 bit),将询问数据进行译码处理并进行数据检错处理,完成后将数据送入DSP 处理器,DSP 根据当前应答机的状态对询问数据进行后续处理。

图5 DPSK 解调模型Fig.5 Block diagram of DPSK demodulation

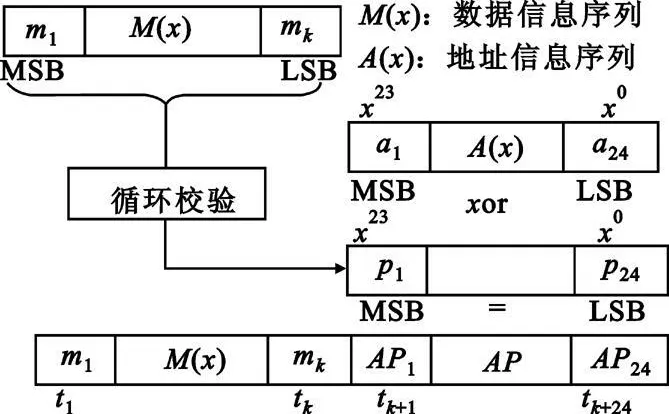

FPGA 实现数据译码处理过程,可根据询问编码的产生过程进行逆过程处理,得到询问信号中的地址信息A(x),也可以通过图6 应答机询问信息数据解码过程得到询问信号中包含的地址信息。应答机对询问信号数据检错的过程实际上就是对译码得到的地址信息A(x)的判断过程,如果A(x)为全1 或者与应答机的地址一致,则询问数据译码正确,进行后续处理,否则译码错误,本次接收数据丢失。

图6 为S 模式应答机对询问信号信息数据的等效解码电路[4],D 为D 触发器,24 个D 触发器初始值为0,模2 和加法网络为所有抽头的D 触发器和输入值模2 和过程。终端FPGA 提取出56 bit 或112 bit数据块后,将所有数据按先高后低(先收到的数据为高)的顺序依次输入到数据输入口A,同时保存输出口C 的前32 bit或88 bit,输出口B 输出的最后24 bit即为译码得到的询问信号中携带的应答机地址,得到原始的询问信息数据。

图6 询问数据译码电路Fig.6 Decoding circuit of interrogation data

2.5 S 模式应答机编码

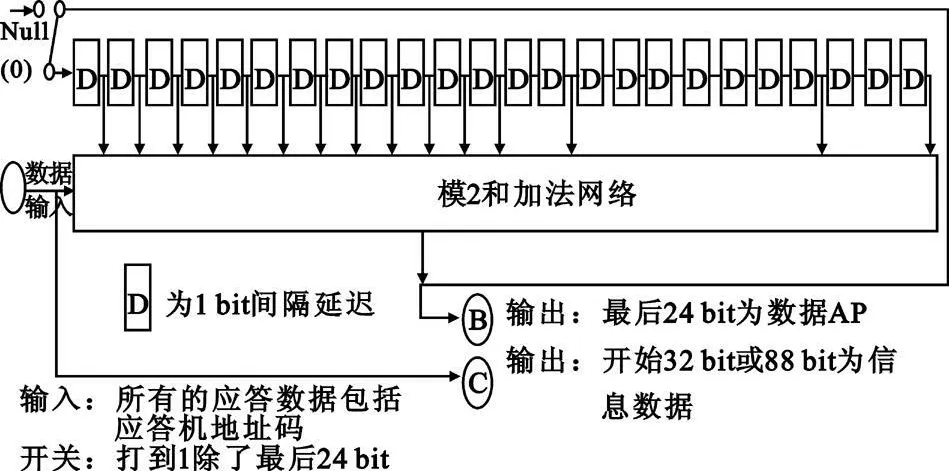

S 模式应答机在收到询问信号(全呼、点名等)后,根据译码结果,产生相应的应答信号(应答机自动广播即S 模式间歇振荡器报告传送能力由应答机自己启动)。应答机的应答信息数据编码产生过程原理如图7 所示。

图7 应答编码过程Fig.7 Downlink encoding p rocess

终端DSP 处理器根据询问模式、数据长度、规程、回答概率、分机状态等信息产生相应格式的应答信号M(x)(28 bit或88 bit),将M(x)和A(x)等数据存入FPGA,FPGA 启动循环冗余校验(CRC),得到24 bit校验数据P,将P 与应答机地址码A(x)相异或,得到24 bit数据AP,再将所有信息数据(M(x)和AP)进行脉位调制后发射。应答信号的循环冗余校验和询问信号的一样。应答信息数据的编码可以根据产生原理分步产生,也可以通过图7 应答信息数据编码过程产生,在FPGA 中可以快速地实现CRC校验、数据异或等功能。需注意当应答格式DF 为0、4、5、16、20、21 或24 时,A(x)为应答机的地址;当DF 为11 时, A(x)为17 bit 0、3 bit CL和4 bit IC;当DF 为17 或18 时,A(x)为24 bit 0。

图8 为S 模式应答机应答信息数据的等效编码电路,与译码电路一样,24 个D 触发器初始值为0,模2 和加法网络为所有抽头的D 触发器和输入值模2和的值。将开关选择位置1,所有数据按先高后低的顺序依次输入到数据输入口A(先收到的数据为高),输入最后24 bit时开关选择位置0,同时保存输出口C的前32 bit或88 bit,输出口B 输出的最后24 bit即为应答编码数据的AP ,完成后FPGA 对编码后的信息数据进行脉位编码,同时终端启动应答发射。

图8 应答数据编码电路Fig.8 Encoding circuit of reply data

2.6 S 模式询问机译码

询问机在发射询问信号后,打开接收机等待接收,应答信号经过接收机下变频后送入信号处理终端,终端接收并进行应答信号处理。终端数据处理通过FPGA 硬件完成,处理流程如图9 所示,FPGA完成数据解调、门限、窄脉冲处理后,提取同步脉冲和应答数据脉冲,并进行脉位解调,提取应答数据和设置数据置信度,将提取的数据译码处理后,进行数据检错处理,如果检错后数据正确,则直接将数据送入DSP 处理器,否则进行数据纠错处理(询问机信号处理终端必须对检错有误的数据进行纠错处理,其纠错原理及方法可参考相关资料,本文不详细叙述),完成后再将纠错后的数据送入DSP 处理器,并将询问结果传给显示等外部设备。FPGA 对应答信息数据的译码处理,可根据应答机的应答编码原理进行逆过程处理,也可以根据应答机的译码电路(如图8 所示,应答信号的译码电路与应答编码电路一致,唯一不同的就是译码电路端口A 输入的是所有的应答数据,端口B 输出的最后24 bit 为应答机的地址码)来实现。

图9 询问机应答信号FPGA 处理流程Fig.9 FPGA-based reply signal process flow for interrogator

询问信号处理终端对应答信号的检错处理,实际上就是对译码完成得到的24 bit地址码与询问机所问应答机地址码的比较判断,如果一致,则数据正确,否则该数据有错误,需要进行纠错处理。

3 数据仿真及结果

在工程设计应用中,根据实际的应用和专业的仪器设备对本文介绍的方法进行了仿真和验证。图10 为S 模式询问信号的产生和处理仿真图,(a)为S模式询问发射信号的原始数据(数据信息为0x20123456789abc),(b)是询问信号经过差分编码后的信号,(c)为调制后的中频询问发射信号,(d)为终端的AD 采样信号(采样率为80 Msample/s,横坐标为采样点数,纵坐标为12 bit采样值),(e)为DPSK 解调处理中采样信号通过一个码元延迟后相乘结果(即差分相乘),(f)为差分相乘信号经过低通滤波后的信号波形(高于该门限的信号为1,低于门限的信号为0),通过DPSK 解调处理,就得到了波形(g),为滤波后信号进行门限判决后的波形,该解调信号和原始信号是一致的。

图10 S 模式询问信号产生和处理仿真波形Fig.10 Modulate and demodu late process of Mode S interrogation signal

在实际调试中,我们通过ChipScope Pro(在线逻辑分析仪)对FPGA 内部的编码解码等程序分别进行数据测试,其中两组数据如下所示。

(1)S 模式询问编码

全呼询问数据前32 bit M(x)=0x58000000,全呼地址为A(x)=0x111111,根据图3 得到AP =0x4A430A,得到发射数据为0x580000004A 430A;应答机通过图 6 (或图 3)可得到询问数据0x58000000111111。短格式点名询问数据前32 bit M(x)=0x20000000, 点名应答机地址为A(x)=0x29CBB8,根据图3 得到AP =0xB115A2,得到发射数据为0x20000000B115A2;应答机通过图6(或图3)可得到询问数据0x20000000B115A2。

(2)S 模式应答编码

广播应答数据前32 bit M(x)=0x58000000,广播地址为A(x)=0x111111,根据图7 得到AP =0x1F10F2,得到发射数据为0x580000001F10F2;询问机通过图 8 (或图 7)可得到广播数据0x58000000111111。短格式点名应答数据前32 bit M(x)=0x20000000, 应答机地址为 A (x)=0x29CBB8,根据图7 得到AP=0xA 9ADE7,得到发射数据为0x20000000 A9ADE7;询问机通过图8(或图7)可得到询问数据0x2000000029CBB8。

4 结束语

本文主要介绍了询问/应答信号的处理过程和数据的编解码原理和硬件实现方法,将传统主要由软件完成的数据处理通过硬件FPGA 完成。该设计已经在工程应用中实现,并通过航管专用测试仪器(美国An Aeroflex 公司的MK12/Mode S IFF Accessory Unit)和航管应答机(美国Honeywell 公司的KT73 Mode S Transponder)测试。随着FPGA 产品的不断更新换代,FPGA 资源越来越大,功耗越来越低,处理速度越来越快,设计者可以实现更优的信号处理,不断提高终端的处理能力,实现系统更高的抗干扰和多目标处理能力。

[1] ICAO.Annex10 to The Convention on International Civil Aviation[M] .2nd ed.[S.l.] :International Civil Aviation Organization,1998.

[2] ICAO.Manual on the Secondary Surveillance Radar(SSR)Systems[M] .3the ed.[ S.l.] :International Civil Aviation Organization,2004.

[3] 徐慧.基于TMS320C6416 的S 模式二次雷达应答信号处理系统[ D] .成都:电子科技大学,2005:11-12.

XU Hui.System of the Second Surveillance Radar mode S signal processor base on TMS320C6416[ D] .Chengdu:University of Electronic Science and Technology of China, 2005:11-12.(in Chinese)

[4] 张尉.二次雷达原理[M] .北京:国防工业出版社, 2009:140-157.

ZHANG Wei.The Theory of Secondary Radar[M] .Beijing:National Defense Industry Press,2009:140-157.(in Chinese)