基于FPGA和UART的MCU总线数据采集系统设计

2012-03-17王敬华丁国清

王敬华,刘 武,丁国清

(上海交通大学 仪器科学与工程系,上海 200240)

设计以上汽集团采埃孚转向系统有限公司的SKII生产线(下称“目标生产线”)为数据采集对象,目标生产线采用BOSCH公司的拧紧器系统,拧紧器系统由拧紧主轴、电源及伺服放大模块、控制器、通讯单元、接口模块和扭矩显示模块。拧紧器系统通过控制器(MCU)采集拧紧器的扭矩并显示在LCD模块上,是一个完整的加工系统。目标生产线由BOSCH公司提供,其拧紧器控制器无法实现更改。随着电子技术的不断发展,在电子设计领域,采用FPGA技术往往能使设计系统简便,在此背景下,为了实现目标生产线扭矩值到服务器数据库的传输,设计了以FPGA为核心的采集系统。

1 总体设计结构

数据采集系统框架如图1所示。

系统以现场可编程门阵列FPGA(Field Programmable Gate Array)为核心,利用FPGA可以方便实现数字器件的逻辑功能,可根据需要,现场改变硬件电路逻辑,大大缩短开发周期,降低成本减少PCB面积,提高系统的可靠性和可维护性。

图1 数据采集系统总体框图Fig.1 Structure diagram of the data acquisition system

MCU为所要采集的目标对象,以总线方式进行数据采集;系统的设计采用硬件编程语言VHDL,分模块进行设计,包括MCU与FPGA接口逻辑电路设计、双端口RAM数据缓存模块、顶层状态机控制模块、UART数据发送模块和时钟分频等模块。整个系统由顶层状态机进行逻辑控制,系统上电后,总线上的数据通过接口逻辑电路解析,把数据缓存到双端口RAM中,再通过UART发送模块实现数据的串行发送。

2 各主要模块设计

下面分别介绍系统主要模块的设计,分为MCU与FPGA的逻辑接口模块、双端口RAM模块,UART发送模块、和状态机控制模块等。

2.1 MCU与FPGA接口模块

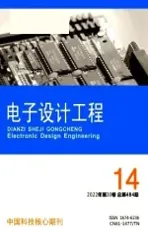

已知P0口为数据为扭矩值,P0口作为地址/数据总线分时复用,通过设置寄存器来锁存地址,通过控制总线设计电路逻辑,接口逻辑电路主要有3个输出,分别是双口RAM的写允许信号RAM_WR、RAM的写地址 RAM_ADDR和输出数据RAM_DATA。图2(a)为程序编译得到接口逻辑框图。

图2 VHDL程序实现的接口和双端口RAM逻辑框图Fig.2 Interface and dual port RAM logic diagram based on VHDL

clk为系统时钟,datain[7.0]实现对单片机 P0口总线数据的采集,in3为地址锁存信号,in5、in7为其他控制信号。P0口数据位为目标数据,故设置8位宽地址锁存单元Signal bus_addr:std_logic_vector(7 downto 0),用 in3 下降沿来锁存数据地址;ram_wr为后端RAM的写允许信号,地址锁存后则把相应的数据则通过 ram_data[7.0]缓存到 RAM的ram_addr[5.0]指定地址中。

2.2 双端口RAM模块

采用FPGA的M4K单元,双端口RAM形式缓存数据,如图 2(b)所示,输入端口 data[7.0]和输出端口 q[7.0]位宽均为8,端口的读和写采用一个同步时钟clock,并且设置读允许rden和写允许wren信号,实现对双端口RAM的读写。RAM 大小设为 64个 words,故写地址 wraddress[5.0]和读地址 rdaddress[5.0]宽度为 6。

通过语句 ram_wr=> ram_wren,,wren=> ram_wren,实现RAM的写控制信号传递,满足条件 in3_not_rise=‘1’and wr=‘0’时,令 ram_wr<= ‘1’,对 RAM 进行写操作,通过语句 ram_addr=> wraddress,wraddress=> wraddress; 确定数据写的地址,把数据写到RAM相应的地址中,实现P0口数据的锁存。

2.3 带缓冲区的UART发送模块

UART(Universal Asynchronous Receive Transmitter)即通用异步收发器,数据通过串口一位一位的传输。UART信号线上共有2种状态,逻辑1(高电平)和逻辑0(低电平)。在发送器空闲时,数据线保持高电平,当有低电平出现时并保持一定的时间就认为是起始位,一般为1位,对应逻辑0。接着数据位一般为8位,低位在前高位在后。而后为校验位,用来判断数据是否有误,在使用中该位常取消。停止位在最后,一般为1位,其对应逻辑为1。

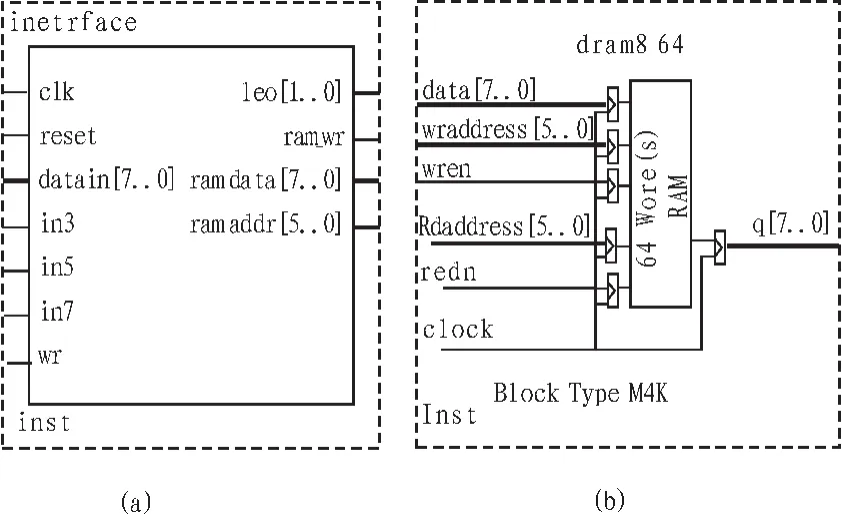

由于要采集的总线数据为连续的多个字节,采用FIFO来缓存数据,通过语句data=>tx_fifo_din,wrreq=>tx_fifo_wr,来实现串口数据的缓存。FIFO逻辑框图如图3(b)所示。

图3 VHDL编译的串口发送模块和FIFO模块框图Fig.3 Serial send and FIFOmodule logic diagram based on VHDL

图3(a)为串行发送模块程序编译图,并行数据通过tx_fifo_din[7.0]传送到发送模块,当 tx_fifo_wr <= '1, 即wrreq有效时把数据写到FIFO中,通过串口发送模块状态机使rdreq有效读取FIFO中的数据,实现串行发送,系统波特率为9 600。

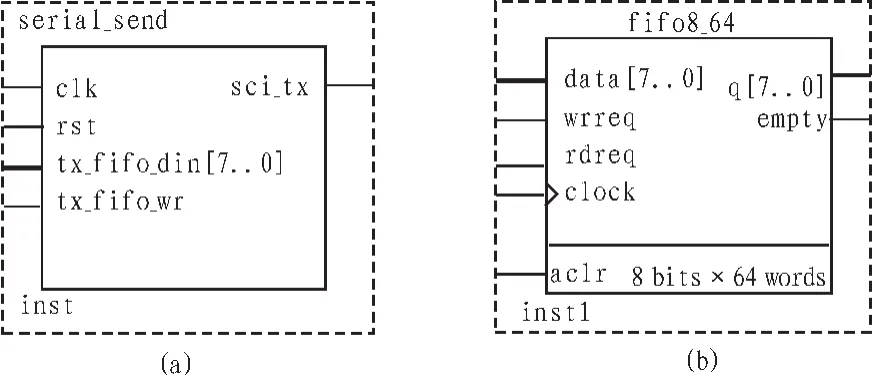

图4 UART发送模块仿真Fig.4 Simulation of the serial send module

图 4(a)中 tx_fifo_din 输入十进制数 170,37 和 170,只有前2个数输入时tx_fifo_wr有效从图4(b)仿真结果可以清楚的看到UART发送器的输出端sci_tx串行的输出二进制数10101010和00100101,转换成十进制即170和37,仿真结果正确。

3 顶层控制的设计

3.1 顶层状态机

设计系统的状态机如图5所示。

图5 设计系统顶层状态机Fig.5 Top statemachine of the design system

定义状态机m_st,共有7个状态,t0至t6,系统首先复位然后进入状态t0,在此处对双口RAM读地址进行初始化,确定RAM中第一个传输数据的地址,然后根据自定义的分频上升沿clk_10ms_rise='1',当此条件满足时,跳转到t1,并且对串行发送器的FIFO初始化即头标志字节十六进制AA;t1状态时发送FIFO头标志字节的写入脉冲,然后跳转到t2;t2状态复位FIFO头字节写入脉冲,根据双口RAM地址条件发送RAM读脉冲,并跳转到t3;t3状态复位RAM读脉冲,并跳转到 t4;t4为延时状态,然后跳转到t5;t5状态再次发送FIFO写脉冲并且把双口RAM中相应地址的数据写到FIFO中,跳转到t6状态;t6状态复位FIFO写脉冲,改变RAM的读地址并循环跳转到t2状态。MCU总线上的数据按照相应的地址缓存到RAM中,然后写到串行发送器的FIFO中,而发送器只要FIFO中有数据就会按照顺序串行的发送出去。

3.2 系统顶层仿真

编写 test程序,仿真结果为图 6(a)所示,数据以十进制显示216为地址单元,9为相应地址单元的数据;217为地址,10为其相应数据,依次类推。通过总线端口dataout[7.0]把地址和数据发送到设计的采集系统中,系统输出仿真结果为图6(b),sci_tx为串行发送模块的数据发送端口,高电平为1,低电平为0,帧格式采用1位低电平起始位,8位数据,1位高电平停止位。数据以二进制的形式读出发送,00001001,0001010,00001011, 等依次对应十进制9,10,11 等。

图6 VHDL程序仿真结果Fig.6 Result of the simulation based on VHDL

4 结 论

系统以FPGA为核心对MCU总线进行数据采集,已经应用到上汽集团采埃孚转向系统有限公司的SKII生产线,实现了数据的采集,具有一定的稳定性和准确性。设计实现了MCS-51单片机总线数据采集的一种方法,在科研和实际工

业生产中具有一定的通用性和扩展性,为数据采集提供了一个新思路。

[1]Cyclone IIDevice Handbook[S].Altera Corporation,2010.

[2]苏航,张宁.FPGA实现UART和MCU一体化设计[J].现代电子技术,2011,34(2):22-28.

SU Hang,ZHANG Ning.Integrated design of MCU and MCU based on FPGA[J].Modern Electronics and Technique,2011,34(2):22-28.

[3]李莉,路而红.电子设计自动化(EDA)[M].北京:中国电力出版社,2009.

[4]胡汉才.单片机原理及其接口技术[M].2版.北京:清华大学出版社,2004.

[5]游至宇,董秀成,杜扬,等.单片机与FPGA/CPLD总线接口逻辑设计[J].单片机与嵌入式系统应用,2008(1):121-123.

YOUZhi-yu,DONGXiu-cheng,DUYang,etal.Thebusinterface design between FPGA and single-chip microcomputer[J].Microcontrollers & Embedded System,2008(1):121-123 .

[6]刘凤新,赵坚固.基于FPGA的多路并行独立串口的实现[J].仪表技术与传感器,2010(11):44-46.

LIU Feng-xin,ZHAO Jian-gu.Implementation of independent multi-chanel parallel serial portbased on FPGA[J].Instrument Technical and Sensor,2010(11):44-46.