数字电路设计中部分常见问题解析

2012-01-29茶国智

茶国智

(大理学院 工程学院,云南 大理 671003)

1 常见问题解析

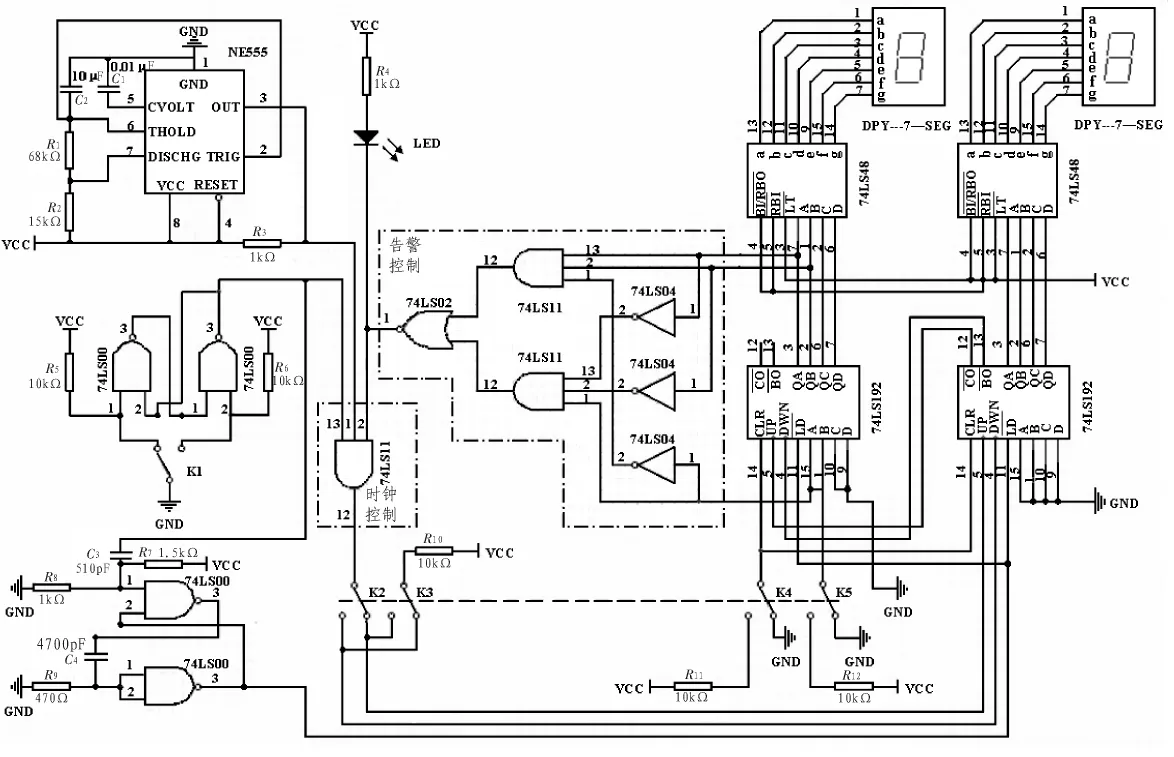

文中借助学生设计的双向(加减)计时器,如图1所示,来探讨电路设计中3个方面的常见问题。

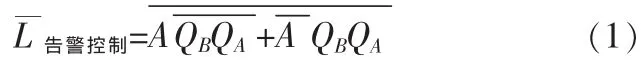

图1所示的电路可实现0~30 s双向(即加减)计时,这是该电路的优点,因为目前常见的多为单向计时电路,图2所示为其仿真波形。该电路包括秒脉冲发生器、计数器、译码显示电路、各种控制电路等几个部分组成。具体为[1-5]:由一个工作于多谐振荡模式的NE555产生1 Hz的时钟CP,经过时钟控制电路去激励两个异步时序的74LS192开始计数,计数输出给两个74LS48进行译码,最后由2个七段数码管完成计时显示,而控制部分主要包括:开关K1和RS锁存器完成计时开始和暂停、联动开关K2~K5和单稳态电路完成加减计数时钟切换和相应初值设定、LED和限值反馈控制电路完成告警、时钟CP控制等。

1.1 控制方面

在设计中,先对电路性能指标要求进行分析,然后确立设计方案(或原理框图),一般在此基础上选择合适的功能器件是很容易搭建出各主要功能模块的。但是,如何将各功能模块间正确的“联系”起来最终实现所有的电路功能,在实际设计中这往往是一个令人头痛的问题,相信许多设计者对此都有同感。

这里将此部分称为控制方面[6]的设计问题,实质要求为:逻辑上需要用一些信号(称为控制信号)去决定某一个或一些信号(被控制信号)。对此的解决办法是:把此部分看作一个简单的逻辑电路(组合逻辑或时序逻辑)进行设计。因此,关键步骤是:选取合适的输入控制信号和正确列出真值表(对组合逻辑电路而言)或状态表(对时序逻辑电路而言)。

实际中,一般多属于组合逻辑情况,即此时刻输出状态由此时刻输入状态决定,体现“即时”控制的内涵。文中就探讨属组合逻辑的控制,且以前述电路中的告警控制和时钟控制为例。

图1 双向计时器的总电路Fig.1 Total circuit diagram of two-way timer

图2 双向计时器的仿真波形Fig.2 Simulation waveform diagram of two-way timer

1)告警控制

在图1电路中当正向加计时到30 s或者反向减计时到00 s时要求实现LED告警功能。

张双田[23]基于多孔介质和Syamlal-O′brien曳力双流体模型,研究了振动流化床内气固两相流场分布,用正交试验方法考察了表观气速、振动强度、分布板开孔率对床内气泡行为、床层压降及其波动、床层物料分布及物料流化的均匀性等流化质量的影响,建立了流化质量与影响因素的函数关系式,并进行了显著性检验。结果表明:适宜的分布板床层压降比为0.17,床层径向不均匀度与操作参数、分布板开孔率的关系式为

首先,得选取合适的输入控制信号,从反馈控制的角度一般选择两74LS192的计数输出端(QDQCQBQA)。若对于单向计数告警控制来讲,确实可以。但是对双向计数来讲,因为对应于加减计时的限值30 s和00 s,两74LS192的计数输出为“00000011”和“00000000”,可见两种状态下仅高位(十位)片74LS192的QBQA不同,仔细分析仅借助两74LS192的输出是不能实现告警控制的,需再寻找与这两限值状态有关的信号,不难发现两74LS192的初值输入端(D C B A)可为我们解决问题提供帮助。最终,选出高位(十位)片74LS192的计数输出端QBQA和初值输入端A作为输入控制信号。

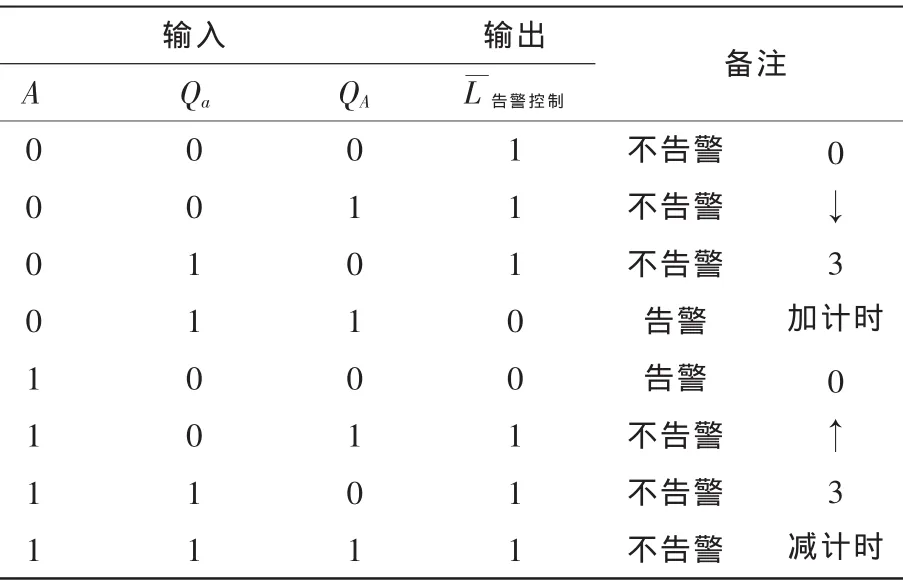

其次,正确列出真值表,如表1所示。由于LED为共阴极接法,故告警控制输出为低有效,用L告警控制表示。

最后,根据表1可得到逻辑表达式为

由(1)式设计的告警控制电路如图1中虚框部分所示。

2)时钟控制

对时序逻辑电路设计而言时钟控制一般都会涉及的。图1所示电路中的计时开始/暂停/结束等功能就是通过控制时钟CP的开启与关闭来实现的。图中由基本RS锁存器的输出LRS锁存器实现计时开始/暂停,前述的告警控制的输出L告警控制实现计时结束,故选取LRS锁存器、L告警控制、时钟CP为输入控制信号,列出真值表如表2所示,其中输出用L时钟控制表示。在列真值表时如何处理像时钟CP这样高低电平都有的输入信号可能会是个难题,方法就是高低情况都列出。

表1 告警控制真值表Tab.1 Truth table of alarm-control

表2 时钟控制真值表Tab.2 Truth table of clock-cotrol

由表2可得逻辑表达式:

根据(2)式设计的时钟控制电路如图1中虚框部分所示。

最后,再对前述两例作个强调:举告警控制例子旨在介绍输入控制信号可选取(来自)任何有帮助的信号,而举时钟控制例子旨在介绍列真值表时对类似CP信号的处理。

1.2 时序方面

数字电路设计中往往需要对时序[7]作个抉择:是同步还是异步?比较二者,异步的电路结构较同步简单,但同步的时延较异步小、速度快、便于控制。在电路设计中到底采用何种时序可综合权衡考虑,当然从便于控制角度,一般多采用同步。

图1所示电路采用了异步时序,两片74LS192间连接比较简单,采用类似“级联”的方法,即直接将低位(个位)片的进位和借位输出作为高位(十位)片的时钟输入即可。如对异步电路进行软件仿真时常会观察到毛刺现象,就是由于其时延较大的原因,这在图2所示的仿真波形中即可观察到。为减少时延,也可把该电路改为同步时序,可采用“分频”的方法实现,即NE555产生1 Hz的时钟信号送低位(个位)片,同时对NE555产生1 Hz的时钟信号作十分频送高位(十位)片即可,当然其它相关的控制电路也需作相应的修改。

无论是异步的“级联”还是同步的“分频”,仔细分析两者都在做共同的“工作”:即都在处理类似“进制”的问题,如图1所示电路中低位片与高位片间为逢十进一的“进制”。

1.3 引脚方面

只有对IC的引脚[8]作正确的认识,才能很好地使用IC完成电路的设计,下面对一些特殊引脚作些解析。

1)“高/低有效”引脚

“高/低有效”是指当该引脚为高/低电平时执行某个规定动作或功能。如74LS192的第14引脚(CLR)为“高有效”,即当该引脚为高电平时执行清零动作(功能);而第11引脚(LD)则为“低有效”,即当该引脚为低电平时执行预置数动作或功能。

2)“同步”引脚

“同步”是指当该引脚处于有效电平时还不能即刻执行规定动作或功能,而必须等到时钟的有效沿到来时才可执行,即要与时钟的有效沿同步。

如另一种常用的计数器74LS161的第9引脚(LD)即为“同步”引脚,当它处于低有效电平时,还要等到时钟的有效上升沿后才能执行预置数动作或功能。

3)“异步”引脚

“异步”是指该引脚一旦处于有效电平则不必等到时钟CP的有效沿到来就即刻执行规定动作或功能,即可不与时钟CP的有效沿同步而为异步。

如74LS192的第14引脚(CLR)和第11引脚(LD)皆为“异步”引脚,一旦处于其有效电平时将即刻执行清零和预置数动作或功能。

2 结束语

数字电路设计中常会遇到诸多问题,文中借助一个0~30 s双向(加减)计时器电路,采用例解形式对控制、时序、引脚等几个方面的常见问题进行了解析。

[1]刘霞.电子设计与实践[M].北京:电子工业出版社,2009.

[2]沈建国,雷剑虹.数字逻辑与数字系统基础[M].北京:高等教育出版社,2004.

[3]王兢,王洪玉.数字电路与系统[M].北京:电子工业出版社,2004.

[4]Wakerly J F.Digital Design:Principles and Practices[M].3rd Ed.Published by arrangement with Prentice Hall Inc.,Pearson Education Company,2000.

[5]孙频栋,曹江.电子设计自动化[M].2版.北京:化学工业出版社,2004.

[6]瞿德福.实用数字电路手册[M].北京:机械工业出版社,1997.

[7]康华光.电子技术基础(数字部分)[M].5版.北京:高等教育出版社,2005.

[8]阎石.数学电子技术基础[M].4版.北京:高等教育出版社,1998.