基于Mealy型状态机的莫尔条纹细分和辨向技术

2012-01-19邱葭华

邱葭华,胡 毅

(合肥工业大学仪器科学与光电工程学院,安徽合肥 230009)

基于Mealy型状态机的莫尔条纹细分和辨向技术

邱葭华,胡 毅

(合肥工业大学仪器科学与光电工程学院,安徽合肥 230009)

介绍了一种利用VHDL语言描述的Mealy型状态机对光栅莫尔条纹进行8细分和辨向的方法。该方法通过状态机对经过预处理电路的光栅信号变化状态进行判断,从而输出计数脉冲和方向信号。通过一种改进的计数方法,避免了尖峰干扰脉冲对计数值的影响,提高了细分和计数精度。

莫尔条纹;细分和辨向;VHDL;Mealy状态机;脉冲干扰

光栅作为精密测量位移的一种重要工具,已在精密仪器、高精度精密加工等领域得到了广泛应用[1]。当光栅尺沿垂直于栅线相对移动一个栅距时,莫尔条纹就移动一个条纹间距,通过统计光电元件接收到的莫尔条纹变化的周期数便得知光栅尺的位移量[2]。

随着超精密加工技术的发展,对光栅测量精度的要求也提高,需要提高光栅测量的分辨率。提高光栅测量分辨率可以通过提高光栅刻线密度实现,但这样会增加成本,且随着刻线密度的增加,要进一步提高刻线密度在工艺上实现难度也较大,同时栅距越小,对光学系统和机械机构的要求也越严格[3]。

通过对光栅信号进行细分同样可以提高光栅的测量分辨率,并且成本较低。传统硬件细分方法的电路较为复杂,随着大规模可编程逻辑器件的发展,许多传统的逻辑电路可以用可编程逻辑器件代替,同时系统的可靠性和处理速度也将提高[4]。文中介绍了一种基于FPGA对光栅莫尔条纹进行8细分和辨向的方法。

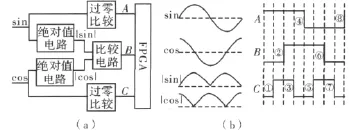

1 光栅信号预处理

如图1所示,两路相位相差90°的正余弦信号分别通过两个过零比较器,得到两信号频率和原始正余弦信号频率相同的方波信号A、B。另外,此正余弦信号分别通过两个绝对值电路后,翔实送入比较电路进行比较,将会得到一信号频率为原始正余弦信号频率两倍的方波信号C。通过FPGA对A、B、C这3路方波信号进行处理,实现莫尔条纹的8细分和辨向。

图1 光栅信号预处理电路框图及各信号示意图

2 光栅8细分辨向和计数的FPGA实现

2.1 8细分和辨向分析

图1所示是相位相差90°的正余弦信号,经过预处理电路后得到的A、B、C 3路信号在一个周期内的电平变化,可以通过对A、B、C 3路信号的每个上升沿和下降沿进行计数从而得到8倍频计数。但是用这种方法处理,当信号受到干扰产生尖峰脉冲时,将会出现重复计数的情况,导致计数值有较大的误差,严重影响光栅的计量精度。

对图1中的A、B、C 3路信号的电平状态进行分析可以发现,在一个周期内,A、B、C 3路信号的电平状态总共有以下 8 种状态:100、101、111、110、010、011、001、000。这8种状态的变化顺序正好组成一个3位的格雷码,按照3位格雷码对应的十进制数,分别将这8 种状态定义为 S7、S6、S5、S4、S3、S2、S1、S0。当光栅正向移动时,A信号相位超期 B信号90°,A、B、C 3路信号的电平状态按照 S7-S6-S5-S4-S3-S2-S1-S0-S7的顺序循环变化;当光栅反向移动时,A信号相位落后B信号90°,A、B、C 3路信号的电平状态按照S4-S5-S6-S7-S0-S1-S2-S3-S4的顺序循环变化。

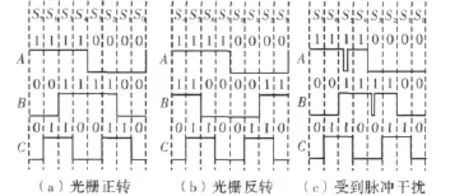

图2(a)中显示了光栅正向移动时的情况,图2(b)中显示了光栅反向移动时的情况。

图2 光栅移动和受到脉冲干扰时状态变化图

由以上分析可知,通过对电平状态变化的次数进行计数可得到光栅移动的距离,根据电平状态的变化顺序可以得到光栅移动的方向。可以设计一个模块,当A、B、C信号的电平状态按照S7-S6-S5-S4-S3-S2-S1-S0-S7顺序变化一次表示光栅正向移动1/8栅距,此时输出一个计数脉冲,方向信号置1;当A、B、C信号的电平状态按照 S0-S1-S2-S3-S4-S5-S6-S7-S0顺序变化一次表示光栅反向移动1/8栅距,此时输出一个计数脉冲,方向信号置0;当A、B、C不改变时表示光栅移动不到1/8栅距,不输出计数脉冲,方向信号保持不变。当光栅受到脉冲干扰时:在S5状态比没有干扰的情况多了一次“111-101-111”状态变化,计数器将进行一次“加1”和一次“减1”操作,计数值不受脉冲干扰的影响;在S3状态比没有干扰的情况多了一次“010-000-010”状态变化,由于这两次变化均不在前文所述的状态变化顺序里,计数器将不进行操作,计数值不受脉冲干扰的影响。

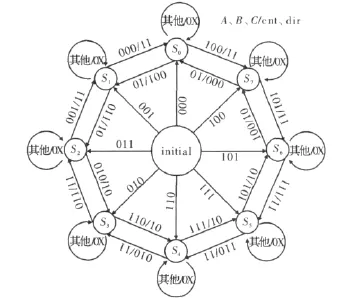

2.2 光栅8细分和辨向FPGA实现

通过以上分析,可以在FPGA中设计一个Mealy型状态机,根据A、B、C的电平状态决定输出计数脉冲和方向信号[5],其状态图如图3所示,initial表示初始状态,S0、S1、S2、S3、S4、S5、S6、S7分别为 Mealy 型状态机的8个状态;两个状态间的连线和箭头表示状态的变化方向,当连线的起点和终点都在同一个状态上时,表示状态不发生改变;连线一侧的数字由两部分组成,如001/11,斜线上面的部分是导致状态改变的A、B、C信号的输入值,斜线下面的部分是输出的计数脉冲cnt和方向信号direct,X表示输出的值不发生改变。

图3 Mealy状态机的状态图

根据图3所示的状态图,以VHDL语言编程,用QuartusⅡ进行仿真得到如图4所示的波形。在每次有效状态变化的下一个时钟周期输出一个计数脉冲,同时方向信号也发生相应的改变;如果发生的是非有效状态变化,不输出计数脉冲,方向信号保持不变。

图4 光栅8细分和辨向仿真图

2.3 光栅细分计数

根据细分模块输出的计数脉冲和方向信号,需要设计一个双向的可逆计数器来完成光栅细分后的计数。由于对于不同的光栅计数最大值可能不相同,所以在计数器模块中需要添加一个可以改变的计数最大值,当计数器正向计数到最大值时,继续进行加计数将会返回零;当计数器反向计数到零时,继续减计数将会返回设定的最大值。

光栅8细分模块和计数模块构成的总体模块图如图5所示,该模块的总体仿真结果如图6所示。为提高细分和计数的精度,8细分模块和计数模块要求同步时钟的频率比较高,然而当直接使用比较高频率的时钟信号时,高频率时钟信号可能会对外围电路产生干扰,为避免这种干扰,可以采用频率比较低的时钟源信号,通过FPGA内部的锁相环电路(PPL)进行倍频后使用[6]。

3 计数误差分析和解决

光栅信号在受到干扰时,会产生尖峰脉冲,经过前面的预处理电路后,可能会出现信号脉冲的跳变,这种信号脉冲跳变会给计数带来影响,使测量的误差较大。当采用经典的计数方法对输入信号的上升沿和下降沿进行计数时,每产生一个尖峰脉冲都会使得计数值额外增加或者减少1,并且无法避免这样的误差。

图7为光栅输出信号受到尖峰脉冲干扰时,输出计数值的情况。图中共模拟了5处脉冲干扰,这些脉冲干扰可以分为两类,一类脉冲干扰对计数器不产生影响,另外一类脉冲干扰使计数器产生额外的加和减操作,但是对计数值结果不产生影响。

设计中所用的计数方法可以消除由于脉冲干扰产生的计数误差。当光栅的输出信号在没有受到干扰时,从S6状态到S4状态计数器应该进行两次“加1”的操作,计数值增加2。在此过程中由于受到两次脉冲干扰,信号的状态变化为:101-111-011-111-110-101-110,根据前文所述的细分和计数方法,计数器分别进行的操作为:“加 1”、“无计数”、“无计数”、“加1”、“无计数”、“无计数”,计数值增加2。当光栅的输出信号在没有受到干扰时,从S3状态到S1状态计数器应该进行两次“加1”的操作,计数值增加2。在此过程中由于受到3次脉冲干扰,信号的状态变化为:010-110-010-011-010-011-001-011-001,根据前文所述的细分和计数方法,计数器分别进行的操作为:“减1”、“加1”、“加1”、“减1”、“加1”、“加1”、“减1”、“加1”,计数器累加后,计数值增加2。通过以上分析可以发现,当光栅信号受到干扰产生脉冲跳变时,采用设计中的方法会通过“不进行计数操作”或者进行一次成对的“加1”和“减1”操作来保证计数值的准确,消除由于脉冲干扰而产生的计数误差。

4 结束语

该设计先将光栅的正余弦两路信号,经过绝对值电路和比较电路得到3路方波信号,通过VHDL描述的Mealy型状态机,对3路信号的状态变化和状态改变顺序进行处理,从而输出计数脉冲和方向信号,完成对光栅莫尔条纹的8细分和辨向。传统的计数方法在有尖峰脉冲干扰时会有较大误差,为避免这种干扰对计数值的影响,设计利用一种改进的计数方法来实现细分计数,从而提高了细分和计数的精度。

[1]朱应时.圆光栅的高精度高质量莫尔条纹信号的研究[J].计量学报,1995,16(4):280 -285,296.

[2]张善锺.计量光栅计数[M].北京:机械工业出版社,1985.

[3]吕孟军.光栅莫尔条纹电子学细分技术研究[D].南京:南京航空航天大学,2008.

[4]唐晖,叶险峰,李向军.一种基于FPGA的光栅莫尔条纹数字细分技术[J].计量技术,2006(10):14-17.

[5]潘松,黄继业.EDA技术实用教程[M].2版.北京:科学出版社,2005.

[6]陈兴文,刘燕.基于FPGA技术消除光电编码器抖动干扰的设计[J].设计与研究,2005(2):33-34.

Moore Stripes Subdivision and the Differentiation of Direction Based on Mealy State Machine

QIU Jiahua,HU Yi

(School of Instrument Science and Opto-electronic Engineering,Hefei University of Technology,Hefei 230009,China)

This article describes a way of Moore stripes subdivision and the differentiation of direction based on the Mealy state machine and described by the VHDL language.By this method,the state machine judges the change of the grating signal of the pre-processed circuit and then outputs the count pulse and direction signal.By an improved counting method the effect of the peak interference pulse on the count is avoided and the accuracy of the subdivision and counting is improved.

moore stripes;subdivide with differentiation toward;VHDL;Mealy state machine;pulse interference

TN29

A

1007-7820(2012)08-067-03

2012-03-04

邱葭华(1986—),男,硕士研究生。研究方向:精密测试技术及仪器。