基于CJTAG的互联信号完整性测试

2012-01-19黄凤彩颜学龙

黄凤彩,颜学龙

(桂林电子科技大学电子工程与自动化学院,广西桂林 541004)

基于CJTAG的互联信号完整性测试

黄凤彩,颜学龙

(桂林电子科技大学电子工程与自动化学院,广西桂林 541004)

随着IP核在片上系统中的大量使用,IP核间的互连总线大量增加,引发信号完整性问题,同时传统的串型扫描拓扑结构,已不能满足测试系统发展所要求的任务,IEEE 1149.7标准提出了包含支持3种拓扑结构的TAP.7接口规范。文中提出了基于CJTAG互联信号完整性测试方法,重点对此TAP.7接口转换器进行了设计,通过系统级测试具有良好的应用前景。

串型扫描;CJTAG;TAP.7接口;信号完整性

随着芯片特征尺寸越来越小以及工作时钟频率越来越高,片上系统的IP核间互连线的交叉耦合、电感以及寄生电容对电路的性能有较大变大。与此同时,系统设计从之前的简单电路板向复杂的多芯片片上电路系统架构发展,消费类电子产品以及手持终端的研发工作者已经面临着日趋严格的引脚与封装要求。

边界扫描技术是一种符合IEEE 1149.1的规范可测性设计技术,JTAG设计的实现使测试的复杂度降低、质量升高而且使芯片面市的时间缩短,适合应用于超大规模集成电路的IP核间互连线测试系统。IEEE 1149.7是德州仪器公司推出的一种新的双引脚测试跟调试接口标准。IEEE 1149.7标准在兼容了IEEE 1149.1标准的同时,还增加了功耗控制功能;包含了1-bit芯片旁路功能,使扫描链长度减少;定义了能够直接寻址的星型扫描拓;具有支持片上多TAPC串行结构的功能。随着IEEE 1149.7标准应用的推广,基于CJTAG的互联信号完整性测试具有广阔的应用前景。

1 CJTAP介绍

紧凑型边界扫描测试(CJTAG)的接口是基于TAP.7。CJTAG按功能划分可分为6级,每级都在上一级的功能基础上增加新的功能。T0层以IEEE 1149.1为基础,并且支持多片上TAPC串行结构;T1层增加了功能复位、测试复位、电源控制功能,支持TAP.7寄存器以及控制器命令;T2层增加了芯片级旁路功能,减小了扫描链长度,同时起到“热连接保护”的作用;T3层增加了支持可直接寻址的4线星型拓扑扫描机制;T4层给出了支持2引脚的连接方式。T5层增加了数据传输功能并且支持除了边界扫描以外的功能。

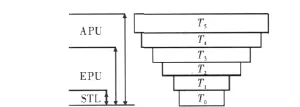

CJTAG包含3种操作方式。系统测试逻辑(STL),基于IEEE 1149.1标准并且包含T0级的所有功能;复位与选择单元(RSU),可支持各种不同的复位方式,同时选择功能也可以把TAP.7控制器设置为在线或者离线状态;扩展协议单元(EPU)具有T1到T3级的所有功能,提供1-bit芯片旁路路径,是连接CJTAG协议和JTAG的纽带;高级协议单元(APU)完全支持两个接脚协议,支持高级扫描格式,使扫描性能得到了提高,同时也包含了T4到T5级的全部功能和支持两个数据通道对后台数据进行传输。TAP.7控制器可以由RSU/EPU/APU任意组合而成。分模块构建TAP.7控制器不仅可以满足TAP.7各个层次的需求还允许RSU功能运用到其他技术中。图1为CJTAG层次分布图。

图1 CJTAG层次分布图

2 基于CJATG的TAP.7接口转换器

图2为基于JTAC的SI互联测试系统原理图。

图2 基于JTAC的SI互联测试系统

图2系统是基于IEEE 1149.1接口的互联测试系统,IEEE 1149.7 DTS生成的测试矢量不能直接施加到基于JTAC的SI互联测试系统中,这就需要有一个1149.7接口将IEEE 1149.7 DTS测试系统生成的符合1149.7标准的测试矢量,转换成能够直接施加到符合1149.1接口标准的测试矢量,即TAP.7转换器。图3为基于TAP.7转换器的测试连接。

图3 基于TAP.7转换器的测试连接

如图3所示,TAP.7转换器中的TAP控制器为ADTAPC(TAPC),主要通过完成对TAP.7信号的控制操作,实现新的升级功能特性,TAP.7信号的测试跟调试逻辑被解码成符合TAP.1接口的时序信号,进而实现对IEEE 1149.1器件的TAPC控制。IEEE 1149.1 IP具有符合IEEE 1149.1测试标准的测试JATG口的器件(STL),其中含有的TAP控制器(芯片级TAPC即CLTAPC)。CLTAPC是符合IEEE 1149.1测试标准规范的TAP接口,主要可以完成对器件的测试功能以及对调试逻辑的控制,进而完成相应的调试。

3 CJTAG的命令实现

3.1 零位扫描

TAP.7转换器的主要功能是对原有TAP.1接口的兼容同时提供 IEEE 1149.7标准规范的扩展功能,TAP.7命令能够实现大部分的扩展功能。CJTAG扩展了JTAG标准对TAPC状态序列的定义,以达到对CJTAG中的TAP.7的控制,JTAG的协议被这些控制序列兼容,保证了JTAG和CJTAG可以在系统中同时工作。在此基础上,将要实现一个全新的TAPC序列,叫做零位扫描(ZBS-Zero_Bit_Scan)。

TAP.7控制器的命令实现包括两个步骤:ZBS探测与控制级别的锁定以及命令的产生和实现。CJTAG通过零位DR扫描的方式生成ZBS,随后通过锁住ZBS计数以完成控制级(Control Level)的产生,最后生成命令。图4为CJTAG的TAP运作时序图。

图4 CJTAG的TAP运作时序图

图5是通过VerilogHDL语言描述的多always并行语句生成的TAP控制器状态机功能仿真波形图,tck时钟频率100 MHz。

通过将BYPASS或IDCODE指令与ZBS相结合,设定TAP.7控制器的控制级。ZBS是一种TAPC状态变化顺序,是从Select-DR-Scan状态开始扫描,经过Capture-DR状态后不经过Shift-DR状态直接到Exit-DR状态,继续转移直到离开Update-DR状态,这样一次ZBS过程就完成了。TAP.7控制器中的ZBS-COUNT计数器从零开始计数,ZBS连续完成一次,ZBS-COUNT计数器的值就会加1,ZBS-COUNT计数值不能>7。如果DR扫描过程中含有一个Shift-DR状态同时ZBS计数值>0,锁定ZBS-COUNT的计数值。ZBS-COUNT控制器的不同控制级别执行不同的功能,具体如表1所示。

图5 TAP控制器状态机功能仿真波形图

表1 ZBS产生的控制级别及功能

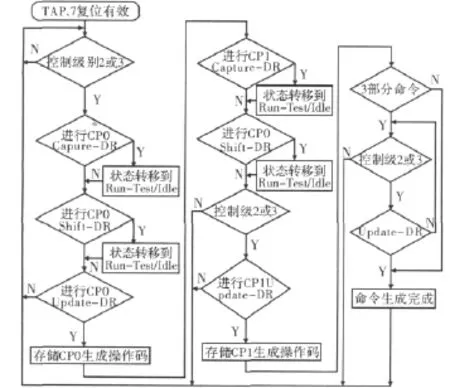

3.2 CJTAG的命令生成

CJTAG命令是由10位值构成,当控制级等于2且ZBS被锁住时,经过两个连续的DR扫描,可生成CJTAG的10位命令。CJTAG的命令由两部分构成:命令的前5位(CP0)是命令的操作码,命令的后5位(CP1)是命令的操作数。除了上述两部分类型的命令,还有一些用于发送和接收数据的命令,这种类型的命令被称作3部分类型命令。在这类命令中,除了CP0与CP1部分以外,还包含了一个额外的DR扫描,数据的传输将通过它来完成。图6为CJTAG的命令状态转移图。

图6 CJTAG的命令状态转移图

图7 CJTAG的命令仿真图

4 结束语

数字信号因为传输线间存在串扰电容和串扰电感而产生畸形,使得高速互连系统的信号完整性测试变的困难。边界扫描测试技术在超大规模的集成电路中得到广泛的应用以及测试标准的发展,又对测试接口设计提出了更高的要求。IEEE 1149.7测试标准中规范的TAP.7接口含有TAP.1接口没有的功能特性,把IEEE 1149.7应用于高速信号完整性测试中,对高速信号完整性测试具有重要意义。本文中设计的基于TAP.7的TAP.7控制器的接口是一种基于原有的JTAG器件的TAP.1接口,在TAP.1接口的基础上添加相应的逻辑硬件层来实现扩展功能的升级接口,在目前基于TAP.1接口的系统级测试中有良好的应用前景。文中为高速信号互联系统的信号完征信测试提供了一种新的方法,对IEEE 1149.7标准规范在边界扫描系统中的研究与设计具有很好的参考价值。

[1]IEEE Stand Board.IEEE Std 1149.7.IEEE standard for reduced-pin and enhanced-functionality test access port and boundary- scan architecture[S].USA:IEEE Standard Board,2009.

[2]IEEE Stand Board.IEEE Std 1149.1 -2001.IEEE standard test access port and boundary-scan architecture[S].USA:IEEE Standard Board,2001.

[3]胡和娟.基于JTAG的SOC互连信号完整性测试系统的设计[D].桂林:桂林电子科技大学,2010.

[4]雷加,黄文君.基于 IEEE1149.7边界扫描技术的研究[D].桂林:桂林电子科技大学,2011.

[5]徐志磊.紧凑型JTAG接口的设计与验证[D].上海:上海交通大学,2010.

[6]陈光禹,潘中良.可测性设计技术[M].北京:电子工业出版社,1997.

Interconnected Signal Integrity Test Based on CJTAG

HUANG Fengcai,YAN Xuelong

(School of Electronic Engineering and Automation,Guilin University of Electronic Technology,Guilin 541004,China)

With the wide application of IP cores in the system on the chip,more and more interconnection bus has been used in the IP cores,leading to the problem of the signal dis-integrity.And the traditional serial scanning topology structure cannot satisfy the requirements of the development task of the test system.The IEEE 1149.1 standard proposed a TAP.7 interface standard that supports three topology structures.This paper gives a test method for the interconnected signal integrity based on CJTAG with emphasis on the design of the TAP.7 interface converter.Testing results show that this system has good application prospects.

serial scanning;CJTAG;TAP.7 interface;signal integrity

TN911.23

A

1007-7820(2012)08-026-03

2012-02-16

黄凤彩(1985—),女,硕士研究生。研究方向:计算机辅助设计。