SOC芯片的可测试性设计与功耗优化

2012-01-19陈志强林平分任威丽

陈志强,林平分,任威丽

(北京工业大学嵌入式系统重点实验室,北京 100022)

SOC芯片的可测试性设计与功耗优化

陈志强,林平分,任威丽

(北京工业大学嵌入式系统重点实验室,北京 100022)

介绍了数字集成电路可测试性设计与测试覆盖率的概念,针对一款电力网通信芯片完成了可测试性设计,从测试的覆盖率、功耗等方面提出了优化改进方案,切实提高了芯片的测试覆盖率,缩减了测试时间和成本,降低了测试功耗,同时保证了芯片测试的可靠性,最终使芯片顺利通过量产测试。

可测试性设计;低功耗设计;故障覆盖率

可测试性设计(DFT)是指在集成电路设计前期就考虑到测试的需求,在电路设计中增加有助于测试的电路。目前常用的DFT技术有扫描设计(Scan Design)、内建自测试(Build In Self-Test)、边界扫描设计(Boundary Scan Design)等。随着集成电路工艺的不断改进,芯片制造过程中引入故障的几率变高。同时,设计方法学的发展为测试带来了严峻的挑战。研究表明,晶体管数量和故障模型种类的增加使测试数据量急剧膨胀,以及越来越先进的低功耗设计和越来越高的工作频率给测试功耗带来苛刻的限制使可测试性设计成为数字集成电路设计的热点[1]。为应对以上的挑战,文中着重讨论在扫描设计中如何提高测试覆盖率并缩减测试时间,同时优化测试功耗提高测试稳定性。

1 扫描的原理和测试覆盖率

SOC芯片内部集成了数目众多的数字模拟以及存储器模块,但受限于数目较少的IO,直接对内部电路进行测试较为困难。所以业界通常采用扫描的方法,使内部电路变成可测试电路。具体做法是将芯片内部的寄存器用具有扫描功能的寄存器代替,使其在扫描测试模式下形成一个或多个移位寄存器链[2]。这使电路的所有状态均可直接从片外输入和输出端得到控制和观察,从而达到由外部充分测试内部电路的目的。

评价测试质量的好坏有两个标准,一是故障覆盖率的高低,二是测试向量集的大小。测试覆盖率是指测试向量能够检测出的故障占有数的比率[3],测试向量集是指达到设计的测试覆盖率所需要的向量集合,因而测试向量集的大小则直接影响到测试的时间与成本。在通常情况下,由于逻辑结构的原因在芯片首次进行扫描设计时覆盖率通常较低,这就需要通过分析逻辑结构,在芯片内部增加额外的测试电路来提高覆盖率。但额外增加的测试电路须保证不影响正常的逻辑功能,且不能破坏芯片正常工作的时序。文中提出的方法就是通过适当调整电路结构,增加测试的控制点和观测点来大幅度的提高测试覆盖率。

2 测试覆盖率的优化方法

在设计过程中,存在两种对测试覆盖率影响较大的情况:一是存储器输入输出的端口电路,二是测试模式下不工作的阴影逻辑。所有这些不可测试的电路有个共同特点就是在测试模式下不可控或不可观测。

2.1 存储器端口电路的优化

造成存储器端口电路测试覆盖率低的主要原因是在测试模式下存储器不工作,无法通过它来完成电路的控制与观测。一方面存储器的输入是直接由存储器控制逻辑给出,这一部分控制逻辑的输出无法在测试过程中直接输出到片外,造成不可观测。另一方面,存储器的输出在测试时是不确定状态,对于和存储器直接相连的后继电路而言,其得不到一个确定的输入值,因此该逻辑不可控。

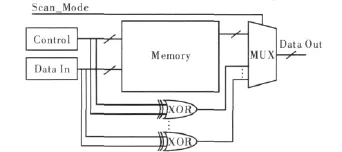

针对这一问题,解决方法是在存储器的外围增加一块额外的旁路电路。具体的方法是通过一个多路选择器,在正常工作下,存储器控制逻辑的输出接存储器的输入,存储器的输出接后继的电路。在测试情况下,存储器控制逻辑的输出通过选择电路直接输出到存储器后继的电路,从而完全将存储器旁路。

如图1所示,在正常情况下Scan_Mode为0,数据和控制信号输入给存储器,同时多路选择器的输出为正常的存储器数据输出。当芯片进入扫描模式时Scan_Mode为1,输入信号首先通过异或运算压缩成为与输出宽度相同的信号,接着使一信号通过多路选择器输出到存储器的后继电路,这就完成了对存储器的旁路,达到存储器前后两部分逻辑的可观测和可控性的要求。

图1 存储器旁路电路结构

2.2 阴影逻辑的优化

扫描模式下的阴影逻辑是指在扫描模式下由于电路的输入恒定,导致电路的输出也恒定为0或1,无法通过其他的输入来改变输出,从而无法测试这一逻辑。阴影逻辑产生的原因之一是芯片设计的过程中引入了多种工作模式,部分电路只能在一个特定模式下工作,而一旦芯片处于扫描模式时这些电路均处于不可观测或不可控状态,无法通过扫描链测试。

针对这一问题,解决方法是增加额外的模式控制逻辑,使阴影逻辑在扫描模式下也能工作,但同时新增逻辑不能影响其他工作模式。这种方法需要对ATPG测试故障进行分析归纳,找出影响覆盖率的关键控制点,然后增加控制逻辑进而提高芯片的测试覆盖率。

ATPG测试故障主要有已检测的故障(DT)、可能检测的故障(PT)、不可测的故障(UD)、无法测试的故障(AU)和无检测到的故障(ND)几类[4]。DT和PT占据故障的绝大部分,代表已检测到的故障和可能通过其他途径检测到的故障。UD代表现有测试向量无法覆盖的测试故障,如器件悬空的引脚。AU指工具在满足现有约束下无法覆盖的测试故障,通常是由于设计因素导致的,这其中就有较大部分是由固定状态造成的阴影逻辑,所以研究改进的重点就是该部分的故障。ND指受到时间和覆盖率约束的限制,ATPG工具还未能分析和处理的部分电路里包含的故障。

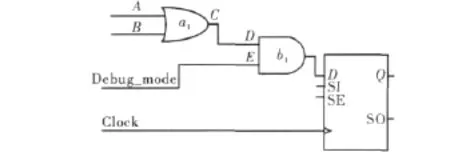

如图2所示,这是一个明显的AU错误。Debug_mode是在正常模式下用于调试芯片功能的模式配置信号,当芯片处于扫描模式时,其值恒为0。在分析ATPG故障的时候,工具会报出或门a1的A、B、C的故障不可测,类型是AU。很显然造成该部分故障不可测的原因是与门b1的输入端E恒为0,从而影响了所有通过D路径的故障观测。解决办法就是对Debug_mode信号加以控制,使之在扫描模式下恒为1,从而不影响由与门b1的D端经过的所有路径测试。

图2 ATPG不可测故障

如图3所示,在增加一个两路选择器和触发器组成的控制逻辑后,测试模式下b1的E直接受触发器控制,因而可通过改变测试数据来完成a1、b1及这条路径上所有相关的故障的测试。

图3 控制逻辑的加入

3 测试功耗的优化

在扫描测试过程中,当测试向量以移位的方式通过扫描链时,与扫描链上直接相连的功能逻辑也随之发生翻转,这将导致在这一过程中无谓的功耗损耗。且测试过程由于功能逻辑翻转的随机性,有可能在芯片内部的某一区域造成局部过热从而损坏芯片。

如图4所示,这一问题的处理方法是在触发器的Q端增加门控电路,使功能逻辑的输入在移位输入的模式下处于固定值。ScanEnable=1芯片处于移位输入模式,同此信号相连的与门输出则恒为0。对于组合逻辑,如果所有输入的信号全部固定,那么组合逻辑将处于稳定状态,动态功耗为0,从而达到优化目的。

图4 组合逻辑门控结构

在新版本的DFTCompiler中,工具已支持逻辑自动门控功能。按照用户需求,工具能分析出需要插入门控逻辑的电路节点,选择与门或者或门进行插入操作。使用的语法是:set_scan_support_togglin-selection_method auto。

这一方法对DFT设计工程师而言是方便和可靠的。随后文中将给出功能逻辑门控前后不同的功耗分析对比。

4 测试结果

文中设计的电力网通信芯片总共使用了5条扫描链,每条链的长度均是2 704。在进行芯片的物理设计时,按照触发器的物理位置对所有扫描链进行重组,以避免触发器之间过长的绕线距离。在扫描测试的覆盖率和功耗方面,文中优化的方案均在原设计基础上得到了较大提高。

4.1 覆盖率的改进

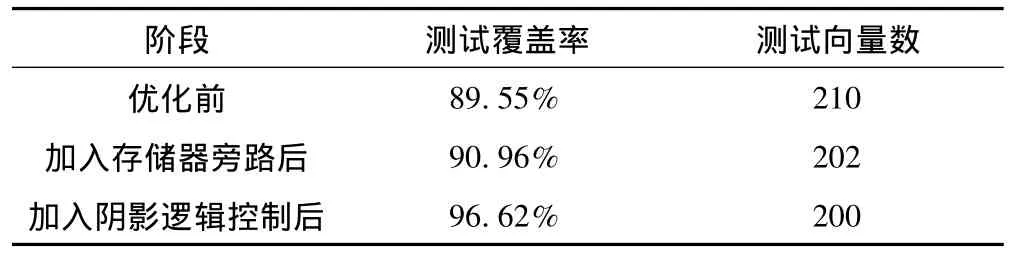

在使用存储器旁路电路和阴影逻辑控制电路后ATPG的覆盖率和测试的向量数明显发生了变化,具体对比结果如表1所示。

表1 优化前后覆盖率与向量数对比

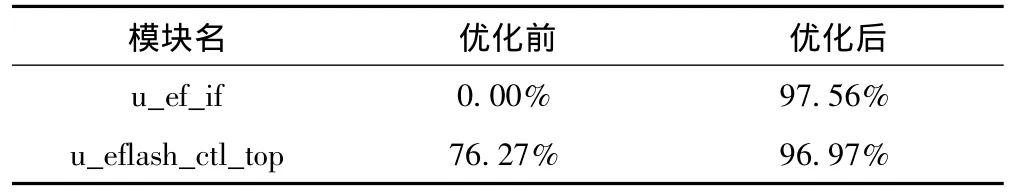

存储器旁路的优化中,文中通过添加嵌入式Flash单元的旁路逻辑,使Flash接口和控制模块的测试覆盖率大幅提升。模块的优化结果如表2所示,通过改进,使整体覆盖率提高了1.41%。

表2 Flash控制模块优化前后覆盖率对比

第二步阴影逻辑控制,其加入了若干内部状态控制点。其中控制mbist是否工作的test_h点对覆盖率影响最大。其原因是芯片中所包含的8块SRAM和一块ROM均做了mbist设计,这部分用于产生bist激励和比对输出结果的电路在扫描模式下都属于阴影逻辑。而通过控制test_h就使mbist电路在扫描模式时可观测,从而使整体的覆盖率大幅提升。

4.2 测试功耗的改进

通过门控结构的应用,扫描测试整体功耗得到降低,特别是扫描移位过程的功耗发生了大变化,具体结果如表3所示。

表3 优化前后功耗对比

结果表明在进行门控功耗优化后,移位模式的峰值功耗降为原来的77%,整体功耗降为原来的27%。进一步分析瞬态的功耗变化得到如图5所示的结果。

图5 优化前后瞬态功耗对比

图中可看到优化后的曲线峰值大约为优化前的11%。同时可以看出优化后的曲线在时钟翻转前后瞬时功耗衰减较快,但优化前曲线衰减速度较慢。说明在门控逻辑加入后,功能逻辑能在时钟停止时迅速达到稳定,从而保证较低的功率消耗。

5 结束语

介绍了SOC芯片可测性设计原理和覆盖率的概念,通过对一款电力网通信芯片的分析应用,完成了其可测试性设计同时提高测试的覆盖率,减少测试向量的数目,降低了测试的功耗和成本,同时提高了测试的稳定性和可靠性,最终通过量产的测试验证。

[1]李晓维,韩银和,胡瑜,等.数字集成电路测试优化[M].北京:科学出版社,2010.

[2]郭炜,魏继增,郭筝,等.SoC设计方法与实现[M].2版.北京:电子工业出版社,2011.

[3]余会星.数字电视解调芯片的可测试性设计与优化[J].微电子学与计算机,2008,25(8):172 -175.

[4]Synopsys Corpration.Tetra MAX ATPG user guide[M].USA:Synopsys Corpration,2010.

[5]曲利新.空间电子设备电路板可靠性可测试性设计检查[J].现代电子技术,2010(19):184 -186.

[6]王志林,于秀金,王永岭,等.边界扫描技术在故障信息处理中的应用[J].西安邮电学院学报,2010(3):53-56.

Design for Testability and Power Optimization in SOC

CHEN Zhiqiang,LIN Pingfen,REN Weili

(Beijing Embedded System Key Lab,Beijing University of Technology,Beijing 100022,China)

This paper introduces the conception of DFT(Design For Testability)technology and test coverage with a PLC(Power Line Communication)chip as an example.An obvious adjustment has been made based on test coverage and power of the design.These optimization methods have greatly improved test coverage,reduced the cost and power consumption,and improved DFT quality.Finally,the design went on to mass production successfully.

design for testability(DFT);low power design;test coverage

TN702

A

1007-7820(2012)08-023-03

2012-03-05

陈志强(1988—),男,硕士研究生。研究方向:集成电路后端设计与测试。