通用数字电路板测试系统硬件设计

2012-01-19刘文波

周 博,刘文波

(南京航空航天大学自动化学院,江苏南京 210016)

通用数字电路板测试系统硬件设计

周 博,刘文波

(南京航空航天大学自动化学院,江苏南京 210016)

针对传统依靠人工使用示波器、万用表、逻辑分析仪等设备对数字电路板进行测试具有过程复杂、工作量大、可靠性低等缺点,介绍一套通用数字电路板测试系统的硬件设计方案。跟传统数字电路板测试系统相比,文中的设计性能参数更优,主要包括:测试频率最高50 MHz并可调为100 MHz的整数分频;测试电平兼容-6~+9 V且可编程步长为100 mV;测试通道32路,每通道可设为输入输出三态可选且同步工作,存储深度1 Mbit,电流驱动能力达50 mA并有过载保护。

数字电路板测试;嵌入式硬件设计;FPGA

随着设计技术和制造能力的发展,实际应用系统中的数字电路规模越来越大,功能也日趋复杂[1]。测试是认识世界以取得定性或定量信息的基本方法,是信息工程的源头及组成部分,据资料显示,目前测试成本已达到所研制设备成本的50%、甚至70%[2]。传统的数字系统测试与诊断工作是工程技术人员凭借经验和理论知识,借助一些常规工具,比如万用表、示波器或逻辑分析仪来完成的,测试的速度慢、自动化程度低、可靠性不高,因此使用数字电路自动测试系统成了最佳选择。目前国内仪器、仪表公司和科研机构研制的数字电路板测试系统,价格昂贵,且各项性能指标都有提升的空间。比如北京新润泰思特测控技术有限公司的XR3168A大规模数字集成电路测试系统,主要支持TTL系列、CMOS系列等器件,测试通道数可达256通道,动态功能测试速率1.6 kHz~20 MHz,支持I/O引脚输入高、低电平,输出高、低电平,输出三态和输出屏蔽等格式。

文中针对市场上数字电路板测试系统在各项技术指标上所存在的不足,提出一套高性能、操作使用方便的通用数字电路板测试系统硬件设计方法。该测试系统的主要技术指标如下:测试通道数32路,每通道独立、可同步工作,可输出最大电流50 mA,均有短路保护,均可设置为输入或输出:设置为输入时,可检测低电平、高电平和不定状态;设置为输出时,可发送低电平、高电平和高阻态3种状态;测试电平范围为-6~9 V,可编程电平步长为100 mV;单通道存储深度最大为1 Mbit,测试频率最高达 50 MHz,并可设置为100 MHz的整数分频。

1 测试系统概述

文中介绍的是一套高性能、自动化、通用的数字电路板测试系统,可完成各种型号的数字电路板测试工作,方便对被测电路板进行故障分析与诊断,其系统总体结构如图1所示。

图1 数字电路板测试系统总体结构

上位机初始化测试电平、测试频率及测试通道数后,下位机将上位机发送的测试向量保存到发送缓存模块,通过发送调理电路连续地输出至被测数字电路板;被测电路板响应后,经接收调理电路保存至接收缓存模块,最后集中发往上位机供其分析。通过对比发送的测试向量与被测电路板的响应向量,可对被测电路板进行故障检测与分析。

2 测试系统硬件设计

2.1 系统电源设计

文中考虑实际工作环境里均使用220 V、50 Hz的交流电作为总电源输入且电源模块的体积不能太大,遂选取朝阳电源公司定制的轻系列开关电源,再通过线性电源稳压芯片对其输出进行稳压,减小输出纹波,以满足测试系统的电源需求。开关电源输出+18 V经Linear公司的LT1085-ADJ输出+14V为测试向量发送调理模块及接收调理模块正极电源,开关电源输出-15 V经Linear公司的LT1033输出-12 V为测试向量发送调理模块及接收调理模块负极电源,开关电源输出+7.5 V经Linear公司的LT1085-5输出+5 V为D/A等器件电源。

2.2 FPGA最小系统设计

FPGA有较大可编程灵活性及可移植性,用户可通过反复编程,使得在外围电路不改变的情况下用不同硬件描述语句实现不同的功能,这是DSP、ARM等嵌入式C处理器所不可匹敌的。文中选用Altera公司CycloneIII系列芯片EP3C25F324C8作为发送控制模块处理单元芯片,该FPGA芯片具有24 624个LE,4个PLL,608 256 bit Memory Block以及多达215个可编程IO口,内部资源满足本课题的应用需求[3]。选取Linear公司的LT1085-3.3提供3.3 V电源,可输出3 A电流,纹波在2%以内;选取AMS公司的AMS1117-2.5提供2.5 V电源,可输出0.8 A电流,纹波在1.6%以内;选取Sipex公司的SPX3819-1.2提供1.2 V电源,可输出0.5 A电流,纹波在2%以内。

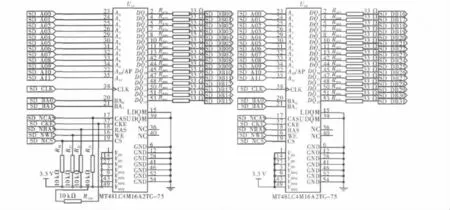

2.3 高速存储模块设计

测试向量发送与接收高速缓存选用单倍速率动态随机存储器即SDRAM,具有单位空间存储容量大、读写速度快以及价格便宜等优点。文中选用两片位宽为16位、容量为 64 Mbit的镁光公司 SDRAM产品MT48LC4M16A2TG-75组成容量为128 Mbit的存储单元,该芯片读写时钟频率可达133 MHz,满足设计指标每通道测试存储深度达1 Mbit的需求,其电路连接如图2所示。

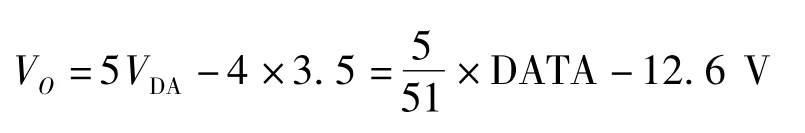

2.4 测试电平调节电路设计

测试电平调节电路的为发送调理模块提供发送参考电平以及为接收调理模块提供比较参考电平,由D/A转换电路与偏置放大电路组成。选用 Analog Devices公司 8位、8通道低功耗 D/A转换芯片AD8801[4]及单片四通道运放 OP482,原理如图 3所示。其中VREF为高精度稳压芯片TL431输出3.15 V,R3与C1组成低通滤波电路滤除高频噪声,输出电压VO连至发送驱动芯片的VL、VH及接收比较芯片的-IN1、-IN2端,通过编程 D/A转换的数字量 DATA改变VDA,可得到-12.6~+12.4 V范围电平,分辨率为100 mV,具体计算方法如下式:

图2 SDRAM位宽扩展电路

图3 电平调节原理

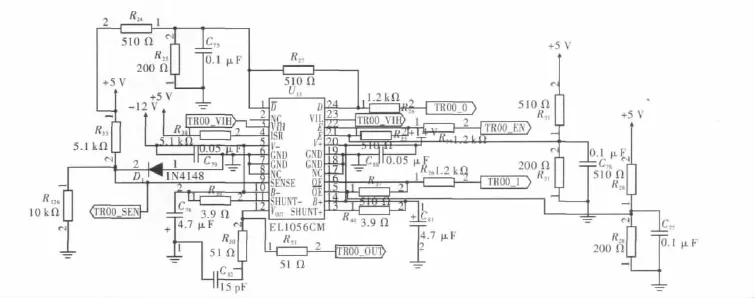

2.5 发送驱动电路设计

测试向量发送驱动电路实现对测试向量的调理,将从发送控制模块即FPGA的IO发出的测试向量电平转换成测试系统需要的-6~+9 V电平及高阻输出,提高电流驱动能力。为保证测试频率、电平范围及驱动能力,文中采用Intersil公司的高性能管脚驱动芯片EL1056为发送驱动芯片,可输出电平范围-12~+12 V,频率达66 MHz,峰值驱动电流达140 mA,并具有短路保护功能[5],发送驱动电路如图4所示。

图4 发送驱动器EL1056电路

每路测试通道占用发送控制模块即FPGA的4个IO口,分别连至发送驱动芯片EL1056的数据脚D、低优先级使能脚OE、高优先级使能脚E以及芯片过载保护指示脚SENSE。要实现发送3种状态,每个通道需用两位并行数据表示,假设为 test_vec[1:0]:test_vec[1]为高位,接EL1056低优先级使能脚OE;test_vec[0]为低位,接EL1056数据脚D。测试时先进行初始化,通过对D/A编程设置EL1056的3脚VH及23脚VL的电压值。当 test_vec[1:0]=‘10’时,EL1056 输出低电平,电压为VL;当 test_vec[1:0]=‘11’时,EL1056 输出高电平,电压值为 VH;当 test_vec[1:0]=‘00’或‘01’时,EL1056输出高阻态。其实现测试向量三态输出。利用FPGA实时监控EL1056的SENSE脚电平,其跳变为低电平时,将高优先级使能脚E置为低电平将EL1056输出高阻,从而实现发送驱动的过载保护。

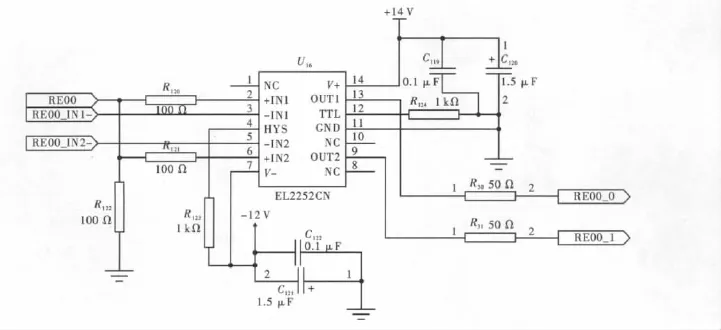

2.6 接收比较电路设计

测试向量接收比较电路实现对被测数字电路板响应向量的比较,将从被测电路板接收到的响应向量电平转换成与接收控制模块即FPGA的IO口相兼容的电平并对其进行判断。考虑被测电路板的响应频率及电平范围,文中采用Intersil公司的EL2252作为接收比较芯片,该芯片上集成两路独立的比较器,可比较频率达50 MHz、电平范围为 -12 ~ +12 V 的信号[6],如图5所示。

图5 接收比较器EL2252电路

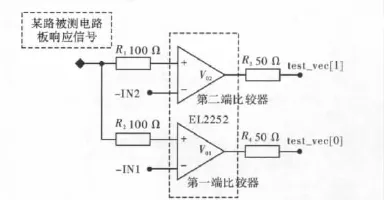

为检测被测电路板响应向量的状态,将响应信号接至两路比较器的正端,与两路比较器的负端进行对比,所得数据需两位并行数据表示,设为 test_vec[1:0]:test_vec[1]为高位,接 EL2252 第二端比较器输出脚;test_vec[0]为低位,接EL2252第一端比较器输出脚,接收原理方框图如图6所示。测试时先进行初始化,通过对D/A编程设置EL2252的3脚-IN1及5脚-IN2的电压。当检测到 test_vec[1:0]=‘11’时,接收到的状态判定为高电平;当test_vec[1:0]=‘00’时,接收到的状态判定为低电平;当 test_vec[1:0]=‘01’时,接收到的状态判定为不定状态,通常将此状态定为故障状态;test_vec[1:0]不可能出现‘10’的状态。双端比较器的输出即test_vec[1:0]连至FPGA的IO口,通过检测IO口的电平可实现被测电路板响应向量3种状态检测[7-8]。

图6 接收比较原理框图

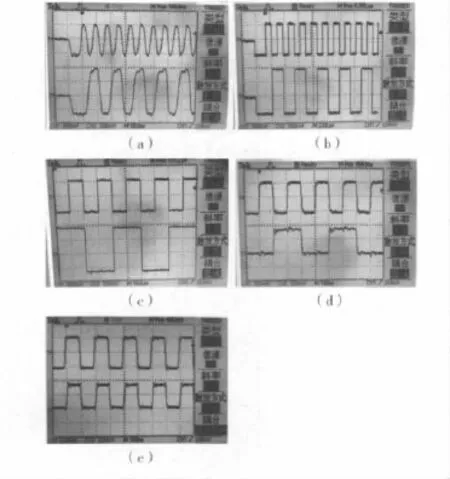

3 测试结果分析

数字电路板测试系统作为一种测试仪器,其是否能实现提出的性能指标设计要求以及稳定地运行,调试和验证是重要环节。文中使用Verilog HDL对FPGA进行电路描述,编写测试程序对系统指标进行验证。使用边沿触发方式观察到测试向量输出结果如图7所示,其中图7(a)中1通道为50 MHz测试频率+5 V、-5 V方波,2通道为25 MHz,+9 V、-6 V方波;图7(b)和图7(c)是(a)中测试向量频率调为1 MHz、500 kHz、100 kHz、50 kHz的波形;图 7(d)2 通道为输出LVTTL电平方波;图7(e)1通道为10 MHz测试频率+5 V、-5 V方波,2通道为接收比较后的波形。无论数字电路的功能有多复杂,都可施加二值逻辑即一串连续的“0”和“1”组成的数字序列来测试。从以上波形可看出文中介绍的测试系统发送的测试向量电平、频率均满足预期要求,对被测电路板的响应也能正确接收。

图7 测试向量输出结果

4 结束语

文中针对某航修单位的应用需求,介绍一种可对军用数字电路板在内进行测试的高性能、通用数字电路板测试系统的硬件设计方案,核心处理系统采用FPGA+两片SDRAM方案实现,解决了传统数字电路测试系统灵活性低、存储深度小、测试速度慢等问题。该系统可按操作人员的要求发送测试波形至被测电路板,接收其响应后存储并上传到上位机供操作人员分析处理,其可以迅速判断被测电路板的性能是否正常并定位故障位置,达到事半功倍的效果,具有广阔的应用前景。

[1]贺喆,周剑奇,马好东.基于PXI总线的小型化数字电路故障诊断系统设计方法研究[J].计算机测量与控制,2010,18(2):323 -325.

[2]郭希维,苏群星,谷宏强.数字电路测试中的关键技术研究[J].科学技术与工程,2006,6(18):2903 -2905.

[3]Altera,Inc.Cyclone III device handbook[M].CA,USA:Altera,Inc,2010.

[4]Analog Devices,Inc.Octal 8 - bit trimDAC with power shutdown,AD8801[M].Ultra,USA:Analog Devices,Inc,2002.

[5]Intersil,Inc.Monolithic high - speed pin driver[M].UK:Intersil,Inc,2007.

[6]Intersil,Inc.Dual 50MHz comparator/pin receiver[M].UK:Intersil,Inc,2007.

[7]黄鑫,常天庆,邢士勇,等.数字电路板自动测试与故障诊断系统的设计与实现[J].计算机测量与控制,2010,18(7):1512-1514.

[8]谢涛,何怡刚,侯玉宝,等.模拟数字电路故障诊断新方法[J].半导体技术,2007,32(7):558-561.

Hardware Design of a General Digital Circuit Board Testing System

ZHOU Bo,LIU Wenbo

(College of Automation Engineering,Nanjing University of Aeronautics and Astronautics,Nanjing 210016,China)

The conventional method of using an oscilloscope,multimeter,logic analyzer or other equipment for digital circuit board testing is complex,time consuming and not reliable.In this paper,the hardware design of a general digital circuit board testing system is introduced.Unlike traditional digital circuit board testing systems,this design has better performance and parameters:the testing frequency can reach 50 MHz and can be set as integer division of 100 MHz;the testing level is compatible to-6 V~+9 V and can be programmed by 100 mV;there are up to 32 channels,each channel having 1 Mbit memory depth and 50 mA current drive capability with overload protection,and can work either as input or output for three-state synchronously.

digital circuit board testing;embedded hardware design;FPGA

TN79

A

1007-7820(2012)06-110-05

2011-12-08

周博(1988—),男,硕士研究生。研究方向:计算机测控。刘文波(1969—),女,教授,博士生导师。研究方向:信号处理及应用,非线性动力系统分析及工程应用,计算机测试与控制技。