高稳定度锁相环设计

2012-01-13

一、引言

本文介绍一种高稳定度和相位噪声的锁相环设计,适用于对频率源指标要求较高,锁定时间要求较低的场合,而且相对于单个高稳定度和相位噪声的频率源来说成本较低。

锁相环电路是一种以消除频率误差为目的的反馈控制电路,它的基本原理是利用相位误差电压取消除频率误差,所以当电路达到平衡之后,虽然有剩余相位误差存在,但频率误差可以降低到零,从而实现无频差的频率跟踪和相位跟踪。而且锁相环电路还具有科研不用电感线圈、易于集成化、性能优越等许多有点,因此广泛用于通信、雷达、制导、导航、仪表和电机都方面。

图1是一个锁相环的构成框图,PLL电路基本上由下述三大部分组成:

鉴相器(phase Detector或phase Comparator)鉴相器用于检测两个输入信号的相位差;环路滤波器(loop Filter)是将鉴相器输出含有纹波的电流信号平均化,将此变换为交流成分少的直流信号的低通滤波器。环路滤波器除滤除纹波功能外,还有一种重要作用,即决定稳定进行PLL环路控制的传输特性;压控振荡器(Voltage Controlled Osillator)就是用输入直流信号控制振荡频率,他是一种可变频率振荡器。

随着电子技术的发展,要求信号的频率越来越稳定,一般的振荡器已经不能满足要求,于是出现了高准确度和高稳定度的时钟振荡源。但是高稳定度的时钟振荡源价格比较昂贵,对于成本的节约上有很大的限制。于是利用锁相环技术产生高精度高稳定度的频率源应运而生,只需要一个成本不高的时钟源和一个高稳晶振就可以实现高精度和高稳定度的时钟频率输出,图2是一个高稳定度锁相环的框图电路。

二、电路框图

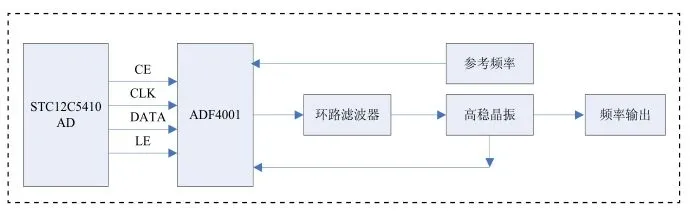

本文利用的是单片机STC12C5410AD和鉴相器芯片ADF4001以及一个高稳压控晶振实现锁相环电路,电路框图如图3所示。

1.器件选择

单片机用普通的单片机即可,本设计使用的是STC系列单片机,也可以使用51系列的单片机;ADF4001是AD公司的一款鉴相器芯片,最大输出频率可到200MHz,它内部含有一个13位、一个14位的分频器,可以对输入频率进行分频,使鉴相频率一致;高稳定度的压控晶振可以自己选择,适合自己要求的,表1是我们自己选择的恒温晶振部分指标。

2.环路设计

环路滤波器的设计是锁相环的重点,它决定了锁相环的指标好坏。环路滤波器的设计关键在环路带宽上,环路带宽会影响锁定时间、相位噪声和短稳等指标。环路带宽与锁定时间成反比关系;大于环路带宽部分的相位噪声由晶振决定,小于环路带宽部分的相位噪声由参考信号决定。环路滤波器的设计方法比较多,各有优势,下面是本设计采用的参数计算方法,环路带宽设置为0.5Hz、相位裕度45°,鉴相频率100kHz。采用三阶无源滤波器。图4是我们的三阶无源滤波器电路。

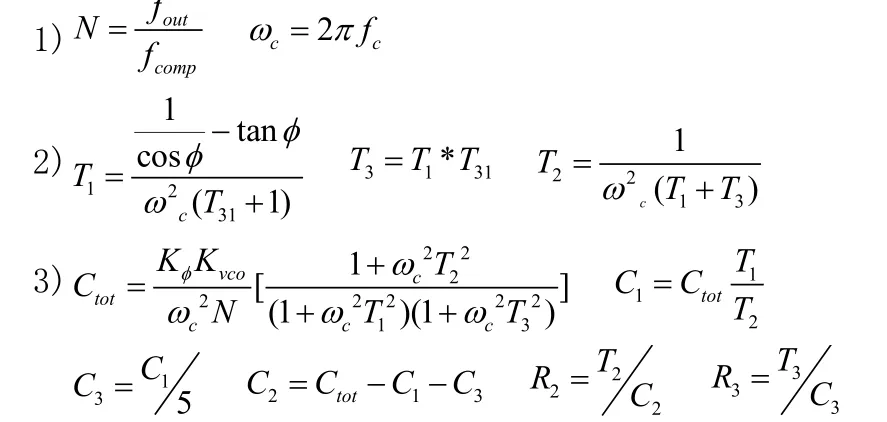

首先已知相位裕度φ、参考频率fc、鉴相频率fcomp、压控灵敏度Kv、鉴相灵敏度Kφ、输出频率fout、时间常数T31(取0到1之间)。

根据以上公式和已知条件,即可计算除电路中各个元器件的值。当然这只是一种环路滤波器的计算方法,也可以使用AD公司提供的ADIsimPLL软件进行计算,各有优缺点。

一般环路滤波器首选无源滤波器,因为无源滤波器相对于有源滤波器来说,引入的相位噪声更小一点。除非压控电压超出了无源滤波器的输出电压范围,我们才选择有源滤波器。

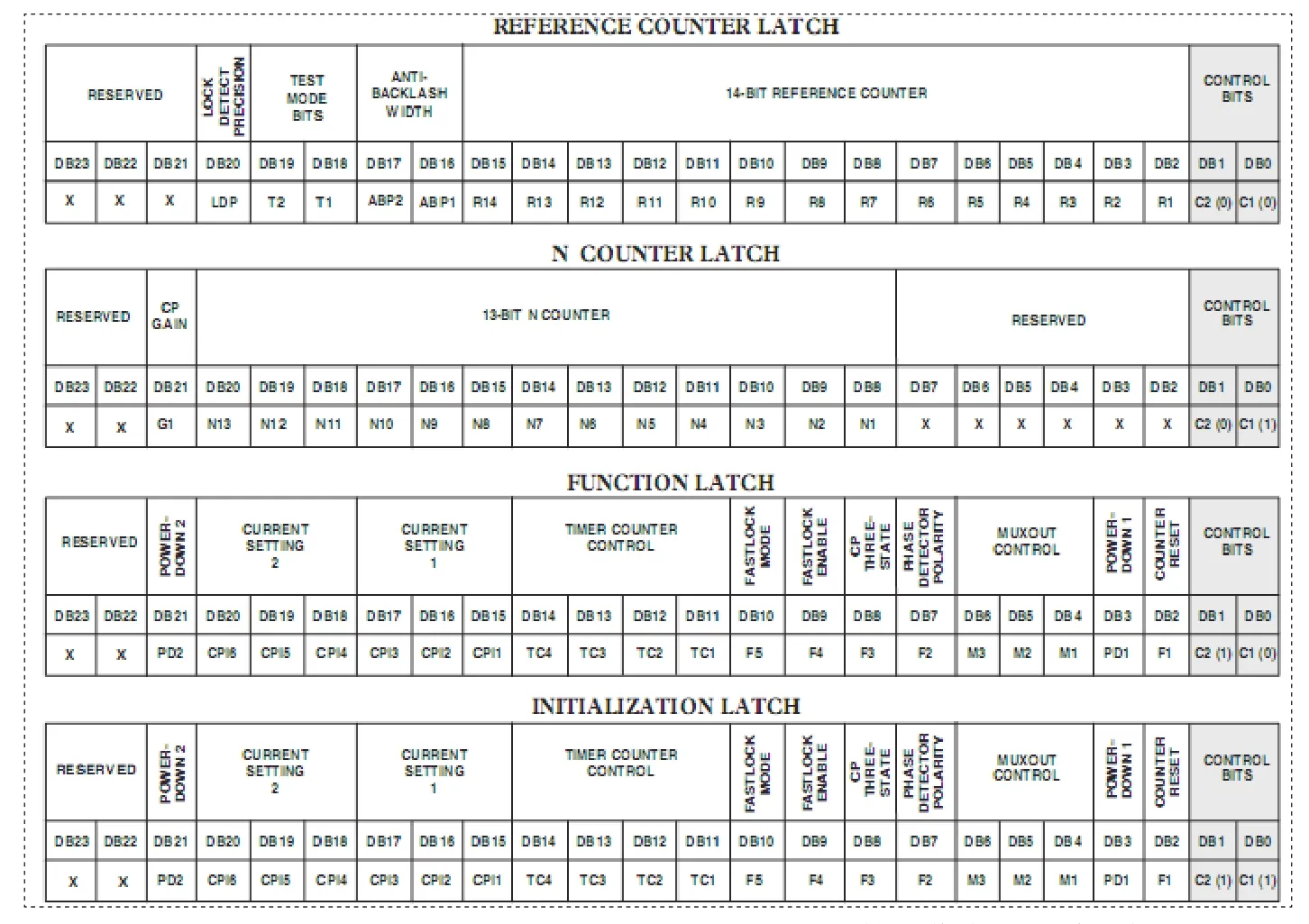

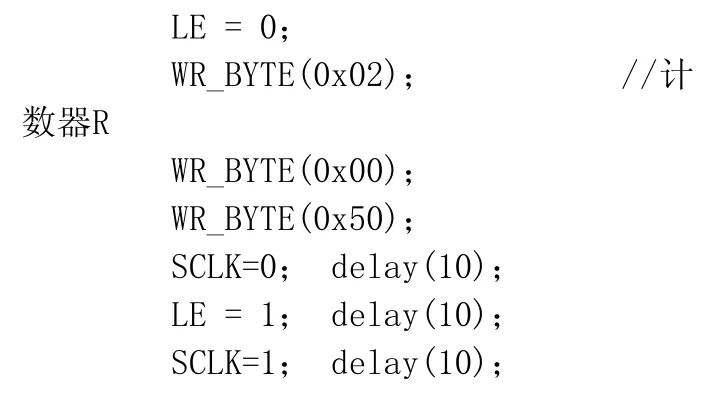

3.软件部分

表2是ADF4001内部寄存器设置图表。

根据寄存器配置表所写的程序如下

表1 高稳晶振指标

表2 测试结果

图1 PLL电路/频率合成器构成

图2 高稳定度锁相环框图电路

图3 高精度锁相环电路框图

图4 三阶无源滤波器电路

图5 vco输出功率分配电路

表2 ADF4001内部寄存器设置图表

4.注意问题

(1)电源

因为我们使用的是高灵敏度的压控晶振,对电压特别敏感,所以在处理电源滤波上要非常到位,特别是ADF4001的供电电压必须适用稳定度高的稳压器,因为供电电压直接影响器件内部电荷泵的电流,从而影响环路输出电压,导致晶振输出稳定度变差。我们在鉴相器电源引脚一次放置0.1uF、0.01uF、100pF的电容,最大限度滤除电源线上的干扰。还在电源线上串一个小电阻,进一步对噪声进行隔离。

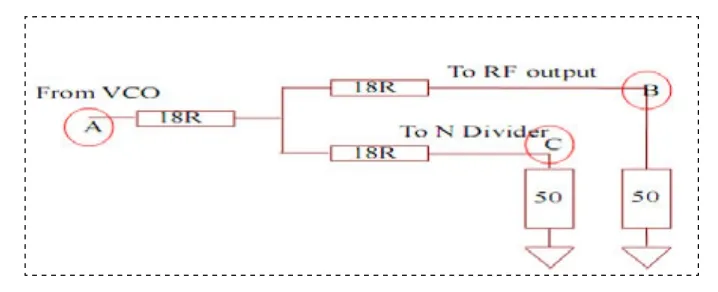

(2)VCO的输出功率分配

VCO的输出通过一个简单的电阻网络,将各个端口匹配到50欧姆,如图所示,利用三个18欧姆的电阻组成的T型网络完成。这样做会使B点和C点的功率比A点的功率低6dB,设计中应该注意。图5是输出功率的电阻分配图。

总之,要取得良好的相位噪声和短稳,要在各个方面进行改进,还应该注意以下的问题:

1)PLL芯片工作的电源纹波足够低——不会恶化噪声基底

2)PLL芯片的RF反馈输入(VCO的输出)具有合适的驱动能力——不容许计数器错误计数

3)PLL芯片的REF参考输入具有合适的驱动能力——不容许计数器错误。

4)PLL环路滤波器的电阻不会增加任何额外噪声——不高于热噪声

5)VCO的工作电压纹波足够小——不会恶化由于频率牵引引起的相位噪声。

6)环路滤波器屏蔽足够好——VCO控制线上不会串入其他干扰信号,防止来源于数字电路的窄脉冲信号出现在滤波器的输入端并直接耦合到输出端。

三、测试结果

经过不断的调试,测试结果如表2

由测试结果科研看出,经过锁相环之后,稳定度和相位噪声的指标跟晶振的指标基本一致,改善了时钟源的指标。

四、结束语

本文所设计的高稳定度和相位噪声的锁相环设计,适用于对频率源指标要求较高,锁定时间要求较低的场合,而且相对于单个高稳定度和相位噪声的频率源来说成本较低。由于本人水平有限以及研究场合等因素制约,难免会存在一些瑕疵,仍需近深入研究,来实现进一步的完善和提高。

[1]姜艳波,等编著.稳态电路与锁相环电路实例——CMOS数字集成电路应用百例[M].化学工业出版社,2009-05.

[2]黄智伟.锁相环与频率合成器电路设计[M].西安电子科技大学出版社,2008-10.

[3]F.M.Gardner,Phaselock Techniques,2nd ed.,Wiley,New York,1979.