一种卫星数传分系统链路数据异常分析

2011-12-26陈建光周希侠

陈建光 向 前 朱 丹 周希侠

(上海航天测控通信研究所,上海 201109)

1 引言

某卫星数传分系统在轨测试初期发现数传分系统延时云图发射机(DPT)链路偶尔有个别轨道数据接收异常现象。在轨卫星数传分系统固态存储器工作温度在0℃左右,DPT 工作温度在10℃左右,出现数据异常时,整个跟踪轨道接收数据均异常,这种数据异常现象在其他地面接收站接收时都出现过,最后通过采取卫星温控系统加热和数传发射机提前开机措施后,数传系统单机工作温度有所提高,DPT数传链路这种数据接收异常现象消失。为防止后续卫星数传系统出现重复问题,本文对该型号卫星数传链路问题进行了分析研究,并通过地面试验模拟问题复现、电路改进、试验验证等一系列措施,最终提高了产品的环境适应能力和系统的可靠性。

2 数传链路数据异常问题分析

观察地面站接收信号频谱[1]以及其他射频指标正常,从云图显示上看,不能看出云图信息,只有不规则的横条和麻点,对地面站接收数据进行事后分析,出错数据帧头、虚拟信道标识号(VCID)、帧计数错误较多,数据出错位置毫无规律,用高速率数据接收机(HDR)测试观察,异常现象表现为接收数据大量丢帧、帧同步有失锁现象、接收码速率相对于标准的124M bit/s 偏移达到10kHz 以上,这种数据异常现象在其他地面接收站都曾出现。综合以上现象可以分析得出,数传分系统DPT 数传发射机的信道编码(3/4,7卷积编码)、信号调制、调制信号功率放大等都没有问题。固态存储器(SS R)存储的数据没有问题,因为存入固存的数据是由数传系统信息处理器提供,信息处理器输出的带有帧格式的数据是通过其他数传链路下传的,地面站接收正常。因此,问题出在固态存储器和数传发射机之间的数据时钟接口部分,固态存储器是以1 路时钟加8 路并行数据的方式传送给数传发射机。从HDR 接收机显示的码速率偏差10kHz 以上的情况进一步判断,数传发射机中93MHz时钟晶振锁相环(PLL)[2]发生了失锁现象。

3 时钟锁相环晶振电路失锁分析

3.1 时钟锁相环晶振电路组成和工作原理

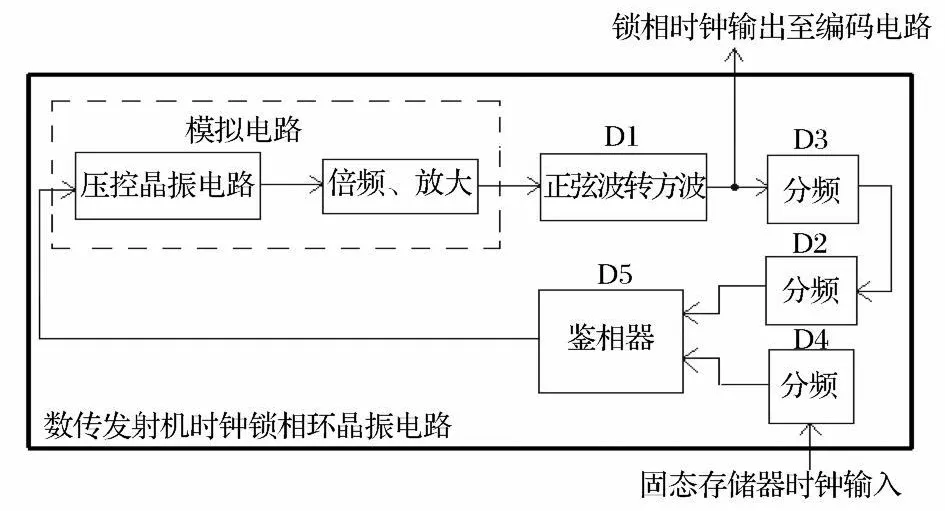

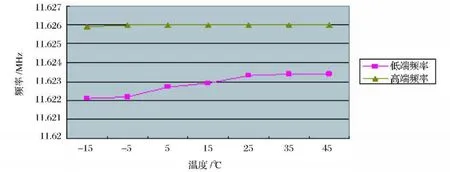

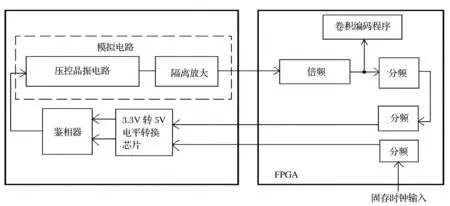

DPT 数传发射机93M Hz时钟锁相环晶振电路[3-4]由输入时钟(固态存储器送至DPT 数传发射机)2分频电路、压控晶振电路、2倍频和放大电路、16分频电路和鉴相器[5]电路等组成。93M Hz时钟锁相环晶振电路组成如图1所示。

图1 93M Hz时钟锁相环晶振电路组成图Fig.1 Block diagram of the 93M Hz PLL

压控晶体产生的46.5M Hz 的正弦波信号,经过2倍频、放大后得到93M Hz 的正弦波信号,再将正弦波转成93M Hz 方波信号,93M Hz 方波信号一路输出给数据编码电路使用,作为发射机内部时钟信号,另一路进行16分频后与外部输入11.625M Hz时钟(固态存储器输出时钟信号)的2分频信号进行鉴相,如此来保证DPT 数传发射机中信道编码电路用93M Hz 方波信号与固态存储器输入11.625M Hz时钟信号同步对齐。

3.2 时钟锁相环晶振电路失锁问题分析

考虑造成DPT 数传发射机93M Hz时钟锁相环晶振电路失锁有两种可能:

1)固态存储器输出到DPT 的11.625MHz时钟频率发生较大偏差,超出数传发射机可以锁定的时钟频率范围。

固态存储器采用的晶振是MM DC-Tech 公司生产的军用抗辐级晶振WO50AV11.625 000M Hz,工作温度在-55℃~+125℃之间,频率稳定度在1×10-4~1×10-5[6]。

为进一步掌握该器件的性能,将同一批晶振选择2 片进行了0℃、5℃和10℃(固态存储器在星上实际工作环境温度0℃~10℃)的标准测试和电压拉偏测试以及0℃的24h 以上的频率漂移测试,测试结果良好,频率偏差不超过0.2kHz;进行晶振带负载0℃、5℃和10℃的标准测试和电压拉偏±10%测试以及0℃的24h 频率漂移测试,结果频率偏差也不超过0.2kHz,符合要求。

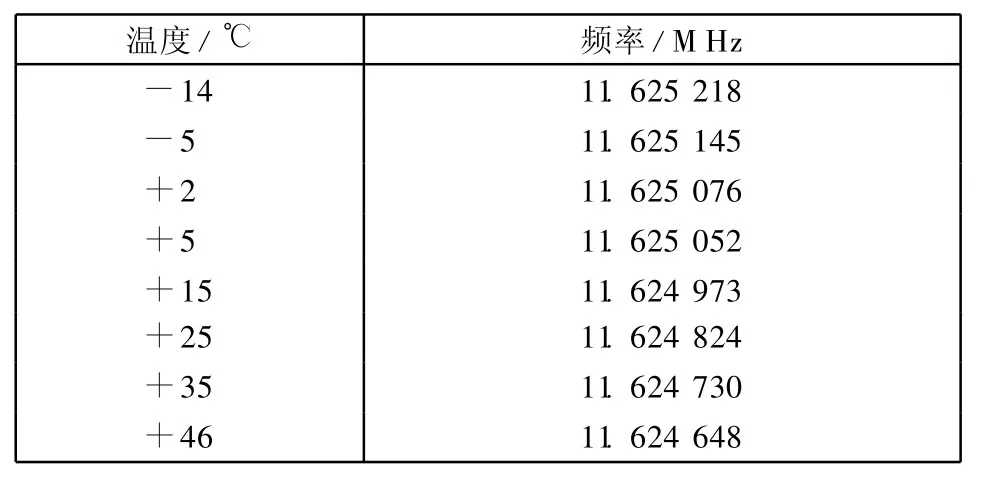

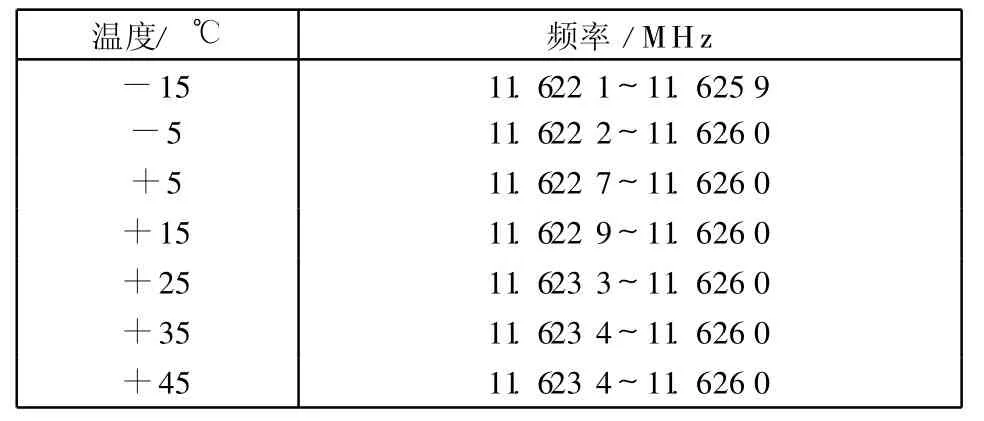

为了进一步排查问题,固态存储器进行单机自检测试以及与DPT 数传发射机连接进行系统测试,固态存储器输出11.625M Hz 的标准值偏差不超过±0.2kHz;将固态存储器初样单机上的晶振更换为正样单机所用的同批次11.625M Hz 晶振,固态存储器单机置于真空罐内与DPT 发射机进行联试,并用频率计数器实时监测频率变化,固态存储器在真空-15℃~+45℃温度范围内输出时钟频率变化情况见表1。

表1 固态存储器输出时钟频率Table1 Output frequency of the SSR

由上述测试数据可以初步得出,固态存储器输出11.625 M Hz时钟频率随温度的变化关系是高温时输出频率偏低,低温时输出频率偏高。在低温-14℃时,频率偏差为+0.218 kHz;在高温+46℃时,频率偏差为-0.352kHz。

固态存储器输出时钟频率随温度变化对应曲线如图2所示。

图2 固态记录器输出时钟频率与温度对应曲线图Fig.2 Output f requency of the SS R at different temperature points

由上述分析和试验测试结果可以看出,固态存储器输出时钟频率变化正常,问题发生在固态存储器输出频率偏差较大的可能性较小,但仍不能完全排除发生问题的可能性,该类晶振的频率稳定度指标最大可能至1×10-4,所以对固态存储器内部时钟晶振应加强环境试验考核。

2)DPT 数传发射机93M Hz时钟锁相环晶振电路出现问题,造成环路失锁。

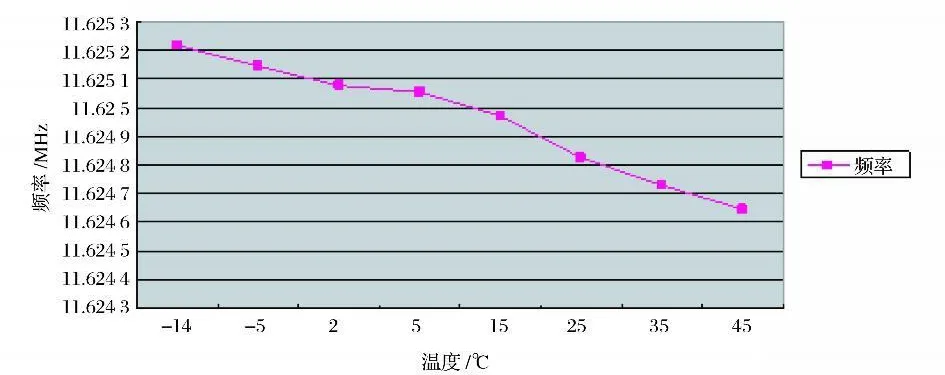

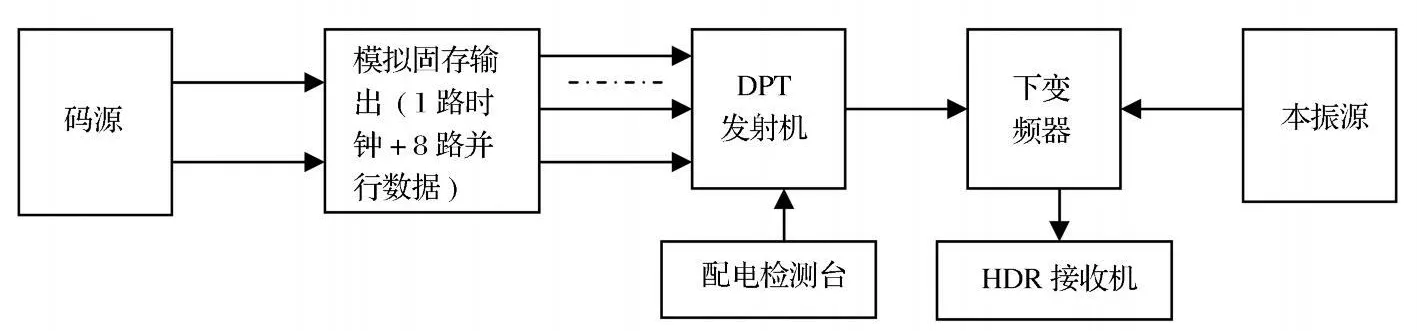

用5台DPT 发射机分别做不同温度下的时钟锁定试验,其中4台工作正常,1台单机在高温45℃以上出现时钟失锁现象。另外,对DPT 数传发射机时钟锁定频率范围变化进行试验摸底。连接测试如图3所示。

图3 DPT时钟锁定频率范围变化测试框图Fig.3 Testing sketch of the DPT PLL frequency lock range

码源设置输出速率为93Mbit/s,PN23 的伪随机码,且传输速率可以1kbit/s 步进调整。通过8路分路输入到DPT ,通过HDR 进行PN 23 伪随机码比对。在-15℃~+45℃温度变化范围选择多个测试温度点,以93M bit/s为中心频率、以1kbit/s步进上下调整码源输出频率,直到HDR 接收对比数据有误码出现,记录此时的码源输出频率,得到DPT 锁定时钟频率范围。测试记录如表2所示。

DPT 锁定时钟频率范围与温度对应曲线如图4所示。

图4 DPT时钟锁定频率范围对应曲线图Fig.4 DPT PLL locked f requency at different temperature points

表2 DPT 发射机时钟锁定频率范围Table2 DPT transmitter PLL frequency lock range

由上述测试数据看出,DPT时钟锁定时,在低温-15℃时允许的频率偏差范围为:+0.9kHz~-2.9kHz,在高温+45℃时,允许的频率偏差范围为:+1kHz~-1.6kHz。随着环境温度由低到高,时钟锁定频率范围逐渐缩小。

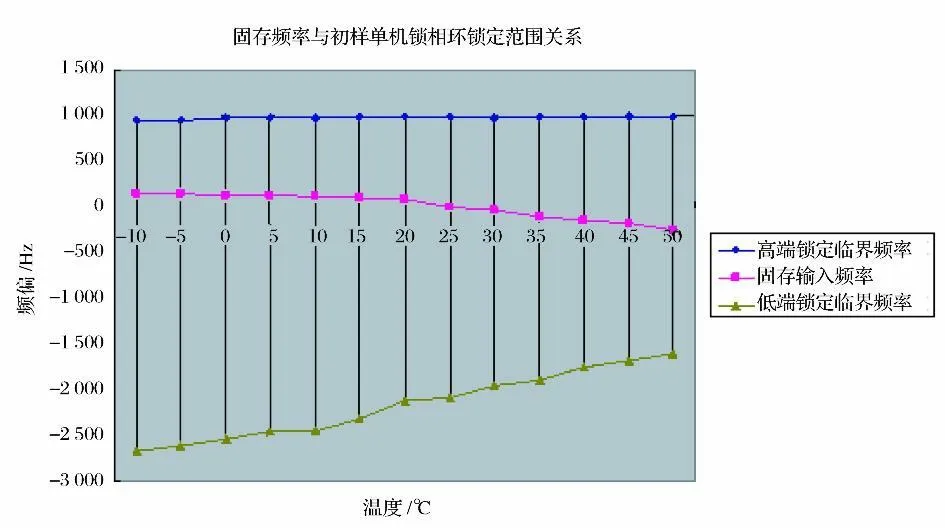

全温度范围内固态存储器输出时钟的频偏(相对于标准11.625M Hz)与DPT 发射机锁相环锁定允许频差变化曲线如图5所示。

图5 DPT 锁相环时钟锁定范围与固态存储器输入时钟频率随温度变化曲线Fig.5 DPT PLL frequency lock range and SSR frequency at different temperature points

由图5可以看出,在-10℃~+50℃全温度范围内,固态存储器时钟频率都在DPT时钟锁定范围之内,且有一定余量。

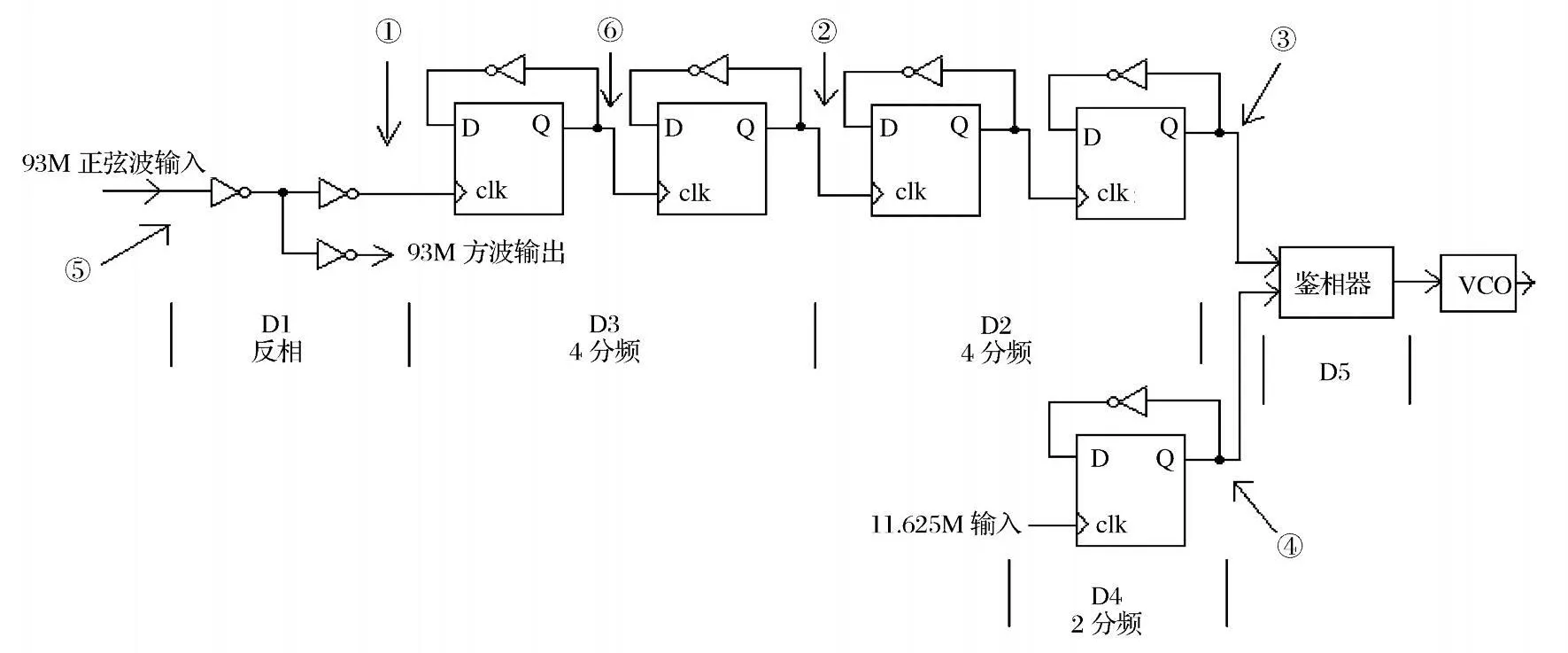

1台初样DPT 的93M Hz时钟锁相环在高温下试验出现失锁现象,用示波器监测高温失锁单机锁相环内部电路信号,监测点①②③④⑤⑥如图6所示。

图6 锁相环示波器测试点图Fig.6 Testing points of the DPT PLL with Oscilloscope

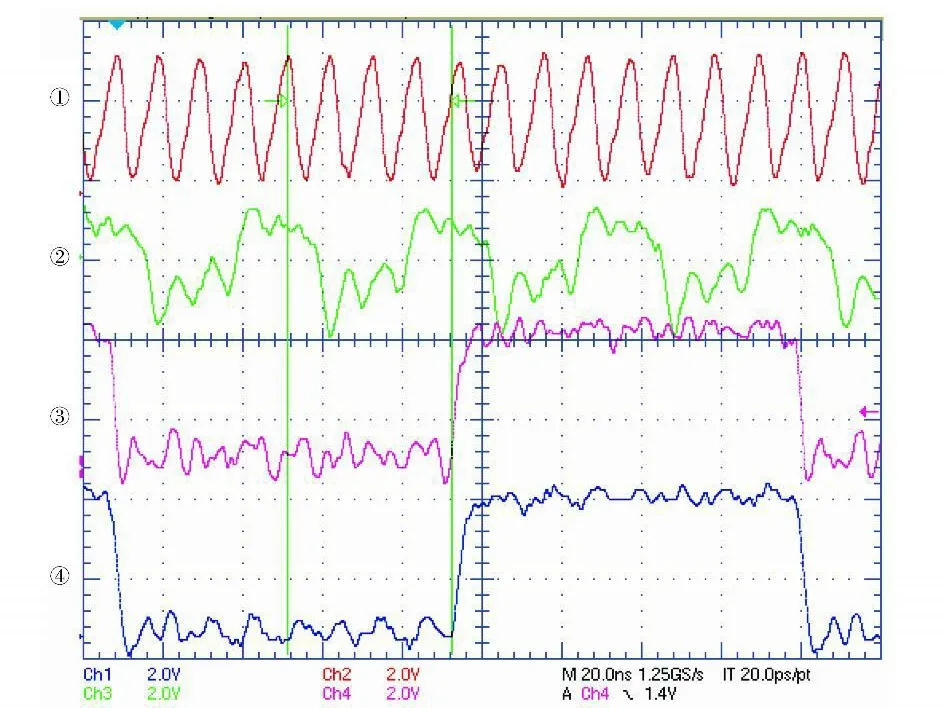

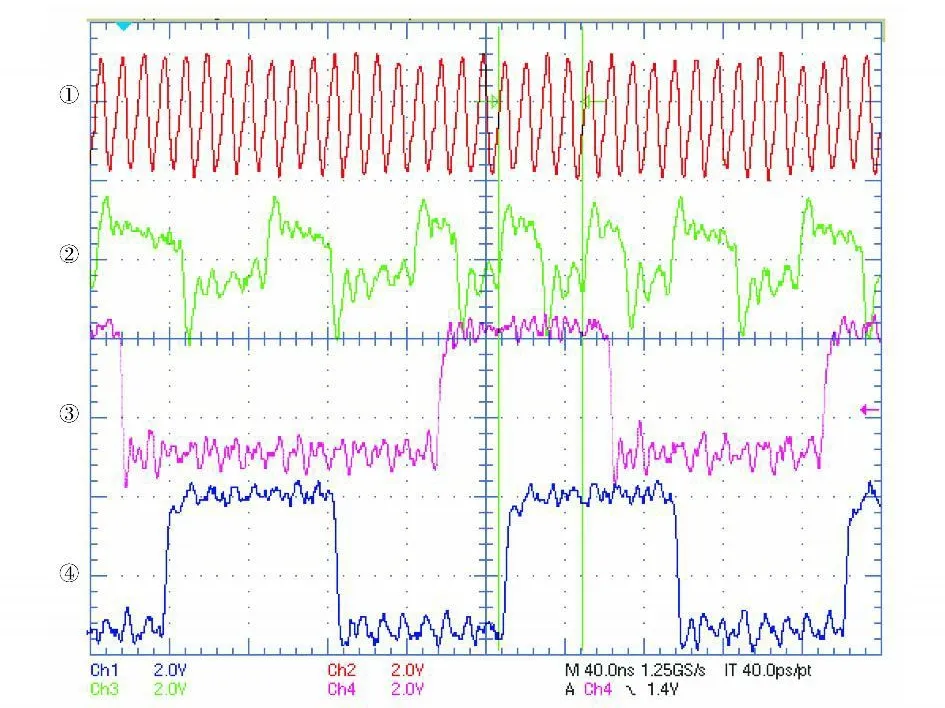

锁相环在常温下锁定时,图6中测试点①②③ ④的波形正常同步,波形依次如图7,测试点①的波形是93M Hz时钟信号,测试点②的波形是93M Hz时钟信号的4分频信号,测试点③的波形是93M Hz时钟信号的16分频信号。测试点④的波形是11.625M Hz时钟信号的2分频信号。

图7 各测试点正常波形图Fig.7 Normal waveforms of testing points on oscilloscope

在高温+45℃以上,锁相环失锁时,观测到鉴相器输入波形③和④不能同步锁定,且周期也不一样。此时,测试点②的波形信号同时有4分频和6分频存在时,测试点③输出波形是测试点②的4分频信号正常,如图8所示。

图8 测试点波形图Fig.8 Waveforms of testing points on oscilloscope

通过试验发现,DPT 数传发射机的时钟锁相环失锁,问题主要出在位号D3 的54S74 芯片的第一个2分频电路。测试点⑥处的波形由正常时①处波形的2分频变成了3分频。

分析其中机理,DPT 数传发射机时钟锁相环内位号为D3 的54S74 芯片(93MHz时钟的2分频)在某温度条件下产生了3分频的错误时钟,而产生错误时钟是由于54S74分频器芯片的实际工作频率93MHz 已经接近器件110M Hz 极限工作频率[7],从而造成时钟锁相环失锁。时钟锁相环的失锁导致DPT 数传发射机用不同步的93M Hz时钟信号对固态存储器送来的8 路并行输入数据进行采数,在数据时钟接口处直接造成采数出错,固态存储器输出的是具有帧格式的数据,数传发射机信道编码电路对错误的数据进行了卷积编码处理,因此,地面接收站接收处理的数据出现异常现象。

此故障现象与卫星数传分系统在轨飞行初期测试偶尔出现的数据异常现象吻合。

4 时钟锁相环晶振电路设计改进及试验验证

4.1 时钟锁相环晶振电路改进

利用DPT 数传发射机原有卷积编码的高速现场可编程门阵列(FPGA)芯片[8-9]将54S04 和54S74芯片替换掉,完成正弦波转方波和时钟分频的功能,改进后的93M Hz时钟锁相环晶振电路方案如图9所示。

经过时钟锁相环晶振电路的局部改进以及信号电缆走向与结构作相应地小改动,此方案解决了原先54S04 和54S74 实际工作频率与截止工作频率接近,工作频率降额设计[10]余量不足的问题。

图9 93MH z时钟锁相环晶振电路改进后的组成图Fig.9 Diagram of improved circuit of 93MH z PLL

4.2 设计改进后的时钟锁定试验验证

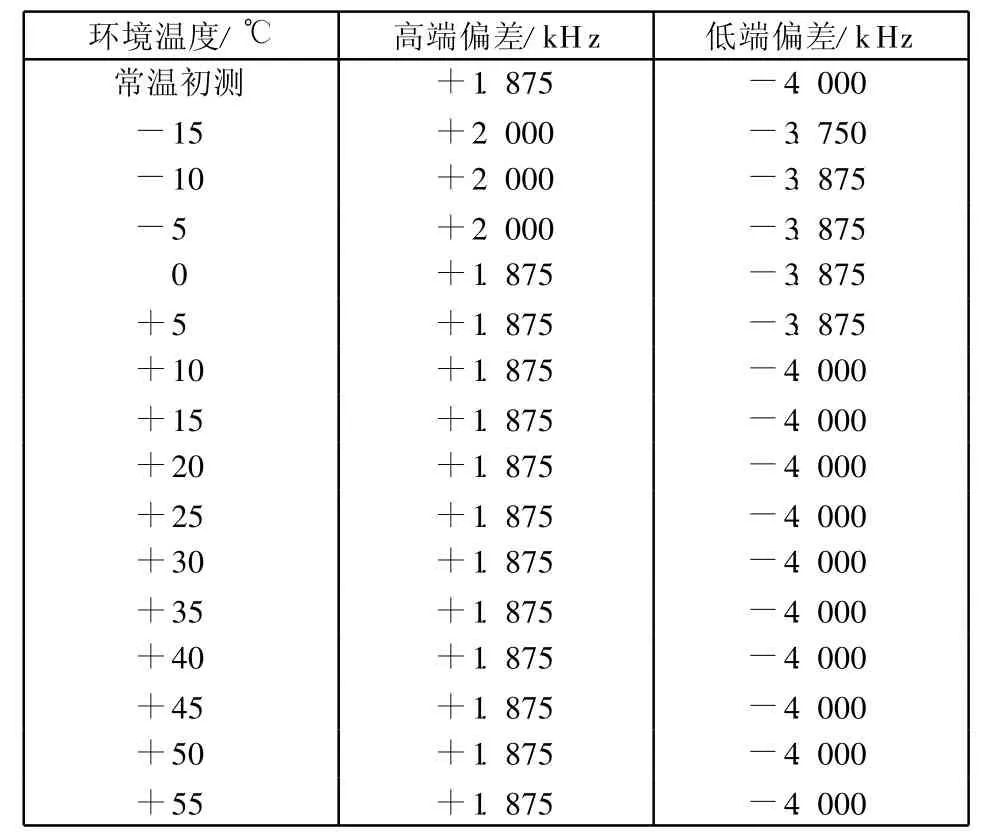

DPT 数传发射机的93M Hz时钟锁相环电路设计改进后,经过整机常温测试和高低温试验测试验证,锁相环时钟锁定范围明显增大,系统测试无误码。在全温-15℃~+55℃范围内,时钟可锁定的频率偏差范围测试数据见表3。

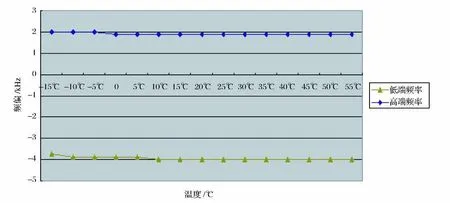

根据表3中的数据,画出DPT 数传发射机整机在高低温环境下,对应时钟锁定范围的高端频率偏差和低端频率偏差变化曲线如图10所示,从图10中可以更直观地看出改进后的DPT时钟锁定频率范围,要比改进前增加1倍左右,其锁定范围随温度变化小,更加稳定,允许固态存储器输出时钟频率的偏差范围也就相应地增加。

表3 DPT数传发射机的时钟锁定允许频率偏差范围Table3 Allowed frequency deviation range of DPT PLL

图10 改进后的DPT时钟可锁定的频率偏差范围与温度曲线图Fig.10 Improved DPT PLL locked frequency deviation range at different temperature points

5 结束语

本文通过对卫星数传分系统在轨测试时发现异常现象的分析研究,查找引起此类异常现象的可能原因,并通过地面试验模拟和问题现象复现,找出了产生问题的具体原因,对暴露的时钟锁相环晶振电路存在的缺陷进行了设计改进,通过各种温度试验验证,提高了产品的环境适应能力和可靠性,最终对在轨卫星数传分系统DPT 链路出现的异常现象给出了合理解释,可防止后续型号卫星出现相同的问题。

References)

[1]Christoph Rauscher.频谱分析原理[M].罗德与施瓦茨公司,1999

[2]张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,2003

[3]胡华春,石玉.数字锁相环路原理与应用[M].上海:科学技术出版社,1990

[4]王文理,张霞.基于FPGA的全数字锁相环的设计[J].电子设计工程,2009,17(1):39-40,43

[5]刘震余,宋鸿霞,夏仲英.MC4044 数字鉴相器的分析及应用[J].无线电通信技术,1982(4)

[6]M MDC-Tech 公司.Frequency control products[Z].M MDC-Tech 公司,2009

[7]TI 公司.Dual D-type positive-edge-triggered flip-flops with preset and clear[EB/OL].[1983-12-01].http://focus.ti.com/lit/ds/sym link/sn54s74.pdf

[8]Xilinx 公司.QPROTMVirtexTM2.5V radiation hardened FPGAs [EB/OL].[2001-02-13].http://www.xilinx.com

[9]Xilinx 公司.QPro series configuration PROMs (XQ) including radiation-hardened series (XQR)[EB/OL].[2001-11-05].http://www.xilinx.com

[10]戴慈庄.降额设计中若干问题的研究[J].北京航空航天大学学报,1995,21(4):30-34