基于MEMS加工工艺的亚毫米波肖特基单端混频器

2011-12-03钱嵩松陈和峰

钱嵩松, 陈和峰, 赵 芸

(1.南京理工大学,江苏南京210094;2.304厂,山西长治046012)

0 引言

混频器是现代雷达、通信系统中的重要组成部件之一。从国外的发展形势看,自上世纪九十年代起,亚毫米波混频器即已逐渐成为研究热点,进入本世纪以来,亚毫米波混频器更是得到了很大的发展。

例如,1997年 Hesler等人研制出基于肖特基管的亚毫米波混频器,在 585 GH z时由1.16mW本振功率驱动得到的双边带系统噪声为2 380 K[1]。2006年,Siles等人研制出了一个基于一对反向并联肖特基二极管的400 GHz混频器,并建立了一套用于仿真优化毫米波、亚毫米波混频器设计的CAD工具[2]。2009年,Bertand Thomas和Sim on Rea等人研制出(320~340)GH z的分谐波镜像抑制混频器,在通带范围内镜像抑制度达到(7.2~24.1)dB[3]。

国内目前在35 GH z频段已有一些成熟的产品,在94 GH z频段也正在大力发展之中,而亚毫米波频段的混频器才起步。本文介绍一种亚毫米肖特基单端混频器的设计与制作。

1 混频器设计

本文介绍的亚毫米波混频器是基于肖特基混频管的,因此主要的设计理论与方法与微波毫米波混频器是一致的。设计过程涉及五个方面[4]:

a)RF输入阻抗;

b)IF输出阻抗;

c)LO输入阻抗;

d)带外闲频的最佳端接阻抗;

e)各端口间的隔离度。

1.1 设计参数

所设计的亚毫米波混频器工作频率为360 GH z,中频带宽(2~6)GHz。设计变频损耗小于18 dB。

设计混频器的第一点考虑是混频管的选择,通常是要求其截止频率为工作频率的十倍以上。当前所能获得的可能工作频率最高的二极管截止频率大约只有1 500GHz,其它主要参数:反向饱和电流 Is=0.1 pA;二极管理想因子 η=1.15;零偏结电容C j0=40 fF;内建电势 φbj=1 V。

由于亚毫米波能量的微弱性,要求混频电路的基片必须是低损耗的,此外也要求其介电常数较为稳定。结合加工单位方面的工艺水平,最后选用的材料相对介电常数为3.4,损耗角正切为0.001,基片厚为50μm。

1.2 设计过程

混频器采用基波混频方案。现有的亚毫米波源的输出功率仅为-3 dBm左右,不能驱动多管混频器,因此采用单管混频。即便如此,这个输入本振功率也仍然难以保证稳定驱动混频管,因此必须加上一个直流偏置电路。

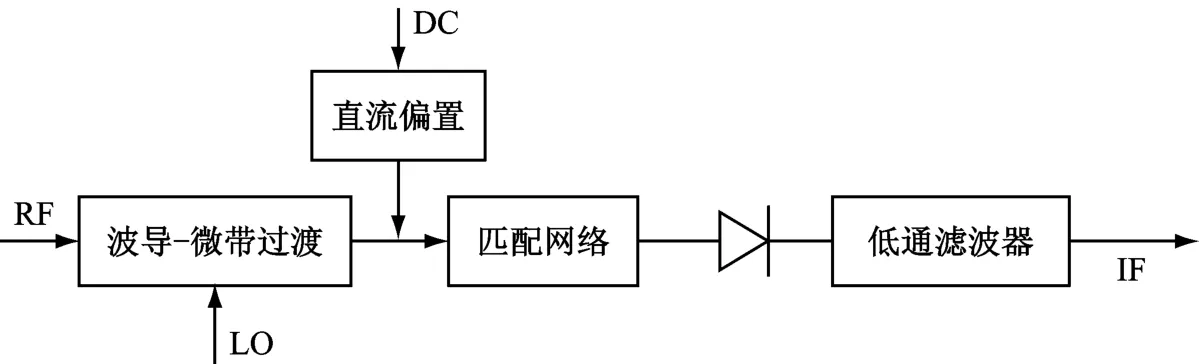

对于通常的单管混频器而言,一个重要的组成部分是本振与信号的耦合电路,耦合电路既要保证本振与信号能量最大幅度的加在混频管上,又要确保两者之间有良好的隔离度。本混频器的结构设计使本振与信号已在同一波导中了,因此并不需要设计耦合电路。360 GH z混频器方案,如图1所示。

图1 360 GH z单端混频器

为将RF及LO信号引入混频腔体采用H面波导-微带过渡。微带线平面与波导入射电磁波的传播方向垂直,通过探针把波导中的电场耦合到微带线上去,耦合孔开在波导宽边,为了减少微带线对波导内部电场的影响,耦合孔的大小要尽可能小,但应确保微带线的宽度。

本设计中的耦合孔大小为0.3 mm×0.2 mm。微带线厚度是0.01 mm,而其宽度则需优化选择。由于中心频率已经处于亚毫米波段,在绝对带宽完全可以保证的情况下,探针直接连接到50Ω微带线。最终由HFSS软件仿真得到在中心频率处的回波损耗达到20 dB,可以满足设计要求。

从中频低通滤波器来的负载端输出中频信号。采用六节巴特沃兹型低通滤波器,截止频率为20 GHz,这种滤波器结构简单,容易实现。由于考虑到加工精度的原因,取高阻抗线为90Ω,低阻抗线为20Ω。

仿真结果表明,低通滤波器在中频信号处的回波损耗达到18 dB,对(30~50)GHz的抑制度达20 dB以上,在保证通带低插损的情况下,具有很好的带外抑制。

由于本振功率难以驱动二极管,需要设计直流偏置电路。为了简化电路尺寸,方便加工,同样采用高低阻抗线串联的结构。仿真结果表明,在中心频率处的插入损耗达到25 dB以上。

由于二极管在信号功率的激励下呈现的阻抗并不是50Ω,需要阻抗匹配。匹配网络应在工作频段内保证无损耗地传输功率,在工作频段外保证功率全反射。

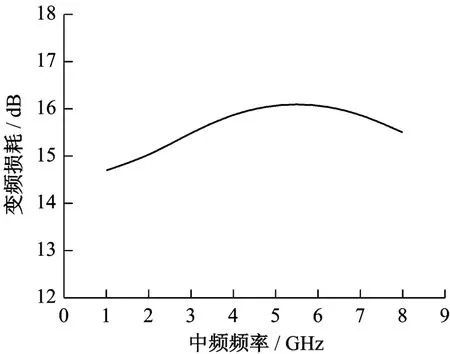

因此,匹配网络的设计目标是在负载终端功率最大程度地吸收,尽可能减少信号功率在传输过程中损耗。现将混频器各个分部在HFSS中分别仿真得到相应参数后,将其打包成s2p文件,结合混频二极管的参数,在ADS中进行总体仿真优化。最终得到优化后变频损耗随中频频率变化的曲线,如图2所示。

图2 仿真变频损耗

由图2可以看出:在中频(2~6)GH z范围内,变频损耗在(15~17)dB之间,最优处达到 15 dB,满足设计要求。

2 混频器加工

由于本混频器工作频率非常高,因此微带电路的相应尺寸也非常小,最细处仅0.02 mm,而整个微带电路的厚度也只有0.01 mm。针对这种精度的设计,通常用于微波乃至毫米波电路的腐蚀加工方法已不能满足要求。

为此本项目开发了一种以MEMS技术为基础的新型微带线加工工艺,涉及的基本工艺包括溅射、图形化、电镀、器件释放等。此处,还需进行多层结构之间的结合力、正负胶叠层技术、牺牲层技术、多层释放技术等问题进行了较为深刻的研究,选用合适的材料,并确定了合适的工艺参数。

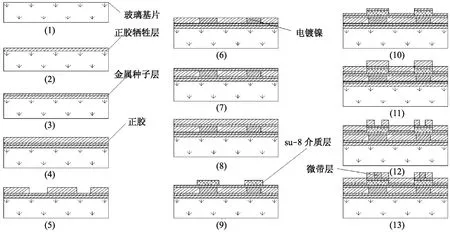

根据亚毫米波混频器的设计情况,器件为三层结构。该结构分别为金属接地层-介质层-微带层,如图3所示。

图3 微带线结构示意图

根据实际情况,工艺流程设计如图4所示:

a)对玻璃基片进行清洗、烘干;

b)制备牺牲层,涂覆5μm厚的正胶;

c)溅射种子层Cr/Cu,约1100埃;

d)制备金属接地层,涂胶、光刻、电镀镍10 um厚;

e)溅射金属保护层Cu,1000埃,制备这层金属层的目的是保证在Su-8胶显影时不会对正胶造成腐蚀;

f)制备介质层,叠层旋涂Su-8胶30 um厚;

g)溅射种子层Cr/Cu,约1100埃;

h)微带层的制备,涂胶、光刻、电铸镍/金,共厚10 um。

完成上述流程之后,再进行自上而下逐层溶解的方法来进行器件释放。

混频器的机械腔体由于结构尺寸微小难以加工。最细小的孔尺寸为0.6×0.28 mm2,针对这种结构,最终采用分割部件进行线切割的方法加工。

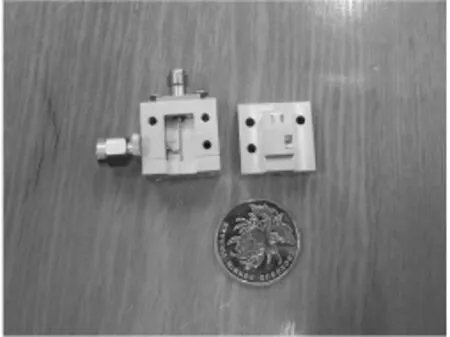

根据上述设计及加工工艺,最终得到的360 GH z混频器电路基片如图5所示,而整体器件如图6所示,二极管及中频输出、直流偏置均由金丝点焊连接。

图4 工艺流程图

图5 360 GHz混频器电路基片

图6 360 GHz混频器整体器件

目前国内还没有能进行亚毫米波混频器的测试手段,因此暂不能对混频器的性能进行实际测量。但本项目中同时也在进行其它亚毫米波器件的设计加工,总体方案是构建一个完整的亚毫米波探测系统,先在总体上进行实验,待条件成熟再逐步优化各部件设计。

3 结论

借鉴了成熟的毫米波混频器的设计方法,并基于MEMS加工技术,完成了一个肖特基亚毫米波混频器设计及加工。由于该混频器是常温工

作,不需要杜瓦瓶制冷,因此结构很紧凑,有望在需要小型化工作的地方获得很好的应用。

[1] J.L.Hesler,W.R.Ha ll,T.W.Crowe,etc.Fixed-tuned Subm illimeter Wavelength W aveguide M ixers Using Planar Schottky-barrier Diodes[J].IEEE T ransactions on M icrowave Theory and Techniques,1997,45(5):653-658.

[2] J.V.Siles,J.G rajal,V.K rozer.Design of Subharmonically Pumped Schottky M ixers for Subm illimetre-wave Applications[C].The1st European M icrowave Integrated Circuits Con ference,2006.145-148.

[3] Bertand Thoma,Simon Rea.A 320–360 GH z Sub-harmonically Pumped Image Rejection M ixer Using Planar Schottky Diodes[J].IEEEM icrow ave and Wireless,2004

[4] S.A.M aas.Non linear m icrow ave and RF circuits[M].Boston:A rtech H ouse,Inc.,2003.