一种数字幅频均衡功率放大器的设计*

2011-11-08张家田严正国

张家田 王 华 严正国

西安石油大学 电子工程学院 (陕西 西安 710065)

一种数字幅频均衡功率放大器的设计*

张家田 王 华 严正国

西安石油大学 电子工程学院 (陕西 西安 710065)

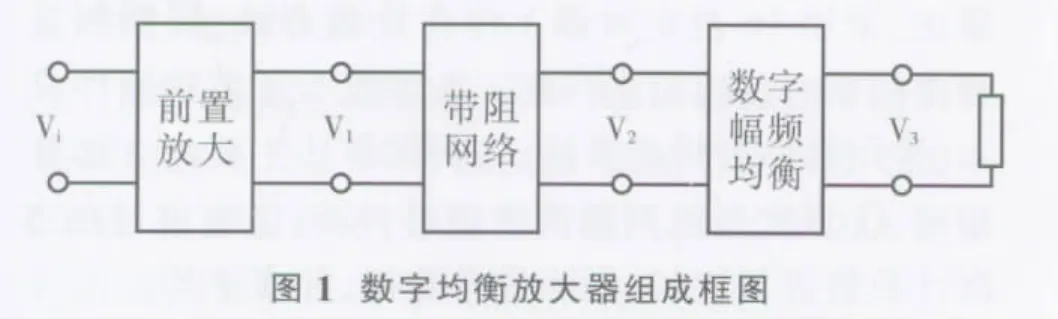

本系统由前置放大器、带阻网络和数字幅频均衡器3大模块组成。前置放大器采用集成运放组成的多级同相比例放大电路达到增益要求;带阻网络通过调整电路部分参数完成衰减要求;数字幅频均衡器采用集成了A/D、D/A、比较器、定时器、片上Flash存储器的SoC单片机最小系统实现幅频均衡。

前置放大器 带阻网络 数字幅频均衡器

数字幅频功率放大器首先要考虑小信号放大电路的设计,要减少输入信号所受干扰通过逐级放大满足增益要求[1],在放大电路中穿插滤波电路以满足通频带要求,在本设计中采用FPGA软硬件结合的方法。

1 系统方案

1.1 系统原理框图

数字幅频均衡放大器如图1所示。

1.2 系统各模块理论分析

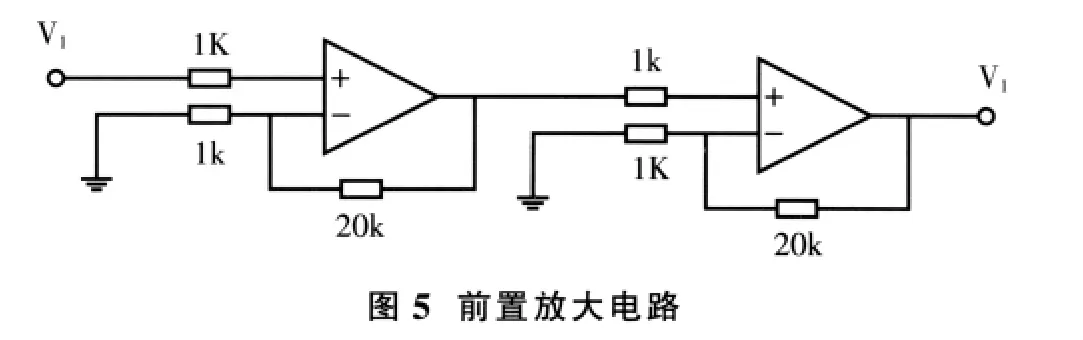

前置放大器应具有大于400倍的放大倍数和20Hz~20kHz的带宽,采用集成运放组成的多级同相比例放大电路。

带阻网络以10kHz时输出电压幅度为基准,有大于10dB的最大衰减,带阻网络如图2所示。

带阻网络有图3所示的幅频响应曲线,对不同频率的信号具有不同的衰减。

数字幅频均衡器根据带阻网络的频率特性,对不同频率的信号乘以不同的均衡系数,使得在系统的通频带内,不同频率相同幅度的信号具有基本相同的输出幅度。

数字幅频均衡器采用图4所示的结构,A/D转换器在嵌入式微处理器控制下对带阻网络输出信号V2进行采样,同时V2送入比较器进行整形,定时/计数器在嵌入式微处理控制下对经过整形的输入信号的周期/频率进行测量,根据存储器中保存的带阻网络频率响应曲线数据确定均衡器系数,与采样波形数据相乘后由D/A转换器转换成模拟信号输出。

2 理论分析与设计

2.1 前置放大器

前置放大器具有大于400倍的电压放大倍数和20Hz~20kHz的带宽,作为电压放大电路应有较大的输入电阻和较小的输出电阻,应采用集成运放组成的多级放大电路[2,3],各级采用电压串联负反馈,级间采用直接耦合。电路形式如图5所示。

图5采用2级同相比例放大电路[4],每级放大倍数为21倍,总共放大441倍。放大器的带宽要达到20Hz~20kHz,应选用增益带宽积大于4M的集成运放。

2.2 带阻网络

带阻网络结构与参数如图2所示,但由于原件参数的离散性,其相对于10kHz的输出电压幅度最大衰减可能达不到10dB,这时把100Ω电阻阻值适当减小。

2.3 数字均衡器

考虑到20Hz~20kHz的信号带宽、±1.5dB的输出电压波动范围、对输出波形失真没有特殊要求、性价比等因素,数字均衡器硬件系统可采用集成了A/ D、D/A、比较器、定时器、片上Flash存储器的SoC单片机最小系统来实现,SoC单片机c8051F020即可满足要求。

3 系统软件设计

3.1 程序设计

数字幅频均衡器程序的核心是信号频率测量程序和查表程序。

频率测量在20Hz~20kHz范围内均采用周期测量法,采用16位定时器工作在计数方式,周期测量程序的核心是边沿去抖动。本系统为了节约硬件成本,采用软件去抖动算法。去抖动算法主要由2部分构成:①多次延时判断消除边沿抖动;②对连续的5次计数值进行比较,剔除异常数据,并求平均。

查表程序的功能是根据频率测量值查带阻网络幅频特性曲线数据确定均衡系数。其算法原理如图6所示。整个通频带被分成若干子频带,每一子频带对应一个均衡系数,若频率测量值属于子频带BWi(i=0,1…n),则取对应的均衡系数Wi(i=0,1…n)与波形采样数据相乘,送至D/A转换输出。

4 测试方案及测试仪器

测试仪器:信号源Agilent33220A

数字万用表Agilent33401A

测试电路连接如图7所示。

4.1 前置放大器性能指标测试

(1)前置放大器放大倍数测试

测试方法:用万用表Agilent33401A监视Vi电压有效值,设置信号源Agilent33220A输出1kHz正弦波,调节输出电压幅度使万用表读数约为5mV,用万用表测量读取电压有效值V1,电压放大倍数Av。

测试结果:Vi=5.001mV,V1=2.108mV

结果分析:Av=V1/Vi=421,大于400

(2)通频带测试

测试方法:保持信号源Agilent33220A输出波形和幅度不变,调节输出信号频率使其在20Hz~ 20kHz范围内变化,并用万用表Agilent33401A记录V1在各测试频点的有效值,如表1所示。

结果分析:从表1数据可以看出,前置放大器的-1dB带宽为10Hz~50kHz,大于20~20kHz的要求。

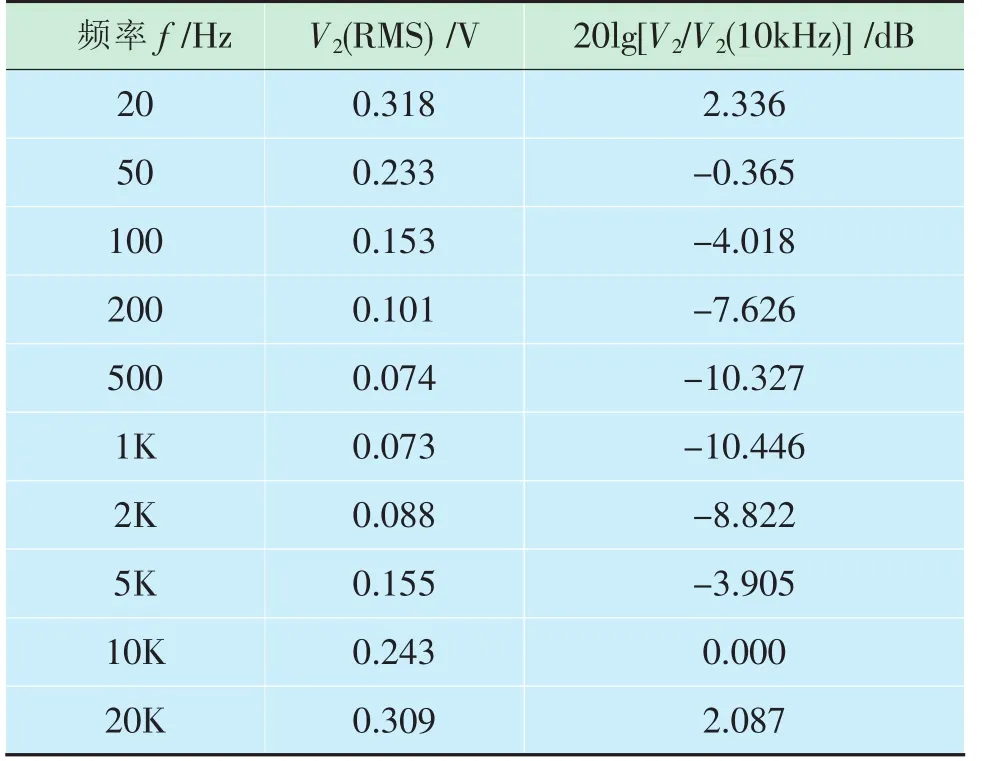

4.2 带阻网络幅频测试

测试方法:用万用表Agilent33401A监视Vi电压有效值,设置信号源Agilent33220A输出1kHz正弦波,调节输出电压幅度使万用表读数为5mV。保持信号源Agilent33220A输出波形和幅度不变,调节输出信号频率使其在20Hz~20kHz范围内变化,并用万用表Agilent33401A记录V2在测试频点的电压有效值,如表2所示。

结果分析:从表2数据可以看出,阻带网络相对于10kHz的最大衰减大于10dB。

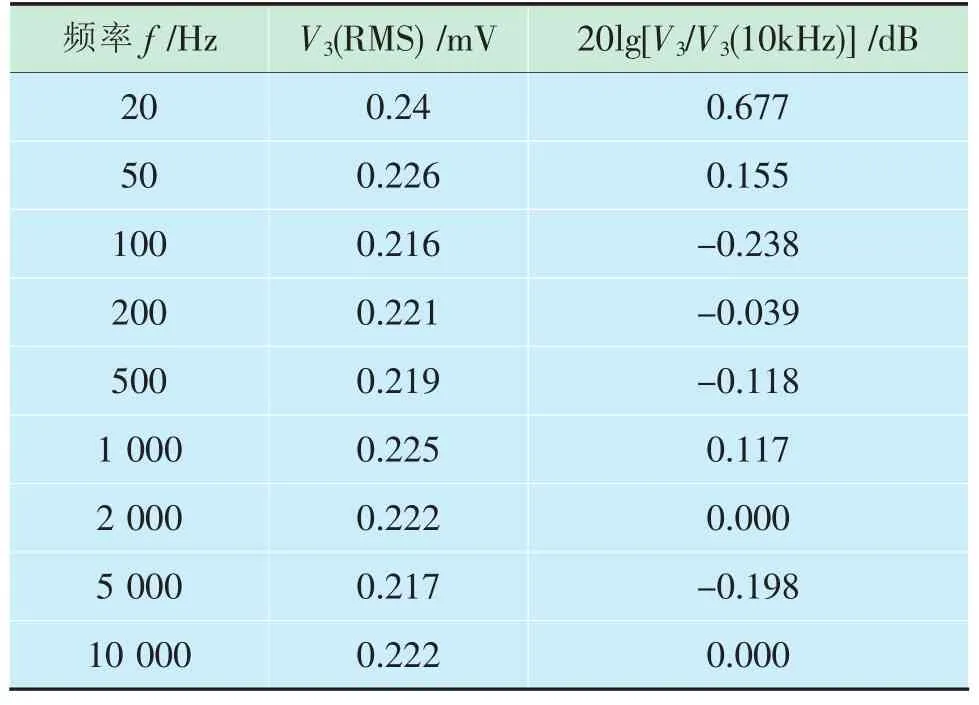

4.3 均衡输出测试

测试方法:用万用表Agilent33401A监视Vi电压有效值,设置信号源Agilent33220A输出1kHz正弦波,调节输出电压幅度使万用表读数为5mV。保持信号源Agilent33220A输出波形和幅度不变,调节输出信号频率使其在20Hz~20kHz范围内变化,并用万用表Agilent33401A记录V3在测试频点的有效值,如表3所示。

表1 用万用表测试V1在各测试频点的有效值结果

表2 V2在各测试频点的有效值测试结果

表3 V3在各测试频点的有效值测试结果

结果分析:在Vi电压不变的情况下,改变Vi的频率,在20Hz~20kHz范围内,带阻网络输出V2以10kHz电压值为基准的电压波动超过10dB,经过数字幅频均衡器均衡后,输出电压V3以10kHz电压值为基准的电压波动小于±1dB,小于要求的±1.5dB。

5 结 论

本系统采用FPGA软硬件结合的方法有效地减少了输入信号所受的干扰,成功的实现了小信号放大电路的设计,通过实际测量,各项参数均满足系统要求。

[1]任爱锋,初秀琴,常存,等.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004.

[2]高吉祥.数字电子技术[M].北京:高等教育出版社,2003.

[3]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[4]童诗白,华成英.模拟电子技术基础[M].北京:高等教育出版社,2000.

This system consists of three large blocks such as the preamplifier,the network with resistance and the digital-frequency equalizers.The preamplifier can reach the demands of increasing benefits through the application of amplifying circuit with the multistage identical proportion,which is made up of integrated operational amplifiers.The network with resistance can meet the requirements of attenuation by the adjustment of partial parameters of circuit.And the digital-frequency equalizer can realize the frequency equalization by the use of smallest system,which integrates the A/D,D/A,comparator,timer,and the single unit Soc in the flash storage.

preamplifier;network with resistance;digital-frequency equalizer

陕西省自然科学基金(2007D01),西安石油大学创新基金(YS28030533)

张家田(1963-),男,教授,1990年6月毕业于西安交通大学电磁测量技术与仪器专业,获工学硕士学位,现任西安石油大学光电油气测井与检测教育部重点实验室主任。

尉立岗

2011-02-07