单相电能表PCB板电路的静电防护设计

2011-11-07李嘉

李 嘉

(华北电力大学电气与电子工程学院,北京102206)

单相电能表PCB板电路的静电防护设计

李 嘉

(华北电力大学电气与电子工程学院,北京102206)

单相电能表的防静电指标已成为其在研发和生产阶段的重要技术内容,也是评价电能表能否安全可靠运行的重要参数之一。本文首先介绍了静电的产生,通过对静电放电过程的研究,分析了静电放电造成电子元器件破坏的主要失效模式,并提出了相对应的防静电措施,包括印制板布板和部分电路的优化设计,有效的提高了单相电能表的抗静电的能力。

单相电能表;静电放电;静电防护;失效模式

1、引言

随着电子行业的高速、蓬勃发展,电子元器件向高性能、高集成、低功耗的方向发展,促进了大规模和超大规模集成电路的广泛运用。随着集成电路内的间隙越来越小,绝缘隔离层越来越薄,再加上电子产品的加工过程中大量使用了塑料和高分子材料等易产生静电的物质,导致静电荷的产生与积累始终处于一个较严重的状态,这无疑大大降低了产品可靠性,提高了产品的返修率。另外,在电子工业领域,ESD带来的不仅仅是对电子器件的直接损伤,它还会产生强烈的电磁辐射干扰,影响电路的正常运行。ESD所产生的危害已成为当前科技、经济发展急需解决的难题之一,因此,对静电放电特征的更深一步的探索、了解,以及开展静电防护技术的研究,逐渐引起了人们的广泛关注和高度重视。

单相电能表在生产和挂网运行过程中容易受到静电的破坏和干扰,降低产品的可靠性,严重时甚至可能引起用户和电力公司的电费纠纷,给各方带来困扰,因此,在电子产品设计过程中,必须考虑到相关的静电防护电路,它们有助于预防并解决静电对电路所造成的危害。

2、静电放电的形成及失效模式

2.1 静电放电的形成

通常物体对外是不显电性的,这是由于它所具有的正负电荷量相等的缘故。如果两种物体互相摩擦,或者紧密接触后再分离、物体受压或受热、物质电解、物体受其他带电体感应,均可使电荷过剩,这样就产生了静电。一般来说,有较高介电常数的物体带正电荷,较低者带负电荷。带静电电荷的物体之间或者它们与地之间有一定的电势差,称之为静电势。

具体来说,静电产生的方式有很多,如接触、摩擦、冲击、冷冻、电解、压电、温差等,但主要是两种形式,即摩擦产生静电和感应产生静电。

(1)摩擦起电

当两种具有不同的电子化学势的材料相互接触运动时,电子将从化学势高的材料向化学势低的材料转移。当接触后又快速分离时,总有一部分转移出来的电子来不及返回到它们原来所在的材料,从而使化学势低的材料因得到电子而带负电,化学势高的材料因失去电子而带正电。对绝缘体而言,由于电子不易移动,过剩的电荷将在接触表面附近累积。总体来说,摩擦所产生的电荷量的多少与摩擦材料的特性、表面光滑程度、摩擦面积、摩擦面的受力、两物体的分离速度等因素有关。另外摩擦所产生的电荷量还与空气的相对湿度有关,空气湿度越小,则产生的电荷就越多。

(2)感应起电

有些情况下,两物体之间没有摩擦,甚至没有相互接触也能产生静电,如感应带电。感应带电就是带电荷物体的电场对邻近物体的电磁场作用,造成导体上电荷的分离。导体靠近带电体的一侧会出现与该电荷极性相反的感应电荷,而另一侧会出现与该电荷极性相同的电荷。事实上,只要物体带有静电荷就会在其周围产生静电场,就会使周围的物体感应带电,当然这种情况仅仅限于导体,因为绝缘体内缺少大量自由的电子,因此绝缘体一般不会产生感应带电现象。

2.2 静电放电的主要失效模式

由静电放电所引发的电子元器件失效一般分为突发性失效和潜在性失效两种模式。尽管在前期,两种失效模式所表现出的特征不一样,但是最终结果都是导致电子元器件彻底失效。

突发性失效是指当静电放电对电子元器件造成损伤后,电子元器件突然完全丧失其正常的功能,主要表现为开路、短路或相关的参数指标发生严重漂移,具体例子有:双极型器件的射-基两极呈短路状态、场效应管的栅-源间或栅-漏间呈短路或开路状态等。

潜在性失效是指静电放电的能量较低,低于元器件失效的电压阈值,不足以造成电子元器件的突然完全失效,仅造成元器件内部的轻微损伤,放电后元器件的电气性能参数指标虽仍然合格或略有变化,但器件的抗过电应力能力已经明显降低,或者使用寿命已明显缩短,该器件在以后的加电工作中,再受到正常应力或工作一段时间后元器件的参数性能将进一步退化,直至最终彻底失效。

一般来说,在正常环境中出现的静电放电失效大多数属于潜在失效。据统计,在由静电放电造成的元器件功能失效中,潜在性失效约为90%,而突发性失效仅为10%。然而,潜在性失效比突发性失效的所造成的隐患更大。

3、单相电能表PCB板电路的静电防护设计

3.1 PCB板的布线规则

PCB板的分层设计、恰当的布局布线等方法是解决生产和静电放电试验过程中所存在的静电干扰等问题的重要途径之一,以下介绍PCB板常用的几种抗静电布局布线方法。

(1)缩小电路的环路面积。当电路中的回路具有变化的磁通量时,就会产生感应电流。由于环路面积与所包含的磁通量是成正比的,因此环路面积越大,所产生的感应电流也就越强,感应电流会引起电路参数变化,因此设计时应尽量缩小环路的面积。

(2)缩短信号线的长度。长的导线比短的导线更容易接收到更多频率成分信号干扰,从而影响采样的信号质量,因此印制板设计时信号线一般要尽量小于3cm,这样可以降低信号线接收ESD电磁场干扰信号的频率。

(3)大面积使用接地面。印制板没有布置器件、走线的区域,采用大面积的接地面可屏蔽静电放电源上的电荷,有效减小静电场对信号线的干扰,避免ESD对元器件造成冲击和破坏。

(4)采用多层PCB板或者在电源线与接地线之间接入高频旁路电容等方式,以便增强电源线和接地线之间的电容耦合,这样有助于减小电荷注入问题。

(5)PCB接地线的阻抗要低且具有良好的隔离性。地线阻抗越低则静电放电电流就易于通过,也就越不容易发生电弧;此外,地线的长度与其宽度的比例应小于4-5倍,地线的阻抗才不会太大,电感效应才不会太明显。

(6)PCB板的边缘比较容易遭受ESD的干扰及破坏,因此,如时钟和脉冲信号等重要的信号线应尽量避免布置在PCB板的边缘位置;

(7)地线与重要信号线之间的距离应至少保持在4mm,以减少地线对信号线的干扰。

3.2 静电防护电子元器件的选择以及应用

仅仅靠PCB板布线的优化设计来提高ESD防护能力是很有限的,为了保证整个系统有较好的ESD防护能力,外部ESD保护器件是必不可少的。实际可根据具体需要可选择不同的ESD防护方案。典型的ESD防护器件主要有以下几大类;

(1)阻容元件

通过在每条信号线上接入阻容元件的方式,可以起到一定的ESD屏蔽作用。串联电阻能够抑制瞬间的峰值电流,并联接地的电容则能限制瞬间的峰值电压。

(2)钳位二极管

通过两只二极管可以将正、负极性之间的瞬态电压钳制在一定的范围内,再加上串联电阻提供功率负载的作用,从而起到正负极性的ESD防护。

(3)稳压二极管

虽然稳压二极管不是专门针对ESD的设计应用,但它的工作特性决定了它具有一定的正负极性ESD防护作用。它的缺点是PN结较小,故不能承受较大的峰值电流,此外,它所产生的寄生电容较大,有可能影响电路的正常运行。

(4)瞬态电压抑制器

瞬态电压抑制器又称TVS管,是针对ESD保护专门设计的一种固态二极管。TVS管的最大特点是响应时间短、漏电流很小,是理想的保护器件。

(5)气体放电管(GDT)

气体放电管采用具有一定气密性的玻璃或陶瓷作为外壳,管内充满如氖或氩的稳定气体,以保持一定的绝缘状态。气体放电管的优点是绝缘电阻大、寄生电容很小,可自行恢复,但缺点是响应速度和寿命均不够理想,且电性能会随时间变化而逐渐衰减。

4、单相电能表PCB板电路静电防护设计实例介绍

4.1 RS485电路的静电防护设计

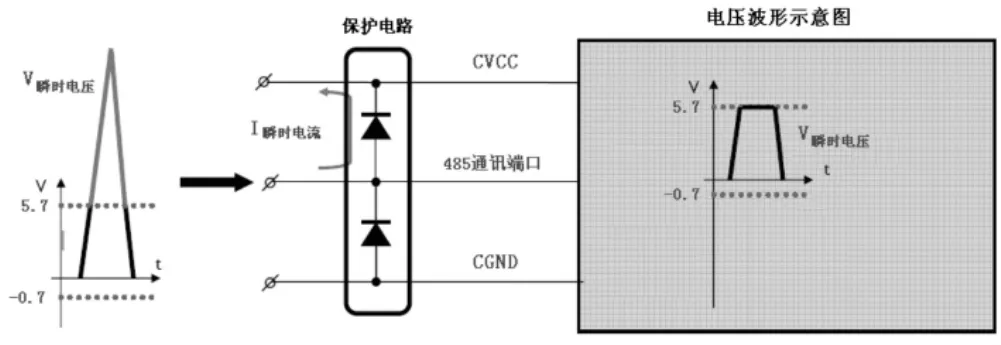

当电能表在生产过程中以及电力公司的抄表员在对表计进行RS485通讯时,可能会接触到表计的485通讯端口,其过程中所产生的静电就有可能造成485口的损伤,因此必须考虑相应的静电防护设计,添加了静电防护的电路原理图见图1。

图1:RS485电路静电防护设计原理图

当静电放电所产生的峰值电压通过485通讯的1、2端口进入电能表内部时,由于TVS管的响应时间最快,TVS管首先瞬间导通,将A、B端口的电压钳位在一个合格的范围内。TVS管导通后,产生了一个瞬时的峰值电流,峰值电流通过热敏电阻时,热敏电阻会发热,其阻抗在几十毫秒内增大几个数量级,从而承受了大部分的压降,随后通过热敏电阻的电流会逐渐减小,从而保护了TVS管。

电路中开关二极管D1和D3、D2和D4分别串联,将A、B端口分别接在中间,分别形成对A、B可端口的保护电路。

由于开关二极管是正向起作用,当被保护的线路上有瞬时高压脉冲进入,A、B端口的正向脉冲会分别通过开关二极管D1和D2释放,使得从线路进入到芯片内的电压维持在安全范围之内,如图2所示。

图2:开关二极管正向保护示意图

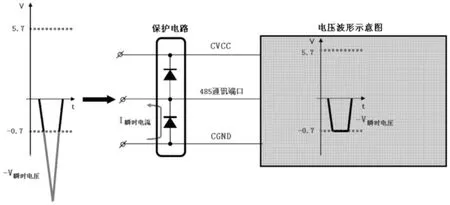

当有负向瞬时脉冲通过被保护线路时,通过开关二极管D3和D4将高压释放,使得从线路进入到芯片内的电压在安全范围之内,如图3所示。

图3:开关二极管反向保护示意图

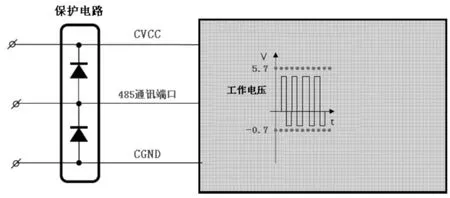

因二极管导通压降为0.7V,CVCC为5V,故A、B端口的信号电压范围均被限制在-0.7V~+5.7V之间,从而起到了对A、B端口的保护作用。在保护电路的作用下,A、B端口电压波形见图4。

图4:信号电压波形图

事实上,仅仅靠上述保护电路还不够完全安全,释放到CVCC端的峰值高压有可能进入到485芯片,可能对器件造成损坏,因此应在正向参考源到负向参考源之间增加了一个稳压二极管D801,使得超过电源的瞬时峰值电压能快速释放到地,从而避免内部器件遭受过压的冲击而受到损坏。

试验证明,该RS485电路的通讯口可承受1000次以上高达8KV的静电接触放电以及10KV的空气放电,具有抗干扰能力强、稳定性好等特点。

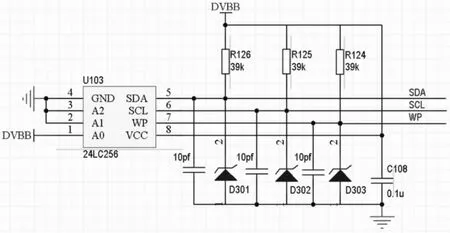

4.2 数据存储电路的静电防护设计

单相电能表的绝大多数电量信息、事件记录等相关数据均存储在内卡芯片中,其中电量信息可通过机械计度器、数码管或液晶显示屏直观的显示出来,是用户用电信息最集中的体现,也是电力公司管理用户、收缴电费的主要参考依据。

本文单相电能表的数据存储芯片以Microchip公司的24LC256为例进行说明。它具有256K的存储容量,可满足电能表正常工作时的数据存储需要,当外界环境对电能表施加静电场时,有可能会干扰内卡芯片与CPU的数据交换,甚至造成内卡芯片的损坏,导致重要数据信息的丢失,因此应考虑设计相关静电防护电路,见图5。

图5:数据存储电路静电防护设计原理图

在该电路中,对SDA、SCL、WP三个I/O口的保护均采用并入稳压二极管以及贴片电容的方式。当I/O口出现瞬时的峰值电压时,稳压二极管及时导通并泄放,从而保护内卡芯片不受损坏。另外,每个I/O口并联一个贴片电容,以滤除静电所产生场的干扰,提高数据通信的可靠性。

试验证明,当内卡芯片I/O口经受高压的静电冲击时,其信号电压波形图与图2、图3类似,其防护电路对静电的尖峰电压起到了很好的屏蔽和钳位作用,从而保护了内卡芯片不受损坏。

5、结束语

单相电能表在生产和运行过程中容易受到静电的损坏和干扰,为了保证其安全、可靠运行就要采取静电防护措施,静电防护措施是通过合理的电路设计来实现的。根据实际需要进行PCB板电路的优化设计,就可以有效的对静电起到屏蔽和抑制的作用。

[1]李秀峰,邱扬,丁高.静电放电及其防护设计[J].国外电子测量技术,2006,25(2):9~12

[2]薛同泽,沙占友,崔博.人体静电放电(ESD)及保护电路的设计[J].电子设计,2007,23(5):303~305

[3]郑英兰,付强,李文昌等.一种具有静电防护功能RS-485接口电路的设计方案[J].仪器技术与传感器,2009,11:68~70

[4]吴昱旻,张金平,张定会.电路中的ESD保护[J].仪器仪表学报,2006,27(6):2560~2561

[5]祁树锋,杨洁,刘红兵等.ESD对微电子器件造成潜在性失效的研究综述[J].军械工程学院学报,2006,18(5):27~31

[6]刘正青,严明.电子设备中PCB板的抗ESD设计方法研究[J].湖南工程学院学报,2003,13(4):30~32

Antistatic Design of Single Phase Energy Meters PCB

LI Jia

(North China Electric Power University,Collegeof Electrical&Electronic Engineering,Beijing102206)

Antistatic isnot only an important techniquerequest duringthedevelopment of singlephaseenergy meters,but alsooneof theimportant parameterstojudgeenergy meterscan run safely and dependably.Thispaper firstly introducesthegeneration of electrostatic toexploretheprogressof ESDand themain failuremodeswhich leadingtothedamageof electronic devices,finally putsforward several antistatic technologiesincludingdesign of PCBand optimization design of circuit which effectively advancingantistatic capability.

single phaseenergy meters;ESD;antistatic;failuremodes

TM930

A

1671-5004(2011) 04-0013-03

2011-6-2

李嘉(1981-),男,湖南常德人,威胜集团有限公司工艺工程师,在职攻读华北电力大学电气与电子工程学院硕士学位,主要从事单相电能表新产品的工艺可制造性、通用性的评估和研究。