无人机光电载荷图像处理器的设计

2011-11-06鲁剑锋

鲁剑锋

(中国科学院长春光学精密机械与物理研究所,吉林长春130033)

1 引言

无人机作为一种特殊的战场武器,其武器化趋势及其未来作战应用越来越引起世界各国的重视。特别是小型无人机,如美国陆军的“乌鸦”无人机等,已以其隐蔽性强,操作简单,成本低的特点,成为世界各国军方关注的焦点。无人机载光电侦查载荷主要用于实现战场环境的监测,战场目标的识别和跟踪。随着无人机任务载荷的发展和进步,探测手段也从原始的胶片照相机,发展到现今的可见光CCD、红外热像仪传感器以及激光指示器等。2002年,美国“捕食者”无人机安装了雷神公司研制的AN/AAS-52多频谱目标指示系统,该系统集成了红外、彩色光电照相机和激光指示器[1]。未来的无人机上还将安装多波段传感器来满足用户对多频谱和高频谱数字光电设备的需求,而图像处理器作为判断、识别目标并引导光电任务载荷跟踪目标的主要设备,在现今的无人机侦查设备中有着不可替代的作用。

本文对无人机载设备的技术特点和机载图像处理器的构成进行了研究,利用数字信号处理(DSP)芯片作核心器件,结合现场可编程门阵列(FPGA)和微控制单元(MCU)设计并研制了适用于无人机光电载荷的图像处理器,该处理器具有体积小、重量轻、功耗低等优点。

2 无人机载设备的技术特点

根据无人机自身的特点,无人机载设备有着与其他载体设备不同的要求:

(1)无人机载设备受到无人机体积的限制,其线路板的体积、形状都受到约束;

(2)由于无人机,特别是小型无人机的载荷能力有限,要求机载的任务载荷重量轻,以便飞机能够尽可能多地携带任务载荷。例如EADS公司研制的微型无人机重量约500 g,携带的传感器重量仅为50 g。美国陆军的“乌鸦”无人机和海军陆战队的“龙眼”无人机上的红外侦查设备是被称为“欧米茄”的红外照相机,重量不到200 g,功耗 <1 W[2];

(3)无人机提供的电源功率有限,不能像地面设备一样通过市电或者油机提供大功率电源,因此,要求机载的任务载荷功耗低。同时,无人机提供的电源范围较宽,通常要求载荷在(24±10)V的范围内都能够正常工作[3]。

基于以上的特点,本文设计了基于 TI的TMS320C6416DSP的小型机载图像处理器,系统呈圆形,直径为 97 mm,重量为 35 g,电源为+12 V~+36 V,功耗<5 W。

系统采用DSP+FPGA+MCU的构架,实现了从图像数据的采集、处理到输出的过程。

3 机载小型图像处理器的硬件构成

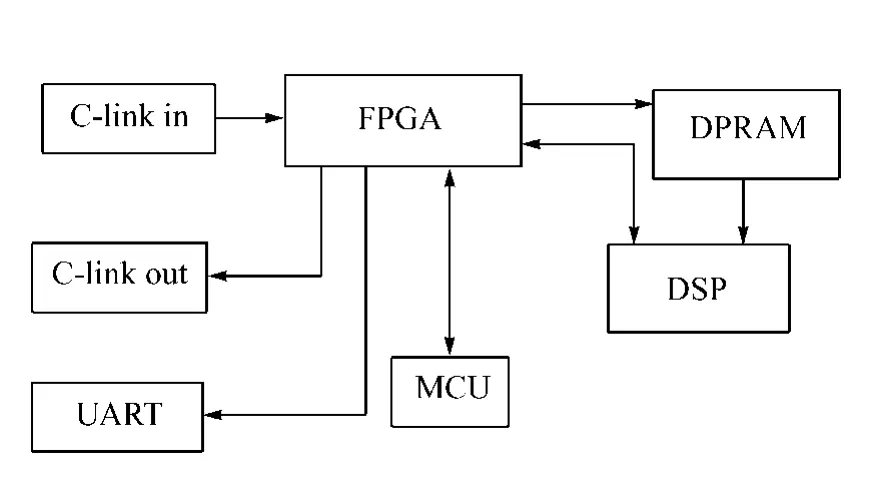

针对机载图像数据量大的特点,采用了美国TI公司的高速数字信号处理器—TMS320C6416为主处理器。同时,为了保证系统的实时性,以现场可编程门列阵器件FPGA作为系统的逻辑控制及时序处理器,使用MCU单片机C8051F023芯片作为外围接口控制处理器,配合以高速的Camera-link视频解码、编码器件等,构成了实时高速数字图像处理系统,其原理框图如图1所示。

图1 DSP图像处理系统硬件原理框图Fig.1 Schematic diagram of hardware for DSP image processing system

系统的工作原理为:Camera-link解码芯片DS90CR286接收由CCD给出的视频信号,经过解码得到图像信息、采样时钟以及行、帧同步信号,并将信号转化为标准TTL电平信号,发送到FPGA芯片中。FPGA芯片作为整个系统的逻辑、时序控制芯片,不仅控制图像数据的传输,同时,负责DSP与MCU的实时数据交换。系统时序以Camera-link解码出来的视频帧同步信号为整个系统的时统信号,这样,DSP芯片在图像的采集和处理过程中,不会被通讯等其它事件所打断,计算出来的目标位置等信息能够实时地通过FPGA传输给MCU芯片。MCU芯片同样以帧同步信号为消息,从FPGA芯片中读取DSP的信息,同时,将系统对外串口得到的消息通过FPGA芯片发送给DSP。MCU负责系统的对外通讯工作,通过RS422串口芯片实现与无人机系统的数据交换。MCU芯片对外通讯采用中断方式,收到外部通讯请求,立即响应中断,确保与系统数据交换的实时性;通过FPGA对内通讯,采取查询方式,在没有外部通讯中断的情况下,实时查询帧同步信号,查询得到帧同步信号后,通过FPGA进行图像处理器内部的数据交换工作[4]。

图像数据的传输过程为:Camera-link解码芯片将图像数据按照帧同步及采样时钟信号发送到FPGA芯片中,FPGA芯片将数据分成两路,一路提供给 DSP,用作图像处理;另一路发送给Camera-link编码芯片。提供给DSP的图像数据,在FPGA芯片内部设置两个双端口RAM(DPRAM)[5],将奇数行与偶数行的图像数据分别交替写入两个DPRAM中。根据DSP芯片发出的指令,FPGA将相应区域图像的第一行图像数据写入一个DPRAM中,然后通知DSP进行读取图像数据,在DSP读取图像数据时,FPGA将下一行的图像数据写入另一个DPRAM中,依次交替进行乒乓操作[6]。这样,在可选择的任意大小范围内的图像数据依次存入DSP的内存中。同时,FPGA将用于输出的图像数据发送到Camera-link编码芯片DS90CR285中,对图像进行Camera-link协议编码,通过Camera-link接口输出。

系统的主要特点是:

(1)DSP处理器在600 MHz时钟工作时,处理能力可达4 800 MIPS;

(2)DSP外扩主频为166 MHz的SDRAM,SDRAM容量为4 MByte;

(3)DSP 带 8MBIT FLASH ROM[7]的程序存储器;

(4)FPGA对图像进行滤波、边缘预处理等工作;

(5)MCU负责与外部进行串行数据通讯;

(6)具有 JTAG端口,支持实时的仿真调试[8];

(7)低电平逻辑数字电路设计,降低功耗。

全面采用BGA封装及小型表贴封装器件,器件工作的IO电压全部为3.3 V,减小了PCB尺寸,降低了功耗,增强了系统兼容性与可靠性。

3.1 TMS320C6416数字信号处理器

TMS320C6416是TI公司于2007年推出的TMS320C6000系列处理器中的一款主流图像处理器,处理器片内总线采用的是修正的哈佛总线结构[7,8]。针对无人机载设备的环境适应性要求,系统选用了TMS320C6416GLZA6E3宽温处理器,工作温度为 -40~85℃,时钟主频为600 MHz;采用了C6000系列标准的甚长指令字(VILW)结构,每个时钟周期可读取指令总字长为256 bit。系统在设计时采用DSP片内的PLL电路对外部时钟进行倍频[8],采用50 MHz的晶振作为提供给DSP芯片的工作晶振,用片内的PLL电路对50 MHz时钟进行12倍频,这样,避免了高频晶振及高频线路引起的电磁兼容问题。TMS320C6416片内集成了1M-BYTE的DATA RAM 和 PROGREM RAM[7]。

DSP对片外存储器的访问是通过两个外部存储器接口(EMIFA&EMIFB)[7]来实现的。

DSP的EMIF可以扩展的存储器接口包括[5]:

(1)同步突发静态RAM(SBRAM)存储器;

(2)同步动态RAM(SDRAM)存储器;

(3)异步存储器,如 SRAM,FLASH,FIFO等[8]。

选用SDRAM(HY57V653220B)作为 DSP的缓存,进行图像数据等的缓存。SDRAM的接口采用DSP芯片提供的无缝接口,接口速度为1/2 CPU CLOCK[9],占用 DSP 接口的 CE2 空间[9]。

图像数据从FPGA到DSP的传输,由EDMA控制寄存器把图像数据以EDMA方式导入DSP中[7]。DSP使用异步存储器接口与FPGA片内的DPRAM相连接,通过EDMA进行图像的导入工作[10],不占用DSP芯片的CPU资源,而是由EDMA控制器来完成图像导入的工作,从而将DSP的CPU资源完全用来实现图像处理算法[11]。

DSP程序存储在外扩的一片Flash芯片中(ATMEL公司的AM29LV800芯片),上电复位时将程序自举[12],导入DSP内。系统采用MAP1存储器映射方式[13],Flash闪存占用DSP的EMIFB的16 bit接口空间,SDRAM与双口RAM占用DSP的 EMIFA 的32 bit接口空间[14]。

3.2 逻辑主控FPGA芯片

系统选用的主控逻辑芯片是Altera公司的CycloneⅡ系列的EP2C35F672I8,该芯片的核电压为1.2 V,IO接口电压为3.3 V,同时支持1.5、1.8和2.5 V LVTTL电平的 IO输入和输出[8]。低电平的IO电压为高速信号传输提供了可能,确保了图像数据存储的实时性和完整性[2]。采用EPCS4串口ROM芯片作为FPGA的配置芯片,系统上电后,EPCS4芯片将程序自举加载到FPGA中[9,12]。

3.3 对外通讯管理芯片MCU

无人机系统的实时通讯往往与图像的帧信号不同步,而二者都要求实时性,因此,图像处理器在设计上选用了Silicon Labs公司的C8051F023单片机芯片,作为对外通讯的管理芯片,配合FPGA芯片完成图像处理器与无人机系统及图像处理器内部的数据交换。这样,既保证了图像处理器与系统的数据交换的实时性,又保证了DSP在图像处理过程中的连续性[4]。

C8051F023芯片采用高速的8051μC核,具有很好的兼容性。芯片使用3.3 V电源供电,比传统5 V供电的单片机功耗更小。芯片提供内置的2~16 MHz可编程时钟振荡器[8]。图像处理器采用芯片内部的16 MHz时钟作为芯片的工作时钟。芯片内部提供4 Kbit的数据存储器以及64 Kbit的Flash程序存储器。

3.4 上电程序加载与复位

图像处理器采用TI公司的TPS3824复位芯片作为整板的上电复位芯片。DSP及其程序存储芯片、MCU芯片和串口芯片等都使用TPS3824复位信号。而FPGA芯片因为不需要复位信号,所以使用 FPGA芯片提供的TPS3824看门狗信号[12]。

系统的DSP芯片、FPGA芯片以及MCU芯片都需要上电进行程序的加载工作。其中,DSP与FPGA芯片从片外的存储器进行程序加载,MCU芯片从芯片内部的Flash存储空间进行程序的加载。这样,产生了程序加载的时序问题,即DSP与MCU加载没有完成,FPGA已经加载完毕并发出了相应的初始化的指令;或者DSP加载完毕,而FPGA没有完成程序的加载,造成DSP与MCU之间的初始化指令不通等故障。为了避免产生加载时序的问题,图像处理器在设计上选择了应答的模式。FPGA芯片不需要复位芯片提供的复位信号,同时,FPGA芯片提供给复位芯片看门狗信号,也就是说,FPGA不提供看门狗信号,复位芯片将会进行图像处理器系统的复位[9]。因此,在DSP与 MCU程序设计时,设计了应答激活模式[13]。FPGA芯片加载完成后,将向DSP芯片与MCU芯片发出固定地址的高电平信号。DSP与MCU芯片在程序设计的初始化工作完成后,在循环中等待,读取相应地址的信号。收到信号,则证明FPGA芯片已经完成初始化,立即向FPGA发出应答信号,同时,可以进行图像处理或者系统通讯。若没有收到信号,则表示FPGA芯片初始化没有完成,DSP与MCU就在循环中不停地读取相应地址信号,直至收到FPGA信号为止。FPGA芯片初始化完成后,发出相应的信号,然后等待DSP与MCU的应答信号,同时,发送固定电平信号给复位芯片的看门狗[15]。若1.6 s内仍未得到DSP与MCU的应答信号,则复位芯片进行系统复位,DSP与MCU重新进行复位,程序加载。

4 结论

本文采用DSP+FPGA+MCU的硬件结构,设计并研制了适用于无人机光电载荷的图像处理器,与原有的其他机载图像处理器系统相比,该处理器具有体积小、重量轻、功耗低等优点。同时,整板采用小型、贴片型器件,系统的可靠性高。该处理器已应用于无人机系统中,工作良好,性能可靠,能够满足无人机光电载荷的任务需要。

[1]石岚.外军无人机光电侦查监视载荷研究[J].红外与激光工程,2007,36(9):103-106.SHI L.Research on UAV electro-optical reconnaissance and surveillance payloads[J].Infrared and Laser Eng.,2007,36(9):103-106.(in Chinese)

[2]秦明,朱会,李国强.军用无人机的的发展趋势[J].飞航导弹,2007(6):36-38.QIN M,ZHU H,LI G Q.The development of UAV[J].Winged Missiles J.,2007(6):36-38.(in Chinese)

[3]韩冰.战术无人机的任务载荷与发展分析[J].舰船电子工程,2007,27(3):31-35.HAN B.Load task and development analysis of tactical UAV[J].Ship Electronic Eng.,2007,27(3):31-35.(in Chinese)

[4]代少升,张新立.利用单片可编程系统对红外焦平面阵列进行实时非均匀性校正[J].光学精密工程,2009,17(4):854-858.DAI SH SH,ZHANG X L.Real time nonuniformity correction of infrared focal plane arrays by system on programmable chip[J].Opt.Precision Eng.,2009,17(4):854-858.(in Chinese)

[5]刘彬,房建成,刘刚.基于TMS320C6713B+FPGA数字控制器实现磁悬浮飞轮主动振动控制[J].光学 精密工程,2009,17(1):151-157.LIU B,FANG J CH,LIU G.Implementation of active vibration control for magnetically suspended flywheels based on TMS320C6713B+FPGA digital controller[J].Opt.Precision Eng.,2009,17(1):151-157.(in Chinese)

[6]陈升来,黄廉卿,郭静寰.基于整型提升小波变换的图像处理及DSP实现[J].光学 精密工程,2006,14(3):498-502.CHEN SH L,HUANG L Q,GUO J H.Image processing based on integral lifting scheme and its implementation by DSP[J].Opt.Precision Eng.,2006,14(3):498-502.(in Chinese)

[7]TMS320C64XX Peripherals Reference Guide[G].Dallas:Texas Instruments Incorporated,1999.

[8]TMS320C64XX CPU and Instruction Set Reference Guide[G].Dallas:Texas Instruments Incorporated,1999.

[9]姜培培,裘燕青,傅志辉,等.基于DSP和FPGA的多路型光纤光谱仪系统[J].光学 精密工程,2006,14(6):944-948.JIANG P P,QIU Y Q,FU ZH H,et al..DSP and FPGA based multi-channel fiber-optic spectrometer[J].Opt.Precision Eng.,2006,14(6):944-948.(in Chinese)

[10]王晓东,刘文耀,金月寒,等.基于DSP和CPLD的激光雷达图像采集和显示集成系统[J].光学 精密工程,2004,12(2):190-194.WANG X D,LIU W Y,JIN Y H,et al..Laser radar image acquisition and display integrated system based on DSP and CPLD[J].Opt.Precision Eng.,2004,12(2):190-194.(in Chinese)

[11]许廷发,赵思宏,周生兵,等.DSP并行系统的并行粒子群优化目标跟踪[J].光学 精密工程,2009,17(9):236-240.XU T F,ZHAO S H,ZHOU SH B,et al..Particle swarm optimizer tracking based on DSP parallel system[J].Opt.Precision Eng.,2009,17(9):236-240.(in Chinese)

[12]代少升,袁祥辉.提高DSP图像处理系统实时性的一种有效方法[J].光学 精密工程,2003,11(6):617-620.DAI SH SH,YUAN X H.Improvement of DSP image processing real-timeness[J].Opt.Precision Eng.,2003,11(6):617-620.(in Chinese)

[13]张思芳,李正明.一种实时成像跟踪系统的研究[J].光学 精密工程,2002,10(6):573-577.ZHANG S F,LI ZH M.Study of an image tracking system based on DSP[J].Opt.Precision Eng.,2002,10(6):573-577.(in Chinese)

[14]TMS320C62xx Peripherals Reference Guide[G].Dallas:Texas Instruments Incorporated,1999.

[15]朱明,鲁剑锋,赵建,等.基于TMS320C6202 DSP的实时数字图像处理系统的设计[J].光学 精密工程,2003,11(5):497-501.ZHU M,LU J F,ZHAO J,et al..Design of real-time digital image processing system based on digital signal processor TMS320C6202[J].Opt.Precision Eng.,2003,11(5):497-501.(in Chinese)