IC封装中高频段芯片电磁兼容分析

2011-10-26华北电力大学电气与电子工程学院陈银红高雪莲

华北电力大学 电气与电子工程学院 陈银红 高雪莲

IC封装中高频段芯片电磁兼容分析

华北电力大学 电气与电子工程学院 陈银红 高雪莲

随着电子技术的迅猛发展,集成电路中芯片的无源元件,如电容、电感和电阻等占的比例越来越大,元件数目也越来越多,而芯片的尺寸日益减小,导致电子产品的电磁兼容问题日益突出。如何对芯片源器件合理布局,降低电磁干扰,成为当前一大难题。与此同时,电子产品功能的日益复杂化及其性能的不断提高,使得电子器件的密度和工作频率都不断攀升;同时, 传输时延、反射、串扰、电磁干扰及地电噪声等问题也严重影响电路设计的可靠性,工程师面临挑战日益严峻。除了要对人为的和非人为的电磁兼容(EMC)和电磁干扰(EMI)有一个很好的了解之外,在芯片真正投入生产之前如何利用软件对其做EMC预测仿真,以期高质量、高效率地完成设计,对工程师来说变得尤为重要。

一、芯片设计中的EMC分析

在很多芯片的研发流程中,EMC问题都是在产品研制出来后经测试才发现的,需要反复修改,严重影响了产品的研发进度;有时还因为时间或空间紧张的原因,不能及时解决所有问题,造成事后多次返工,严重浪费人力、物力。利用先进的设计软件,可在产品设计初期,同步进行EMC仿真分析,对芯片管脚电容、电感进行分析评估,得出互电容、互电感、自电容、自电感等的矩阵分布,为产品设计人员提供EMC分析数据,使设计中潜在的EMC问题得到处理。

本文,笔者首先采用基于有限元法(Finite Element Method,FEM)的三维电磁场软件Q3D,对14×14 四列直插式扁平外壳型芯片管脚及内部的键合线搭建三维物理模型,采用有限元法进行高频电磁场分析,得到精确的电容电感矩阵参数;其次采用参数提取方法提取部分等效管脚参数值;最后利用优化仿真功能不断改进参数,以得到较理想的结果。

二、模型的建立与仿真

芯片级EMC仿真软件Q3D的主要功能是建模,把设计模型的尺寸作为参数输入,通过对芯片不同管脚施加高低电平,预测产生的电容、电感,进而减小矩阵规模,对矩阵进行优化,得到较好的电容电感的矩阵参数、表面电流密度场、矩阵最上一行电容分布列表以及最佳的矩阵参数收敛点。其应用流程是在产品研制的方案阶段,对一些准备沿用的芯片进行评估,以确定是否需要改进设计;在试样阶段,对所有的新设计或改进设计的印制板进行评估,同时与部件级和系统级EMC分析软件结合,进行产品电磁干扰和电磁敏感度分析;在定型阶段,与其他相关软件联合对产品EMC进行评估。

1. 封装外壳各管脚的建模与仿真。利用Aansoft Q3D Extractor,建立四列直插芯片封装外壳模型,由于对称性,本实验选取模型的1/4建立有限元模型。坐标系的单位选定毫米,具体建模过程如下。

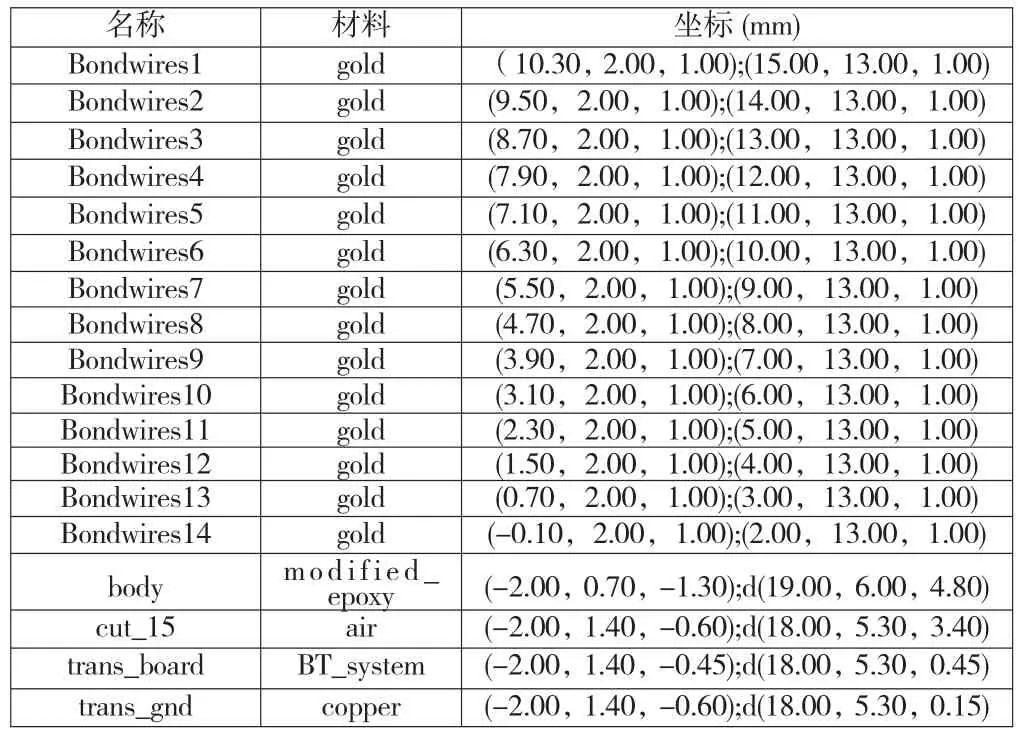

(1)确定芯片封装结构尺寸,画出芯片封装外壳及管脚模型。输入模型尺寸的同时,确定各个材料的属性;对不同的材料设定不同的颜色,以便区分。材料参数及尺寸数据见表1。

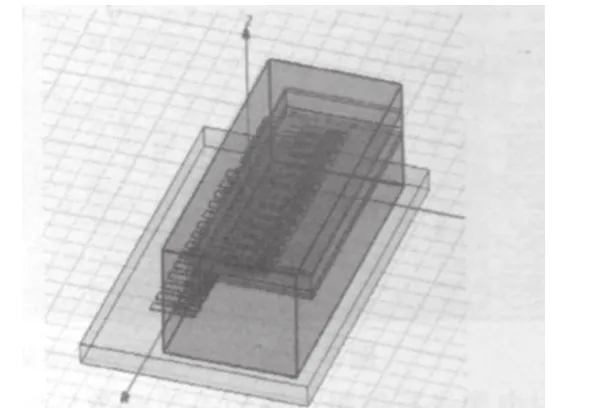

(2)进行模型的Boolean运算,得到正确的模型。如图1。

(3)给各个管脚自动分配二维节点。对节点分配电源和热沉。

(4)求解。可以自由设定出错率冗余度、频率范围,求得电容和电感。

(5)保存数据。

表1 封装外壳模型材料参数及尺寸相关数据

图1 芯片封装外壳封装模型

(6)检查错误。如果有错误,根据提示,进行修改。直至正确无误。

(7)仿真分析。

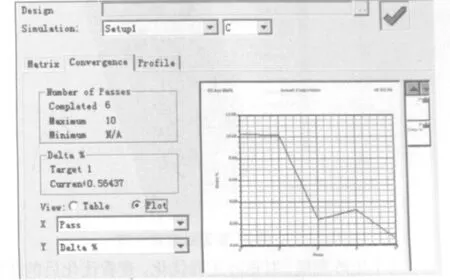

(8)查看求解结果。由此得到相关表列文件、最佳电容收敛点,以图形画出(图2,图3)。由列表和图看出,在第六阶段就达到收敛,即可得到稳定的电容值。

图2 电容C收敛点数据

图3 电容C的收敛阶段

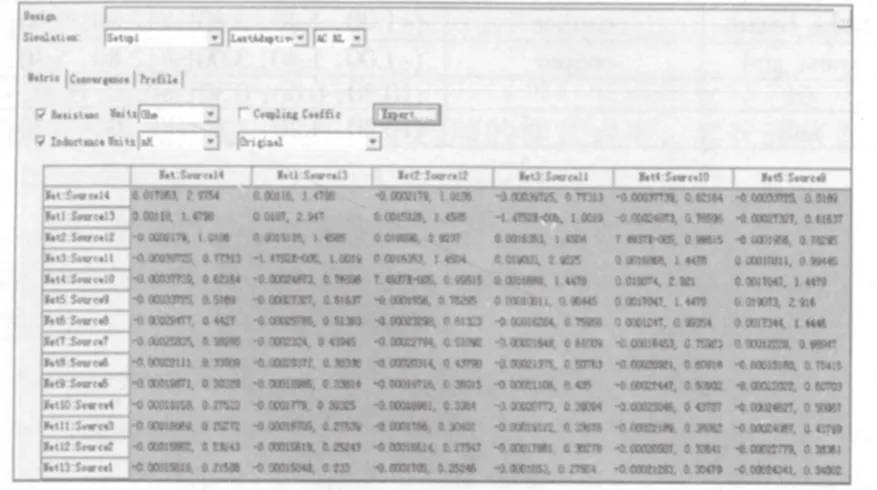

(9)提取电感、电容矩阵,分别如图4、图5所示。矩阵的主对角线上分别是自电容、自电感;非主对角线上的分别是各管脚的相互电容,互电感。由图分析可知,自电容是正值,互电容为负值,自电容绝对值大于互电容绝对值,管脚相互之间距离越远,互电容绝对值越小。

图4 部分电容分布矩阵

图5 部分交流电感分布矩阵

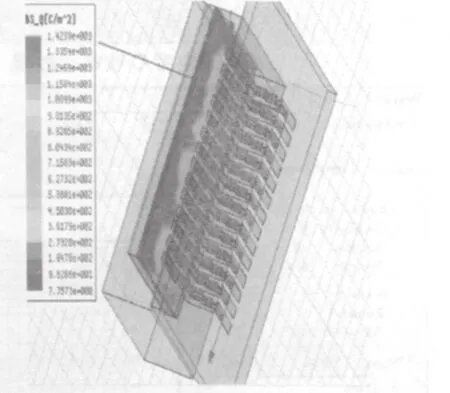

(10)对电源进行编辑,得到不同电源分配状态下各管脚的电容分布,如图6,图7所示。由图可以看出管脚电平设置为高电平的电容值大,管脚为低电平的电容值小,编辑产生的电容密度范围为0.000 0~1.423 9E3(C/m2)。

图6 各管脚电源大小

图7 各管脚电容分布

(11)减小矩阵规模,对矩阵进行优化。查看优化后的矩阵结果,如图8所示。

图8 对电容矩阵优化后得到的电容分布

(12)显示14个管脚Pin_1,Pin_1_1~Pin_1_13交流场时磁场表面电流密度,如图9所示。

图9 编辑电源电平后,对应的各管脚磁场表面电流密度

2. 芯片内部键合线的建模与仿真。目前设计较为复杂的芯片,应该是以DSP与FPGA为核心,以信号处理为主要功能的高速芯片。此类芯片的一个共同特点是广泛采用模拟和数字分离技术,采用多层PCB结构,并在结构上采用了地电平面的分割。对于这样的PCB,尤其要重视地电噪声与EMI问题,因为地电平面的分割会导致共模噪声的增加。原理上,可以通过并连和串联节点减小矩阵的维数,减少计算量,简化模型,但这时会涉及回流的问题。回流路径不当是产生共模噪声的主要原因(前向电流经过信号线流出,但是返回的电流可能会流经未知区域),前向电流和回流所形成的区域会产生辐射噪声。为了减少上述原因引起的电磁干扰,在进行电源与地的分割时,可以利用键合线将电源和芯片的地连接起来。

仍然使用Aansoft Q3D Extractor,建立四列直插芯片封装的内部芯片模型,由于对称性,本实验选取模型的1/4建立有限元模型,材料参数及尺寸数据如表2所示。通过建模仿真分析,可以得到键合线的电容矩阵分布;通过有选择性地合并管脚连接形式,可以得到不同管脚并连时的环路自电感、环路互电感矩阵分布。此处电感矩阵均为正值。在模型各部分建模结束,进行模型的Boolean运算后,得到正确的模型,如图10所示。

表2 芯片内部模型材料参数及尺寸相关数据

图10 14键合线芯片结构

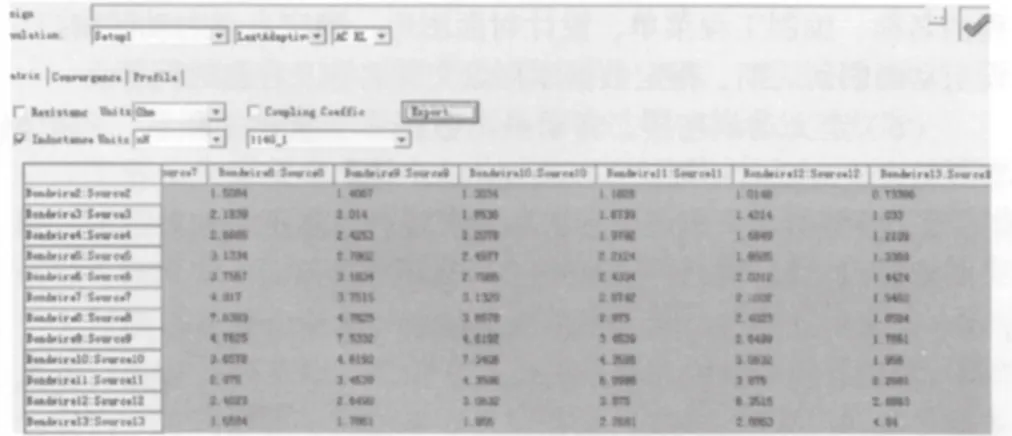

利用软件进行仿真分析,求得电容矩阵和ACRL矩阵、DCRL矩阵。如图11、图12、图13。缩小矩阵规模,得到优化后的矩阵。此处把键合线1和14并连,得到的矩阵命名为114G,并为Bondwire114设置回路。然后再把键合线1和13并连,得到的矩阵命名为113G,并为Bondwire113设置回路。

图11 电容C部分矩阵数据

图12 部分交流电感矩阵分布

图13 部分直流电感矩阵分布

(13)查看求解结果。可以得到对应的114GACRL矩阵分布(部分矩阵如图14所示)。以及13GACRL矩阵分布(部分矩阵如图15所示)。

图14 114G_1部分ACRL矩阵分布

图15 113G_1部分ACRL矩阵分布

三、结论

本次仿真主要利用 Q3D 软件进行了芯片的EMC仿真分析, 包括芯片封装外壳管脚的电容、电感矩阵参数的提取,矩阵优化,处于磁场中的芯片表面电流密度分布等。对矩阵不断优化,减小矩阵规模,得到参数不断优化的矩阵。通过这一系列的电容、电感的预测,获得了一组电磁干扰相对较小的数据,对以后芯片的设计和大批量生产电磁辐射小的电子产品具有指导作用。本文给出了芯片在高频工作时的电磁兼容性分析以及相应的建模实现过程与方法。在多数复杂芯片中,在对其进行仿真时,比如用ANSYS进行电磁仿真时,还要自行设置网格,进行网格划分才能进行精确的仿真, 需要的计算资源会非常大。相比之下, Q3D软件可以自身自动化分网格,不必大费周折一次又一次地选定各个单元模型的尺寸。另外,用Q3D软件对多管脚和多键合线的芯片建模,比用其他软件更易于建模,人性化的设计使建立的三维模型更易于观看。因此,用较少的计算资源和时间便能仿真得到高频下芯片电容、电感矩阵分布等有价值的数据。