基于ADS仿真可控增益技术对雷达捷变频的影响

2011-10-21梁小朋王苏敏

邓 茜 梁小朋 王苏敏

(江西理工大学应用科学学院,江西 赣州 341000)

基于ADS仿真可控增益技术对雷达捷变频的影响

邓 茜 梁小朋 王苏敏

(江西理工大学应用科学学院,江西 赣州 341000)

介绍频率合成器的环路参数设计原理,研究了系统参数变化对环路滤波器的幅频响应和相位裕度的影响,并采用ADS软件对系统捷变频性能仿真。从仿真结果可知,采用可控电荷泵电流增益技术可以很好的解决快速跳频问题。

频率合成器;捷变频;ADS;可控增益

(一)引言

频率合成器是电子系统的核心部件。随着现代通信、雷达、电子侦察和对抗技术的飞速发展,系统对其性能指标也提出了愈来愈高的要求。在各种高性能、宽动态范围的频率跳变中,捷变频时间是一个重要的限制因素。捷变时间这一指标,直接影响到跳频干扰和抗干扰系统的跳速,以及雷达频率捷变特性,也越来越受到人们的关注。因此,快速跳频频率合成器的研制具有重大的现实意义。

(二)锁相频率合成器的原理

图1 整数N频率合成器原理框图

图 1为整数分频锁相环的原理框图。其中,分频因子 N通常由外部数字信号设置。在许多频率综合器中,控制信号使用串行输入数据。当环路锁定时,进入鉴相器的两个信号频率相等,所以,VCO的输出频率是鉴相频率的 N倍,而且严格同步,用锁相环构成的频率合成器具有频率稳定度高、相位噪声小、电路简单易集成、易编程等特点。

(三)可控增益技术与环路带宽的关系

1.无源三阶环路滤波器的设计

为了更好的抑制环路带宽频率十倍以上的纹波,三阶环路滤波器是一个较好的选择,并且可以得到所有环路元器件参数的准确解。我们将从时间常数入手,来计算各元器件参数值。

图2 无源3阶环路滤波器

图2 中,环路滤波器阻抗和开环传输函数表示如下:

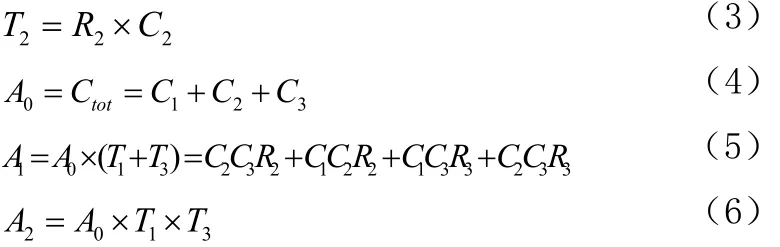

其中,滤波器的系数与时间常数的关系:

根据相位裕度的定义可得:

经验证明,为了保证 3阶环路滤波器的稳定性,要求T2>>T1+T3,使得在环路带宽处,斜率为-20dB/dec同时相位裕量最大,这是本文滤波器设计的基本思想。其中T31为极点比T3/T1,如图 2所示。同样我们通过对三阶滤波器的相位裕度偏微分方程:

近似T2>>T1+T3,可以得到:

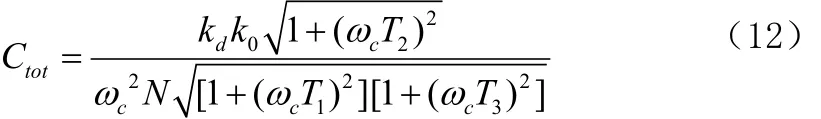

由于在环路带宽处,开环传递函数增益为1,这样可得Ctot:

从(12)式中可以看出,在不改变环路滤波器的参数、压控增益及分频比的情况下,电荷泵电流增益Kd与环路带宽的变化成正比。

2.环路带宽的选取

锁相环 PLL的带宽,需要根据应用环境和环路部件的特性来选择。在选择环路带宽时有三个需要考虑的因素:

(1)最大的环路带宽可以有最快的频率转换速度(最短的锁定时间);

(2)优化的环路带宽能够取得更好的相位噪声性能;

(3)最小的环路带宽可以取得最大的参考边带的抑制。

通常我们要在这三个因素之间做出折中考虑,由于可控电荷泵电流增益技术可以直接改变PLL环路带宽和相位裕度。可见,可控增益技术不仅能缩短捷变时间而且能提高相位噪声指标,当采用大电流增益进行快锁,经过定时器设置时间之后,会自动切换成小电流增益,减小稳态时环路带宽,改善相位噪声,优化杂散抑制性能,提高整体性能指标。

(四)可控电流增益技术对频率综合器捷变时间和稳定性的影响

对于跳频信号源的设计,在保证频率源的相位噪声、杂散等性能指标的前提下,尽量减少频率的切换时间,以利于在一次跳频通信内有相对长的时间来传送有效数据。捷变频时间是跳频信号源的研制的一个非常重要的指标。通过上述无源3阶滤波器的设计方法,设计一个4阶锁相环,通过计算得滤波器元件参数,如表1所示。

表1 三阶滤波器设计实例

1.锁定时间仿真模型建立

瞬态仿真模型是对系统进行闭环仿真,仿真模型中要考虑 VCO的输入电容和输入电阻,对于一些集成压控振荡器的锁相环芯片其 VCO输入电容可能为 0,瞬态响应是采用 ADS中的 Envelope仿真。分频比改变时的锁定时间仿真模型如图3所示:

图3 分频比改变时的锁定时间仿真模型

2.可控电流增益技术对捷变频时间的影响

由于小型化的设计要求,使用两种不同的环路带宽或增益也许是仅有的选择,在捕获时环路具有较大的带宽或增益,锁定以后

使环路的带宽或增益减小,改善带外相噪。

对于三阶环路滤波器来说,较高频率的极点对环路的瞬态特性影响很小,因此在计算锁定时间和锁定过程可以忽略,仍然可以利用二阶环的计算公式来计算其锁定时间,其中,tol为锁定频差。

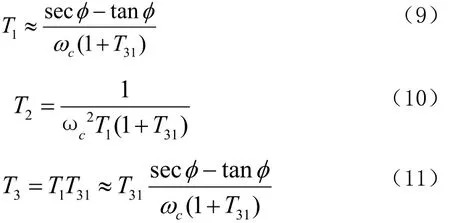

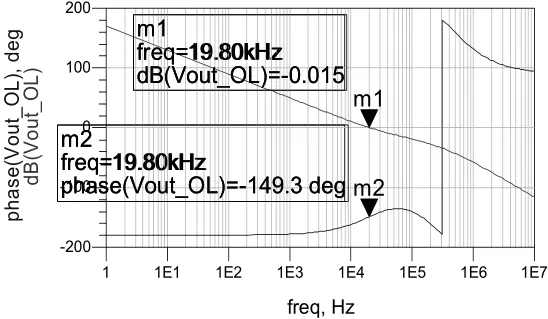

改变电荷泵电流增益,不仅改变了环路带宽,同时也改变了相位裕度。电荷泵电流增益分别为5mA和 1.06mA时的开环波特图,如图4和5所示。采用表3-1中的环路滤波参数,其中kd先取5mA,仿真其相 位裕度和锁定时间。然后保持环路元件参数不变,电荷泵电流增益由5mA变为1.06mA时,通过仿真可知,其带宽由 60KHz变为 19.8KHz,其相位裕度由45°变为30.7°。通常,锁定时间不仅受环路带宽的影响,由于相位裕度与阻尼系数有一定的正比关系,所以相位裕度对锁定时间也有一定的影响。

图4 kd为 5mA环路波特图

图5 kd为 1.06mA环路波特图

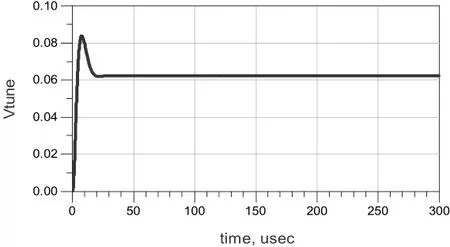

图6 kd为 5mA环路的响应瞬态

图7 kd为 1.06mA环路的瞬态响应

如图6、7所示,保持环路其他元件不变时,电荷泵电流增益为5mA比电荷泵电流增益为1.06mA时的锁定时间大大减小。由于相位裕度关系到系统的稳定度,典型值选择在45°到55°之间。当相位裕度在48°时锁定时间最短,当相位裕度小于48°的时候,会使环路开始振荡,增加锁定时间,此时,锁定时间与相位裕度成反比;当相位裕度大于48°的时候,会使环路系统响应速度缓慢,同样会增加锁定时间。此时,锁定时间与相位裕度成正比;所以相位裕度和阻尼系数一样必须小心选取,其值过大和过小都不利于快速跳频。

3.可控电流增益技术对稳定性的影响

如图 4、5所示,电流增益由 5mA自动换成小电流增益1.06mA,稳态时,环路带宽减小为19.8KHz,相位裕度减小为30.7°。显然,相位裕度太小,导致系统不稳定,延长锁定时间。同时,可控电流增益技术对 PLL相位噪声也有较大的影响。所以,可控电流增益的大小必须小心选取,应从各方面影响综合考虑。

(五)结束语

在一些特殊场合,为满足小尺寸要求,不得不放弃一些性能更优越的电路或大体积芯片,而采用结构简单的锁相频率合成技术。然而,从频率合成理论来看,传统的单环锁相环难以达到指标要求,若采用可控电流增益技术,不但能解决这个问题,而且可以简化电路,进而降低成本。本文采用ADS仿真软件对频率合成器的主要性能进行建模仿真,重点仿真了采用可控电流增益技术对PLL捷变时间和稳定性的影响。仿真结果表明,可控电流增益技术在提高雷达捷变频性能上能起到良好的作用,对类似的设计有良好的借鉴意义。

[1] 张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,2005:1-20.

[2] Dean Banerjee. PLL Performance, simulation, and design 4thedition[M].national semiconductor,2006.

[3] Andy. Phase locked loop design,Analysis of a sigma- delta modulator using RF behavioral modeling and system simulation[M].agilentTechnologies,2002;8-9.

[4] Roland E.Best.锁相环设计、仿真与应用第5版[M].李永明,译.北京:人民邮电出版社,2007:5-30.

[5] 方立军,马骏.C波段低相噪数字锁相频率合成器[J].系统工程与电子技术,2001,23(2):22-24.

TN74

A

1008-1151(2011)05-0031-02

2011-02-17

邓茜(1984-),女,江西吉安人,江西理工大学应用科学学院信息工程系助教,硕士,研究方向为无线射频通信电路。