基于全双工以太帧间隔的源同步时钟传输方法

2011-10-20张俊杰宋英雄

陈 健, 张俊杰, 宋英雄

(上海大学特种光纤与光接入网省部共建重点实验室,上海 200072)

基于全双工以太帧间隔的源同步时钟传输方法

陈 健, 张俊杰, 宋英雄

(上海大学特种光纤与光接入网省部共建重点实验室,上海 200072)

提出在全双工以太物理层中,基于以太帧间隔 (inter-packet gap,IPG)的固定比特率业务同步时钟传输方法.该方法引入同步剩余时戳(synchronous residual time stamp,SRTS)算法,是一种不受以太分组流量影响的带外时钟传输方法.通过连分数展开分析恢复时钟的各阶抖动成分,给出基于以太帧间隔的同步剩余时戳算法的参数选择方法,并通过软件仿真和现场可编程门阵列(field programmable gate array,FPGA)硬件实验证明了其优良的同步性能.

帧间隔;同步剩余时戳;源时钟同步

本研究提出的基于全双工以太帧间隔 (interpacket gap,IPG)源时钟同步方法具有定时精度高、抖动低及易于实现的特点.本研究从基于以太 IPG数据传输的原理入手,介绍了 IPG数据在以太 PHY层的接入位置和数据帧格式,进而引入同步剩余时戳 (synchronous residual time stamp,SRTS)的时钟同步方法.对适应以太 IPG数据传输的 SRTS算法的参数选择详细地进行了分析和仿真,给出了源时钟和恢复时钟的实验对比结果,并证明了本研究提出的源时钟同步方法具有不受以太网中分组流量和分组交换的延迟变化影响,不占用以太分组的带内带宽的优点,是一种在点对点全双工以太网中带外传输源同步时钟的新方法.

1 基于 IPG的数据传输原理

IEEE 802.3协议最初定义 IPG[1]的目的是为了在 PHY层上分隔 2个相邻的数据包,以使所有处于同一以太网段的站点可以探测到不活动的载波,解决半双工模式的冲突检测问题.对于全双工方式的以太网,由于不存在信道的争用,因此,MAC子层的载波监听多路访问 /冲突检测 (carrier sense multiple access/collision detect,CSMA/CD)算法失去了应有的作用,保留的以太网络 IPG只起到继承 10M以太网MAC协议的目的.百兆快速以太网可以采用全双工方式进行工作,而光纤方式的千兆以太网和万兆以太网只能采用全双工工作方式,MAC帧之间的IPG在 PHY层被 12字节的空闲码字替代,以提供对端 PHY层接收码流的连续性,便于时钟恢复电路从接收码流中获得定时信号.由此可见,在 IPG中插入有用的数据,可以提供特殊的传输通道[2],此时PHY层码流还是连续的,只是替代了原来的空闲码型数据,不会使时钟恢复电路的性能变差.

一般的以太 PHY层器件均通过 xM II接口与MAC层器件连接,因此,在充分利用现有器件的基础上,通过在MAC层和 PHY层的 xM II接口间串接一个 IPG数据模块,即可将 IPG数据接入点到点的以太传输通道中.为了让 IPG数据模块容易地识别出属于自己的数据帧,可以安排有别于正常以太帧前导码的 2字节码字作为 IPG数据帧的前导码,IPG数据帧携带的数据可以是 6字节,或者是 5字节数据加 1字节 CRC-8校验.为了产生可靠的帧定界物理层信号,需要在 IPG数据帧的前后各留 2字节的空闲码,这样就形成了插入数据的 12字节帧间隔(见图 1).

图 1 IPG数据的帧格式Fig.1 Frame structure of IPG data

实际上,无论 PHY层速率是多少,IEEE 802.3协议的 IPG间隔都是 12字节.如果接收时对插入数据的 IPG不作任何处理,MAC层会丢弃这些插在IPG中的数据,原因是 IPG数据帧的长度小于正常以太帧最小的 64字节长度.此时,除了产生一个MAC层的出错记录外,对原有的以太数据传输不会产生任何影响.

本研究中的时钟同步分析及实验均以100BASE-T为例说明,IPG数据同样可以接入到全双工千兆以太网中.此时,除了 PHY层中物理编码子层 (physical coding sublayer,PCS)以 8B/10B编码代替了百兆以太网的 4B/5B编码外,其他方面基本与百兆以太网相同.

2 基于 IPG的剩余时戳同步算法

将源时钟的信息 (如时戳值[3])通过 IPG数据模块 (带外)或以太网正常数据帧 (带内)传输是两种可行的同步方法,但均不是最佳的方法.因为,这两种方法需要在目的地用异步时钟重建一个时戳,通过重建时钟产生的时戳与接收到的源时戳不断地相互比较,最终同步到源时钟上.此时,带内传输方法时戳值的到达时间将受变化的分组传输延时影响,而带外传输方法虽不受分组延时影响,但对重建源时钟的环路控制参数依赖性很大[4].

如果能利用全双工以太网中 PHY层接收时钟同步于发送时钟的这一特点,就能利用类似异步传输模式 (asynchronous transfer mode,ATM)协议中的SRTS算法[5]获得直接的源同步信号,从而将避免上述时戳同步方法的缺点.

2.1 基于 IPG的剩余时戳同步原理

SRTS算法是 ATM标准中规定的电路仿真时钟同步方法之一[6].SRTS将源时钟与公共时钟在发送端的频率比值关系传给接收端,接收端利用可获得的公共时钟及频率比值关系恢复出源时钟频率.比值关系通过异步计数的方式实现.由于源时钟频率与公共时钟频率不一定成整数倍关系,因此,在每个源时钟周期内对公共时钟的连续计数必然产生整数和非整数部分,非整数部分在以后的多个源时钟周期内不断累积,最终产生了可变的整数计数值.SRTS算法将这些可变整数计数值以模的余数形式传递给接收端;而模的商则不需要传输,因为接收端只要已知源时钟频率就能事先确定一个最小的商数,这样就减少了在ATM中传输电路仿真同步信息的开销.由于在每个源时钟周期内对公共时钟是连续计数的,因此不会引起截断误差和累积误差.

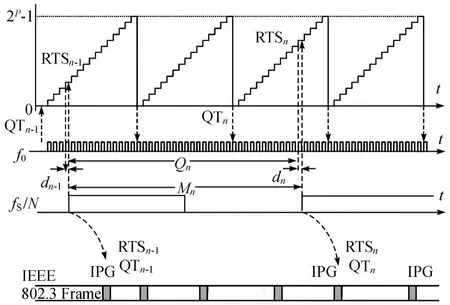

利用全双工以太网中网络接收端 PHY层恢复的时钟同步于发送端时钟这一特点,即公共时钟是通过链路提取的,可将发送端的同步业务源时钟频率与以太网物理时钟之间的关系通过带外的 IPG数据传给接收端,实现在接收端对同步业务源时钟频率的精确恢复.基于 IPG的同步剩余时戳传输如图2所示.

假设源时钟 fS在 N分频后的第 n个周期内有Mn个 f0时钟周期,f0=fT/x,fT为以太网发送端的时钟频率,x为分频数,则

一般情况下,Mn不一定为整数.由于 fS和 f0是2个异步时钟,fS的上沿会在 f0脉冲的任何地方出现,对 f0脉冲计数的计数器在后续输入脉冲到来前会保持当前的计数值,在 2个 f0脉冲的中间出现的计数使能信号 (fS的上沿)将引起对f0的非整数计数.因此,定义 Qn为第 n次计数的整数部分,它是第n次计数值Mn加上第 n-1次计数的小数部分 dn-1取整的结果,而第 n次计数的小数部分 dn为

图 2 基于 IPG的同步剩余时戳传输Fig.2 IPG based transm ission of synchronous residual time stam p

将式 (2)迭代求和,可得

由于 0≤di<1,因此

式 (5)的不等式两边同时除以 n,取 n→∞,可得

由式 (6)可得,只要取样数目足够多,每周期的非整数Mn的平均值与每周期的整数 Qn的均值是一样的,如果 Mn为容差 [Mmin,Mmax]中的固定值 Mc,则Qn的长期平均值等于真实的 Mc值.因此,式 (2)反映了 2个异步时钟之间的正确计数关系.由于没有简单地舍去每周期计数的小数部分,而是不断地将其累积,因此,经过长期平均能够达到传输Mn精确值的目的.

由于 fS是固定比特率业务的源时钟频率,假设其频率稳定度为 ±ε,因此,第 n次的计数值 Mn介于M的最小值和最大值之间,即

Mmin≤Mn≤Mmax. (7)

由于计数的小数部分 dn和 dn-1介于 0和 1之间,将

式 (7)代入式 (3),可得

因此,在源时钟 N分频后的一个周期内,以脉冲 f0的周期为最小计数单位的脉冲计数值 Qn至少为└Mmin」.如果用 P来表示 Mn-Qn的剩余部分,则其表示的范围必须覆盖Mn-Qn的任何取值.极端情况下 ,Mn可取 └Mmin」,同时 Qn取 └Mmax」+1,因此 ,P至少满足

基于 IPG源时钟同步信号的产生方法,是在发送端建立一个以 f0脉冲周期为最小计数单位的,模为 2P的时戳生成电路,计满 2Pbit后,QT计数器计数加 1.当源时钟的N分频信号上沿到来时,将 P bit计数器的当前计数值锁存起来,作为本次剩余时戳的RTS数据.这样,式 (3)中的 Qn可表示成经历了 QTn个 2Pf0周期加上 RTSn-RTSn-1个额外 f0周期,即

基于 IPG传输的数据量比 ATM头部可携带的数据量多很多,因此,同时传输商数 QT和余数 RTS的好处是,接收端无需预知同步业务的频率就能恢复出发送端的同步时钟,这也是与 ATM中只传输RTS的区别之处.

在接收端,由于以太网 PHY层恢复出的时钟 fR同步于发送端的时钟 fT,fR经 x分频后得到与发送端同频的 f0,因此可以产生一个与发送端相逆的时钟恢复过程.最后,使用锁相环电路 (phase locked loop,PLL)将恢复出的频率乘 N倍,从而恢复出固定比特率业务的源时钟频率 fS.

2.2 基于 IPG的剩余时戳同步算法的参数选择

在基于 IPG的剩余时戳同步算法中,必须确定参数 P,N,x的选择范围.文献 [7]指出,如果 f0/fS<4.9,且 P最多为 3 bit时,将具有符合 I.363.1中规定的抗信元丢失能力,这里 P的选择由式 (9)决定.一般而言,源时钟的频率稳定度 ±ε并不是很大,└Mmin」与 └Mmax」相差很小 ,选取 1字节的 P值不仅可以满足式 (9)的要求,而且可以使 f0和 fS的比值更大,这将明显降低由量化误差引起的抖动.

由于以太网中 IPG的出现不是固定的,是随不同大小以太帧出现频次的变化而变化的,因此,源时钟N分频后的时间间隔必须大于 2倍的最长以太帧持续时间,才能保证接收端不会发生接收缓冲下溢现象.而如果在源时钟N分频后的时间间隔内有多个以太帧,则可忽略中间的 IPG,只利用剩余时戳产生后的第一个 IPG就可以至少传输一个源时钟剩余时戳.以全双工 100BASE-T为例,包括前导码的最小以太帧长 72字节,最长1 526字节.这样,N可取512.

由于接收端接收到的同步剩余时戳编码流只是源时钟相对于公共时钟的瞬时相位的近似值,因此,在接收端恢复出的源时钟中通常会出现抖动.

当 Mn的小数部分为 0,即 R=Mn-└Mn」=0或Qn=Mn时,则每次采样不会有相位变化,可准确恢复源时钟.但是,当 R≠0时,则每次时戳采样的取整运算存在余数,会发生相位变化,经过若干个时戳采样周期后,相位的累积将达到或超过一个 f0周期的单位间隔 (unit interval,U I),而一旦超过,累积相位就会减去一个 f0周期的单位间隔,而这时正是时戳采样Qn=Mn+1时期.因此,累积相位误差的最大值是一个 f0周期的单位间隔 (U Ip-p).

对于某种特定频率的同步业务时钟 fS和由最大 IPG间隔确定的 N,以太网发送时钟 fT的分频数x决定了 f0,从而又确定了Mn及其余数 R.

文献[8]认为,与累积相位误差的幅度值相比,低频抖动的频率更值得关注.分频数 x对低频抖动的频率影响很大,Mn的余数 R的取值范围为(0.41,0.44),可使锁相倍频滤波后的抖动均方值达到最佳.

对于一个频率稳定度为 ±ε的,固定比特率业务的源时钟频率 fS,假设Mn的标称值为Mnorm,即

以全双工 100BASE-T以太网传输 E1时钟信号为例 ,设 fT=25.000 Mbit/s,fS,norm=2.048 Mbit/s,N=512,按照式 (11)寻找最佳分频数 x,使0.41≤Rnorm≤0.44.经计算机编程寻找到的最佳分频数 x为 9.考虑到 E1时钟信号频率的容限范围,本研究在2.047 8~2.048 2 Mbit/s范围内每隔100 Hz作一次 x的搜索,可得 x取值为 1,3,4,9.下面通过对相位抖动频率和抖动幅度的仿真试验对 x的取值作进一步的分析.

2.3 剩余时戳的相位抖动仿真结果与性能分析

在 ITU-T I.363.1中规定,1≤f0/fS<2.实际上,在基于 IPG的剩余时戳同步算法中,由于有足够多的字节空间可以携带剩余时戳的余数和商数,因此,f0完全可以取到最大值,即 x=1.选取分频数 x的标准是,由其确定的余数 R是否会产生很低频率的相位抖动或很大的抖动幅度.因为较高频率的相位抖动更容易被锁相倍频的低通滤波器滤除,而较低的频率则不易被滤除.

利用Matlab软件对上例中的 x从 1~12取值,计算在 E1标称频率下,相位抖动的阶数和各阶抖动的幅度.仿真结果表明,只要 E1的时钟频率偏离其标称频率,原来的零余数就不再为 0了,并且出现了相位的低频抖动成分.可见,单纯由源时钟的标称频率求解最佳分频数不符合实际情况,实际的源时钟频率可能在允许的频率稳定度范围内取任何值.因此,需将 E1时钟频率在 2.047 8~2.048 2 Mbit/s范围内每隔几十 Hz作一次相位抖动成分分析,并按照0~3阶抖动成分分别作图比较.图 3显示了 x=1时相位抖动的分布情况.虽然抖动的频率在整个分析的频带内都有分布,但是,0阶抖动的幅度比 x取其他值时都小,1阶以上抖动幅度则更低.x=3,4,9时的 0阶或 1阶抖动的频率集中在 0~800 Hz,幅度为 0.2~0.4 UIp-p.而在其他分频数情况下,低频抖动幅度均大于 0.2 UIp-p,有些甚至达到 0.8 UIp-p左右.

图 3 相位抖动分布(x=1)Fig.3 Phase jitter d istr ibution when x=1

因此,基于 IPG的 SRTS算法的最佳参数选择需在源时钟频率容限范围内仔细搜索,而不只是针对源时钟的标称频率.如果有多个网络时钟分频数能使余数落在 0.41~0.44范围内,即使它们的相位抖动性能很接近,还是要作进一步的相互比较,选出最佳值.

图 4显示了 E1时钟频率为 2.047 932 5 MHz,网络时钟分频数 x=1时,0,1和 2阶相位抖动的仿真波形.这些抖动波形是由于剩余时戳算法对余数取整所引起的.当网络时钟为 25 MHz时,f0=25 MHz,N=512,Mn的近似值是 6 250.206 000 4,取整后的 Mn为 6 250,余数 R=0.206 000 4≈975/4 733.根据文献[9],将其展开成连分数形式,即

图 4 抖动波形(x=1)Fig.4 Jitter wave for x=1

由图 4(a)可见,0阶抖动由 4个 Mn=6 250和1个Mn=6 251的相位波形 (R0=1/5)构成的三角形组成.0阶抖动的周期为 5个 N/fS≈1.25 ms,频率约为 800 Hz,0阶抖动的最大幅度约为 0.065 UIp-p(一个 U Ip-p为 f0的周期,即 40 ns).因此,基于IPG的剩余时戳算法的 E1恢复时钟的理论,同步精度为2.6 ns.由图 4(b)可见,1阶抖动由 6个 0阶抖动波形(R0=1/5)和1个R′0=1/4的相位波形构成的三角形组成.1阶抖动的周期约为 33个 N/fS≈8.25 ms,频率约为 120 Hz,最大幅度约为0.015 U Ip-p.由图 4(c)可见,2阶抖动由 6个 1阶抖动波形(R0=7/34)和1个R′1=6/29的相位波形构成的三角形组成.2阶抖动的周期约为 230个 N/fS≈57.50 ms,频率约为 17 Hz,最大幅度约为 0.002 UIp-p.

实际上,抖动仿真中还存在 3阶以上的相位抖动,但由于其频率和幅度比前 3阶更低,对恢复的固定比特率业务时钟精度产生的影响可以忽略不计,而前 2阶相位抖动是恢复时钟精度的主要决定因素.

3 源同步时钟传输的现场可编程门阵列电路设计和实验结果

按照第 2节叙述的 IPG数据传输原理,可在全双工以太网的MAC层和 PHY层之间插入一个中间处理模块来实现 IPG源时钟的传输,而原来全双工以太网的 PHY层和MAC层的接口芯片可不作任何修改.在图 5所示的 IPG源时钟传输实验方案中,KS8995是一块集成了 5个百兆以太网口的网络交换芯片,其作用是实现 PHY层和MAC层的连接及MAC交换功能.由于 KS8995能提供M II接口上的信号,因此,由现场可编程门阵列 (field p rogrammable gate array,FPGA)构成的中间处理模块能利用这些接口信号完成MAC层与 PHY层的连接.

按照以上设计思路,本研究开发了一套硬件实验电路板,并对 A ltera公司的 EP1C3T144C8 FPGA芯片进行了 IPG数据发送和接收电路的编程.实验测试分 3个步骤:①利用电子设计自动化(electronic design automation,EDA)工具 ModelSim模拟仿真;②使用 FPGA开发软件固有的信号跟踪器 SignalTap对 FPGA的数据处理情况进行跟踪;③使用示波器进行实际测量.

3.1 发送端设计

发送端实体主要包括网络交换芯片 KS8995和FPGA.KS8995为M II接口信号的提取提供了接口,FPGA负责产生业务时钟的同步时戳并实现在 IPG时间段的数据插入功能.

图 5 IPG源时钟传输实验方案Fig.5 IPG based source clock transm ission exper imental schem e

发送端的 FPGA内部逻辑结构如图 6所示.MAC层数据从M II接口输出后,FPGA对其进行缓冲,以保证有时间判断链路上的 IPG是否到来.业务时钟通过分频后的触发信号来决定是将下行数据直通 PHY层还是使用同步时戳数据替换 IPG中的空闲字段,其中同步时戳是由本地 25 MHz发送时钟计数得到的.为了获得稳定的计数值,本地振荡器应具有足够好的频率稳定性和抖动容限,才能使由本地振荡器获得的发送时钟具有较好的品质.

图 6 发送端 FPGA功能框图Fig.6 Function block of transm itter in FPGA

3.2 接收端设计

接收端实体同样由网络交换芯片 KS8995和FPGA构成.KS8995的功能与发送端芯片完全相同,但FPGA的功能与发送端不同,其目的是还原业务时钟.

接收端的 FPGA内部逻辑结构如图 7所示.来自 PHY层的数据在传给MAC层的同时,提取插入的同步信息数据,然后将低频时钟恢复,再通过数字锁相环构成的倍频单元恢复业务时钟.

3.3 实验结果

图 7 接收端 FPGA功能框图Fig.7 Function block of receiver in FPGA

利用 Altera公司的 FPGA设计软件 Quartus自带的SignalTap工具,抓取实际FPGA里恢复的同步信息 (见图 8).图中第 2排即为业务时钟同步信息数据,显示为十六进制 55 aa 18 6a 00 aa,共 6字节,其中前两字节 55 aa代表用于识别的包头,中间的 18 6a为同步用的时戳信息,00为空余字节,aa供CRC8校验使用 (测试时未加入).发送端的业务时钟 fS采用 2.048MHz的频率,则 512分频后为 4 kHz的频率;然后用发送端的时钟 fT=25MHz对 4 kHz进行计数,则在一个周期内的典型脉冲数为 0x186a.

图 8 接收端 SignalTap显示结果Fig.8 Exper im ental result by SignalTap on the receiver

图 9 源时钟与恢复时钟对比Fig.9 Compar ison between source clock and recovered clock

图9显示了源时钟与恢复时钟的实测对比.测试结果表明,当源时钟平均抖动为 500 ps时,恢复时钟能控制在 5 ns以下,与理论仿真结果一致.

4 结 束 语

本研究提出的基于全双工以太网 IPG的源同步时钟传输方法,充分利用了全双工以太网中的 IPG和接收时钟同步于发送时钟 PHY层的特点,结合SRTS算法不会引入截断误差和累积误差的优势,将源时钟在接收端完整恢复.本研究所提出的同步方案是一种不受以太分组流量影响的新的带外同步时钟传输方法.

[1] IEEE Standards Association. IEEE standard for information technology-specific requirements—part 3:carrier sense multiple access with collision detection(CSMA/CD) access method and physical layer specifications[S].New York:IEEE,2005.

[2] 曹俊,陈健,宋英雄.利用快速以太网中 IPG进行数据传输的实现[J].上海大学学报:自然科学版,2005,11(3):221-225.

[3] AWEYA J,OUELLETTE M,MONTUNO D Y,et al.Circuit emulation services over Ethernet—part 1:clock synchronization using timestamps[J]. International Journal of Network Management,2004,14(1):29-44.

[4] GARDNER F M.Phase lock techniques[M].3rd ed.New York:John Wiley&Sons Inc,2005:139-150.

[5] LAU R C,FLEISCHER P E.Synchronous techniques for timing recovery in BISDN [J]. IEEE Transaction on Communications,1995,43:1810-1818.

[6] International Telecommunications Union. ITU-T Recommendation I.363.1,B-ISDN ATM adaptation layer(AAL)specification[S].Geneva:ITU,1992.

[7] COCKBURN B F,FRIESEN T,TSE D W K.Simplified jitter analysis and performance enhancing extensions for the SRTS mode of ATM AAL-1[C]∥Proceedings of IEEE Pacific Rim Conference on Communication,Computer and Signal Processing.1997:61-65.

[8] WALKER J,CANTONI A.Determining parameters to minimize jitter generation in the SRTSmethod[J].IEEE Transactionson Communications,1998,46(1):82-90.

[9] MURAKAM I K.Waveform analysisof jitter in SRTSusing continued fraction[J].IEEETransationson Communications,1998,46(6):819-825.

Source Synchron ized Clock Transm ission Based on Inter-Packet Gap of Full-Duplex Ethernet

CHEN Jian, ZHANGJun-jie, SONG Ying-xiong

(Key Laboratory of Specialty Fiber Optics and Optical Access Network,ShanghaiUniversity,Shanghai200072,China)

A source synchronized clock transmissionmethod isproposed based on inter-packet gap(IPG)of Ethernet running in a full-duplex mode.A synchronous residual time stamp(SRTS)is adopted as the clock transmission algorithm.The characteristic of the new method is immune to fluctuation for in-band Ethernet traffic.Parametersof the SRTSalgorithm used in Ethernet IPG and the output jitterwaveform of recovered clock are determined by using continued fraction.Simulation results and field programmable gate array(FPGA)implementation are given to demonstrate high quality of the recovered clock.

inter-packet gap (IPG); synchronous residual time stamp (SRTS); source clock synchronization

TN 919.3

A

1007-2861(2011)01-0044-07

10.3969/j.issn.1007-2861.2011.01.007

2010-04-06

上海市重点学科建设资助项目 (S30108);上海市重点实验室资助项目(08DZ223100);上海市科委基金资助项目 (08706201000)

陈 健 (1965~),男,副研究员,博士,研究方向为数字通信及接入网.E-mail:chenjian@shu.edu.cn

(编辑:赵 宇 )

以太网的设计初衷是互联本地计算机,并不是用作一个传输语音和视频服务的实时传输网络.在以分组交换为原理的以太网中涉及恒定比特率业务的传输,在与电路交换设备协同工作等的情况下,时钟及其同步是必须要考虑的因素.除了电信运营商有分组传输中时钟同步的需求外,在基于以太网的测试系统、实时工业控制系统和住宅以太网中,对端到端的时钟抖动和漂移也有严格的要求.

目前,建立在物理层 (PHY层)和介质访问控制子层协议 (media access control,MAC)层之间的精密同步时钟协议 IEEE 1588与建立在应用层的同步协议 (如简单网络时间协议 (simple network timep rotocol,SNTP)和网络时间协议 (network time protocol,NTP))相比,在定时精度上有了很大的提高.已发布的 ITU-T G.8261/Y.1361建议规定了通过分组交换网的定时分配特征,确定了同步以太网基于 PHY层硬件的时钟恢复机制.但是为了支持同步以太功能,网络中的所有交换机和路由器必须全部更新,这是其部署时面临的最大问题.