基于压缩感知的低功耗高效率CMOS图像传感器设计*

2011-10-19赵士彬姚素英徐江涛

赵士彬,姚素英,徐江涛

(天津大学电子信息工程学院,天津 300072)

CMOS 图像传感器(CMOS Image Sensor,CIS)以其单片集成、低功耗、体积小等特点,逐渐成为图像和视频采集的主流器件[1-3]。在现有图像视频采集处理系统中,图像传感器和图像压缩处理器往往彼此分离,部分传感器输出数据消耗了大量的功耗和带宽,却被压缩处理器过程舍弃,这将降低了系统整体功耗和带宽效率,限制其应用于图像视频无线传感网等需要低功耗且带宽压力较高的领域[4-5]。

近年来,压缩感知(Compressive Sensing)方法逐渐被引入到CIS的设计中,其设计思想核心在于借助CIS的单片集成特性将数据压缩过程集成于图像传感过程中,从源头削减舍弃图像的产生。Chi Y M等人将全部图像舍弃判别模块集成于像素级[6-8],Viktor Gruev等人则通过增加输出总线和时序优化等手段将图像储存、帧差求解和阈值判别等模块分别集成在像素级和列级[9-10],然而,这两种方法均无法兼顾像素面积、填充因子、固定模式噪声、灵敏度、图像储存精度和功耗等CIS关键指标。此外,上述方法一般采用基于图像舍弃标志位(Abandoned Flag Bit,AFB)的事件地址表示法[11](Address Event Representation,AER)读出像素阵列的模拟输出,既无法与现有的片上图像信号处理(Image Signal Processing,ISP)相兼容,也缺乏针对集成ADC的更深层次的功耗和效率优化。

为克服上述不足,本文提出了一种基于列总线复用的像素结构设计,其可以通过较小尺寸的像素面积和较低的功耗,同时兼顾像素感光灵敏度和数据储存精度。此外,提出了一种兼容于流水线型芯片级ADC结构的自适应读出量化方法,通过AFB的流水化实现了对舍弃和非舍弃图像的选择化处理。

1 压缩感知CIS的设计方法学

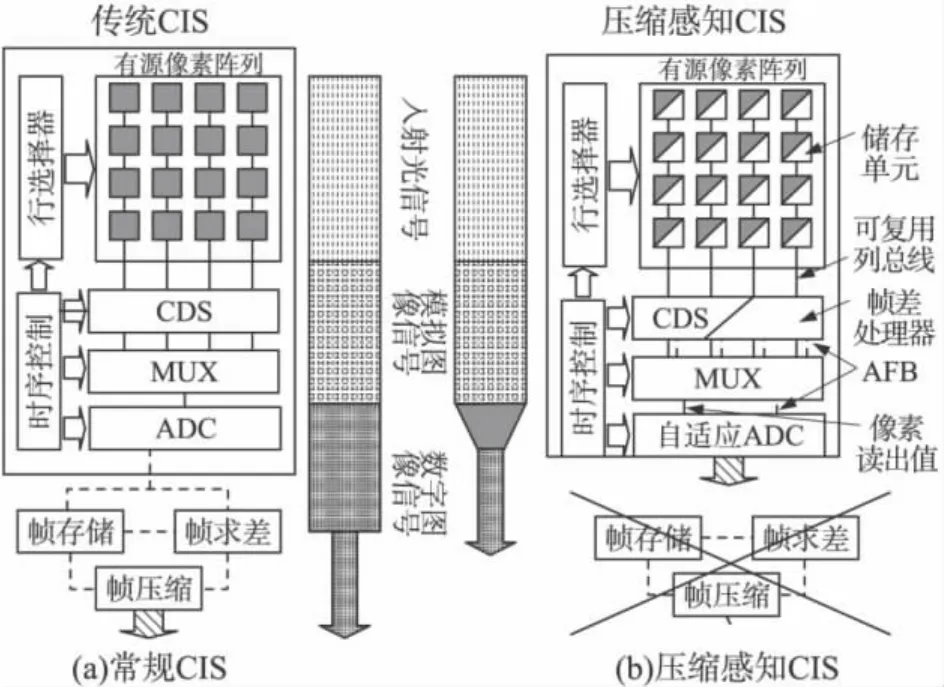

传统CIS的结构和工作流程如图1(a)所示。首先,像素阵列中的有源像素(Active Pixel Sensor,APS)在时序控制电路和行译码器的作用下进行复位和曝光以采样光信号。随后,像素复位信号和曝光信号通过相关双采样(CorrelativeDouble Sampling,CDS)和多路选择器(MUX)等信号调理和寻址电路形成像素读出值。其值经过集成ADC的量化后最终以帧为单位传送到ISP形成数字图像信号。ISP将相邻获取的本帧信号和储存在帧存储器中的参考帧信号进行求差处理,并将结果与设定的阈值比较以确定两帧之间未发生实质变化的像素数据为舍弃数据。最终,非舍弃数据将进行编码并得以储存。在上述过程中,无论是传感器对舍弃数据的感知还是压缩处理器对舍弃数据的压缩,都将消耗无谓的功耗、带宽和储存空间,最终阻碍图像采集处理系统效率的提升。

图1 两种图像传感器工作流程对比图

产生上述问题的根源在于传统图像传感器缺乏自我计算、识别和消除图像舍弃数据的能力,因此突破上述瓶颈的关键在于提高CIS的处理不同类型数据的智能性。易于单片集成是CIS最重要的优势,这就为在像素阵列内部集成储存单元提供了可行性。这种存储单元可以在不影响本帧图像感知的条件下保持并输出前帧图像感知信号,并通过像素级或列级集成的处理电路实现两帧图像的求差和阈值比较,获取像素读出值对应的舍弃标志位。更为重要的是,这些标志位可以用来进一步增强片上集成ADC的智能性,使其具有对不同类型的模拟图像信号具有选择性处理能力。

总之,这种新的图像传感过程是一种典型的压缩传感(Compressive Sensing,CS)过程。对于新的传感器结构而言,舍弃数据是“不可见的”,因此,也就无需在ISP中设置类似于传统CIS的片上图像压缩处理单元。这种将图像的压缩过程与传感过程相集成的设计方法学可以从源头削减舍弃数据,加强了感知和压缩的协同性,有效突破了传统CIS的效率瓶颈。

2 压缩感知CIS的电路结构

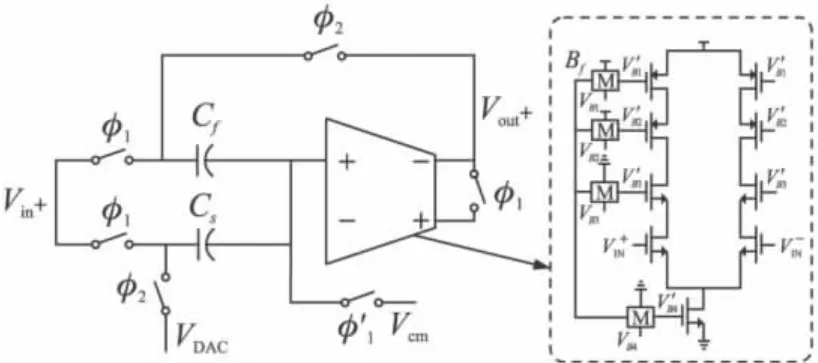

根据上述设计思想,我们提出一种压缩感知CIS结构,如图1(b)所示。其主要由像素级电路、列级电路和芯片级电路组成:

(1)像素级电路包含两部分:常规的有源像素和集成于像素中的存储单元,分别完成本帧光信号的采集和前帧光信号的储存记忆。两者通过共享的输出总线与列级电路相连。

(2)列级电路主要由常规的相关双采样(Correlated Double Sample,CDS)电路和列集成帧差处理器(Frame Difference Processor,FDP),分别用于读出信号消噪和舍弃标志位(Abandoned Flag Bits,AFB)的生成。此二者同样共享列总线,并经由多路选择器MUX分别将像素读出值和AFB输出到芯片级模拟和数字总线上。

(3)芯片级电路主要由基于自适应量化的流水线ADC组成,其可以同时采样像素读出值和AFB信号,且每级流水线均可根据AFB状态在压缩模式和量化模式之间进行切换,因此,可以保证非舍弃数据的量化和舍弃数据的压缩可同时进行而互不干扰。

2.1 基于输出总线复用的有源像素及其储存单元

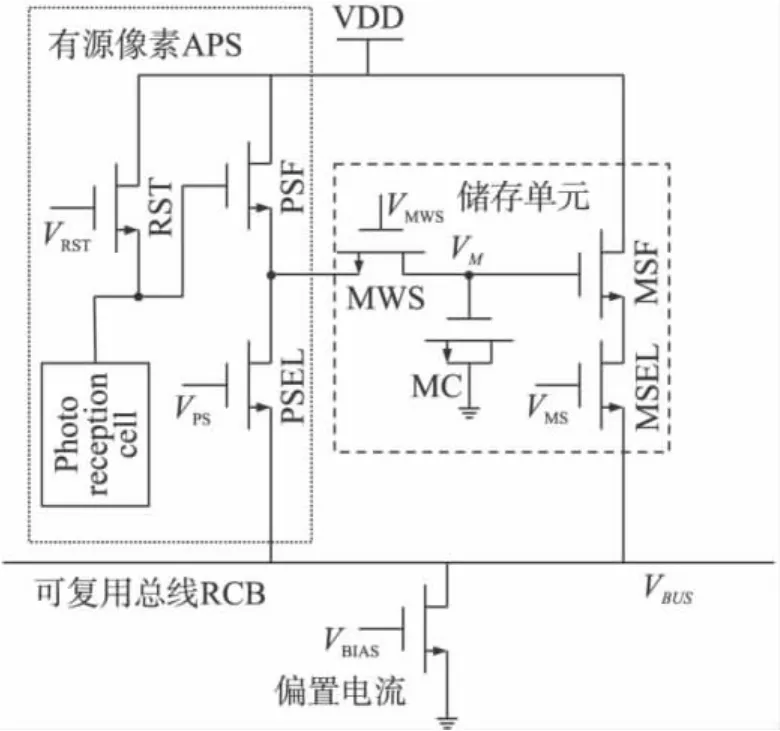

基于输出总线复用的有源像素及其储存单元结构如图2所示。其中复位管RST、源级跟随器PSF、选通管PSEL和感光单元(Photoreception Cell,PRC)组成有源像素APS,而存储写开关MWS、储存电容MC、源级跟随器MSF、选通管MSEL构成储存单元.这两者以PSF源级和可复用总线(Reused Column Bus,RCB)为端口互相连接,并共享列输出偏置BIAS。

图2 集成储存单元的像素结构图

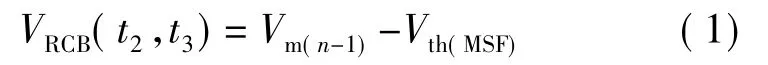

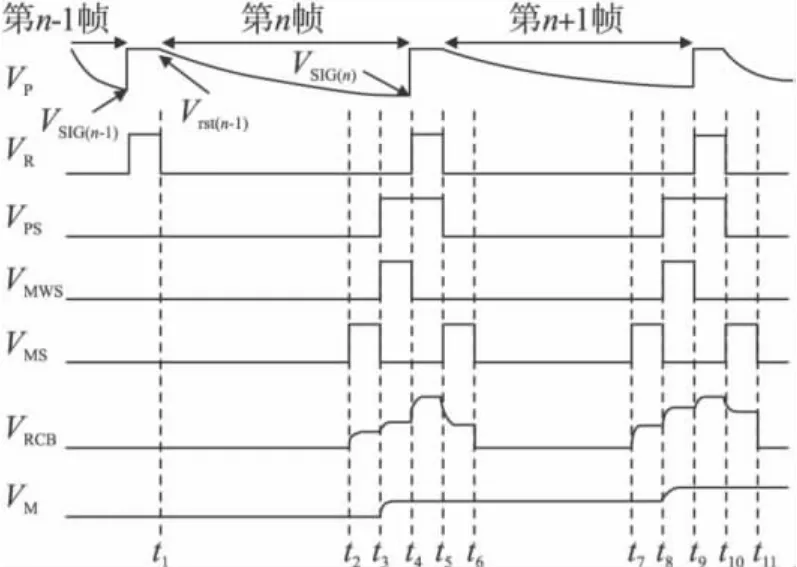

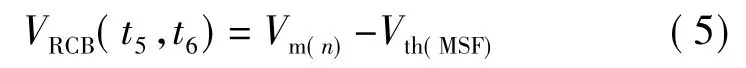

上述结构工作时序如图3所示。假设先后经历第n和n+1帧曝光,且后者光强大于前者。首先,在t1时刻,复位信号Vr下降,像素开始第n帧的曝光过程,正如下文分析所示,此时MC的栅极电压Vm正比例于第n-1帧曝光信号Vsig(n-1)。到t2时刻,存储单元选通信号Vms先于像素单元选通信号Vps变为高,此时 MSEL 被打开,Vm(n-1)经 MSF 缓冲读出到RCB上,此时RCB电压表达式为:

其中Vth(MSF)为MSF阈值电压,其值在不同像素之间存在差异,并构成主要的固定模式噪声(Fixed Pattern Noise,FPN)。待FDP对此RCB电压完成采样后,MSEL关断,PSEL开启,t1至t3时间内第n帧曝光信号经PSF缓冲读出到RCB上,其表达式为:

与此同时,Vmws置高将MWS打开,MC电压被更新为VRCB(t3,t4),待刷新完成后,MWS 断开,Vr升高开启RST管完成RPC的复位,此时RCB电压表达式为:

在t3至t5时间段内,CDS电路采样上述两信号,并求差形成第n帧像素读出信号Vread(n),其表达式为:

图3 集成储存单元像素工作时序图

上述采样完成后,PSEL在t5时关断使得RCB处于空闲状态,此时像素操作类似于前述t2时刻,Vms再次升高,将此时的Vm(n)输出到RCB上,此时RCB电压表达式为:

此时,FDP采样此信号,并与先前完成采样的VRCB(t5,t6)进行求差处理。假设不考虑随机噪声的影响,其两帧复位电压可以认为相等,则求差的结果可以代表帧差信号,其表达式为:

显而易见,上述帧差信号中并不含有MSF或PSF的阈值电压,这意味着帧差信号和经CDS产生的像素读出值一样同样不会受到FPN的影响。上述时序设计同样适用于从t5到t11的n+1帧的操作过程。

上述CDS和FDP电路的细节描述已经发表在我们先前的论文[12-13]中。其CDS结构不仅可以消除像素级FPN,而且可以消除列级FPN,且芯片占用面积小,可以为FDP电路的列级集成提供足够空间。与其他整体在像素级集成的方案相比,所采用的FDP在电路面积方面的限制大大降低,更为复杂和精确的检测电路结构可以被采用。通过上述两模块的操作,高精度低FPN的像素读出值和AFB最终可以被储存在列级。在MUX的寻址选通下,这两个信号分别被输出到全局模拟和数字总线上,供芯片级自适应ADC使用。

从上述分析可以看出,所提出的像素结构与其他相类似的方案相比[6-12],主要具有以下两个优点:

(1)列总线复用一方面使得储存单元的读出无需额外增加偏置电流,可有效降低CIS阵列工作所需功耗;另一方面,也可以保证相邻两帧的曝光信号可以从同一个源级跟随器缓冲读出,有效避免FPN对于帧差检测的干扰。

(2)由于存储单元与感光单元完全隔离,二者可以根据其各自特性分别进行优化以期获得更加良好的折衷性。例如,储存电容可以增大以避免寄生二极管泄漏电流的影响,与此同时,PRC中的感测电容则可以减小,以期获得更高的感光灵敏度。

2.2 基于芯片级流水线ADC的自适应读出量化方法

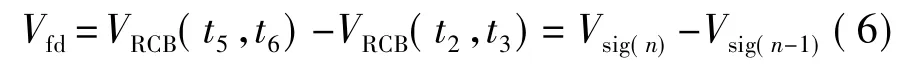

单片集成ADC进行读出信号的片上量化是CIS超越CCD传感器的主要特点之一,CIS集成ADC按其集成位置可分为像素级ADC、列级ADC和芯片级ADC三种。相比前两者,芯片级ADC可以被全阵列共享,对列FPN没有影响,且通过流水线处理其总体占用功耗较低,正在逐渐成为低功耗高分辨率CIS集成ADC的主流选择[14-15]。对应于前述像素读出值及其相应的舍弃标志位,压缩感知CIS集成ADC需要两种工作模式:正常模式与常规ADC操作相同,完成对非舍弃读出信号的正常量化;压缩模式则需要完成对舍弃数据的消减,同时避免处理舍弃信号所消耗的无用功耗。由于舍弃和非舍弃数据往往相互杂糅,上述两模式相互切换所需时间必须尽可能的短,以便减小互扰,即实现模式切换的“无缝化”。然而,常规流水线ADC的处理延迟使得同一时刻各级处理数据并不属于同一个像素读出值,以流水线ADC为整体进行模式切换必然造成舍弃和非舍弃数据处理的相互干扰,无法满足“无缝化”的要求。因此,需要对常规流水线ADC进行电路设计及其相关时序操作的调整,使得各个流水级在独立的模式切换控制信号作用下进行相应的电路操作,根据待量化信号的类型进行自适应量化处理,其基本结构如图4所示。

图4 基于芯片级流水线ADC的自适应读出量化结构图

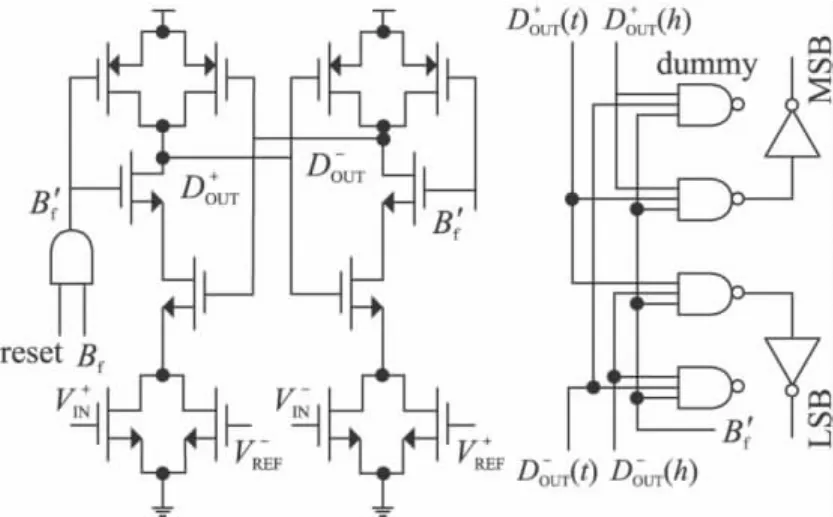

2.2.1 面向流水线级模式控制的电路设计改进

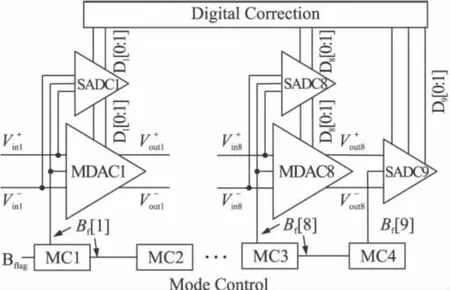

流水线型ADC对于信号量化最为重要的两个核心模块是MDAC中的开关电容放大器和Sub-ADC(SADC)中的动态比较器。前者通过采样保持过程实现量化信号的调理和级间传递,决定了信号流水线操作的量化精度,且是功耗消耗的主要部分;后者则在采样保持时钟作用下完成信号和内建阈值电压的比较,是产生量化输出的主要单元。因此,面向两种模式的电路设计改进也主要针对这二者进行:

图5 MDAC结构示意图

(1)MDAC的调整主要针对运放放大器的偏置电压产生,如图5所示,当Bf信号为高时,双向选通开关M将放大器除输入对管外的其他待偏置MOS管栅极接通到对应得偏置电路电压输出信号上,放大器偏置正常,进入正常模式;反之,M将这些栅极接通到对应的电源线上(PMOS为VDD,NMOS为GND),放大器无法正常偏置静态电流,进入压缩模式。双向选通开关M的主要作用在于隔离偏置电压输出信号线和待偏置MOS管栅极,避免了从压缩模式到正常工作模式切换时由于偏置电压的重新建立延长切换所需时间。

(2)动态比较器及DAC由于不包含静态电流,因此其调整主要针对工作时序。当Bf信号为高时,常规的复位信号reset可以正常通过与门对比较器和DAC施加作用,此时两电路均工作在正常模式;当Bf信号为低时,Bf信号将reset信号屏蔽,一方面将比较器保持在复位状态,减小其输出电压翻转带来的动态功耗耗损,另一方面将DAC的输出进行置位,使每级输出的MSB和LSB始终都保持为0。

图6 SADC结构示意图

2.2.2 面向流水线级模式控制的控制时序设计

根据前述分析,常规流水线ADC无法以整体进行模式切换的主要原因在于流水线操作自身的延迟。因此,实现各级独立的模式切换关键在于舍弃标志位也要同步于其对应像素读出值的处理在流水线级间进行传递,即各级模式控制模块(Mode Control,MC)对舍弃标志位的采样同样采用类似于ADC的流水线处理。首先,MC的控制时钟周期必须与采样保持时钟周期保持相等。其次,后级MC对前级的采样点应选择在前级MDAC保持放大而本级MDAC采样的时刻,为了简化起见,下面以流水线前两级处理第n-1,n和n+1次像素读出值的电路操作和时序关系为例进行对选择此时刻作为采样点进行说明。

图7 Bf信号时序延迟示意图

(1)t1~t2时间内,MDAC1和MC1分别对第n-1个像素读出值及其对应的舍弃标志位Bflag(其值为0)进行采样,输出第一级模式控制信号Bf1为0。此时MDAC1将进入压缩模式,运算放大器在Bf1的作用下关断所有的栅极信号,即将其静态直流电流IDD1置零。SADC中的比较器完成相应复位操作。

(2)t2~t3时间内,Bf1信号保持0,仍处于压缩状态的MDAC1无法对前述采样值进行余数求差,且reset信号同时仍被Bf1信号所屏蔽,比较器仍然处于复位工作状态,对应的MSB1和LSB1输出均为0。至此,第一级流水线级完成了对第n-1个像素读出值的压缩处理。然而,Bf1此时所代表的舍弃标志位必须传递到下一级模式控制模块MC1中,才能最终使得整个ADC实现对此数据的压缩处理。因此,在t2时刻,MC2对Bf1进行采样形成Bf2,舍弃标志位0传递到第二级流水线,t2~t3时间内的MDAC2的工作过程类似于t1~t2时间内的MDAC1,同样对第n-1个像素值保持了压缩模式的处理。

(3)t3~t4时间内,MDAC1和MC1继续对第n个读出值和舍弃标志位进行采样,此时第n个读出值为非舍弃数据,对应采样后的Bf1为高,MDAC1此时将进入正常模式,运算放大器的栅极重新与偏置电压相连,IDD1恢复到正常水平。而此时MDAC2和SADC2在Bf2的控制下仍工作在压缩模式,类似于t2~t3时间内的MDAC1和SADC1,仍保持低功耗和无量化数据输出的状态,实现了第二级流水线队第n-1个像素值的压缩操作。

(4)t4~t5时间内,Bf1仍为高,MDAC1和SADC1均保持正常模式,余数求差得以正常进行,并将求差结果输出到Vout1总线上供后续流水线级进行采样;Bf1信号也解除了对Reset信号的屏蔽作用,SADC也可以完成对非舍弃数据的量化操作,MSB1和LSB1为有效值,第一级流水线级完成了对第n个像素读出值的正常量化转换;在t4时刻,MC2再次对Bf1进行采样,Bf2置高,第n个读出值的舍弃标志位传递到Bf2上,t4~t5时间内的MDAC2和SADC2的工作过程类似于t3~t4时间内的MDAC1和SADC1,同样对非舍弃信号保持了正常模式的处理。

可以看出,上述电路操作过程同样适用于t4至t7时间内从非舍弃数据n到舍弃数据n-1的模式切换,这里不再赘语。综上所述,通过上述电路设计改进和相应的控制时序设计,在类似于t3~t4和t5~t6这样舍弃数据和非舍弃数据的过渡期,各流水线级可以独立根据各自的控制信号进行相应模式的电路操作,通过进一步的优化设计,切换时间基本可以保证不干扰切换后模式的正常作用,完全满足了压缩感知CIS集成化ADC的要求。

3 芯片测试结果

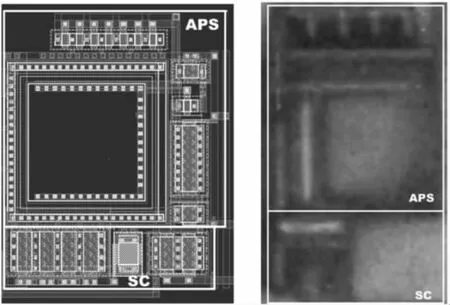

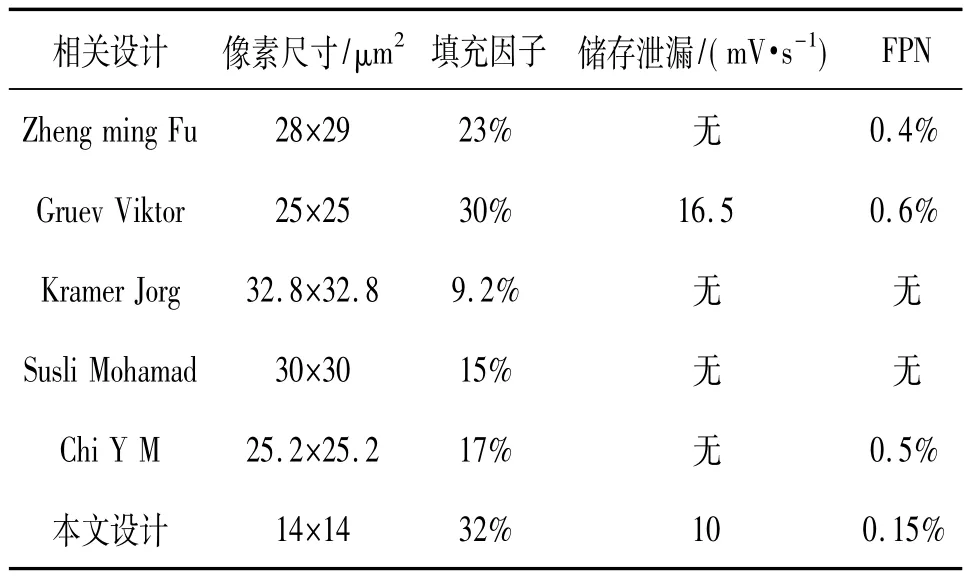

上述压缩感知CIS已利用Global Foundry 0.18 μm Dual Gate Mixed-Signal Process进行了物理设计和投片验证。图8为基于输出总线复用的有源像素及其储存单元的版图和芯片照片,有源像素APS和储存单元SC标注如图所示,其主要指标与其他已发表设计的对比如表1所示。结果显示本文所提出的基于总线复用的有源像素APS集成储存单元SC的方案可以在保持较高的填充因子的条件下有效降低像素尺寸,并且可以通过金属掩蔽、增大栅电容、优化源漏面积等方法进一步降低储存单元的泄漏电流水平。总线的复用时序也使得像素读出值和帧差值都可以避免FPN的影响,从而从整体上降低了FPN的影响。

图8 有源像素及其储存单元版图设计和芯片照片

表1 基于总线复用的像素设计和相关已发表设计特性对比表

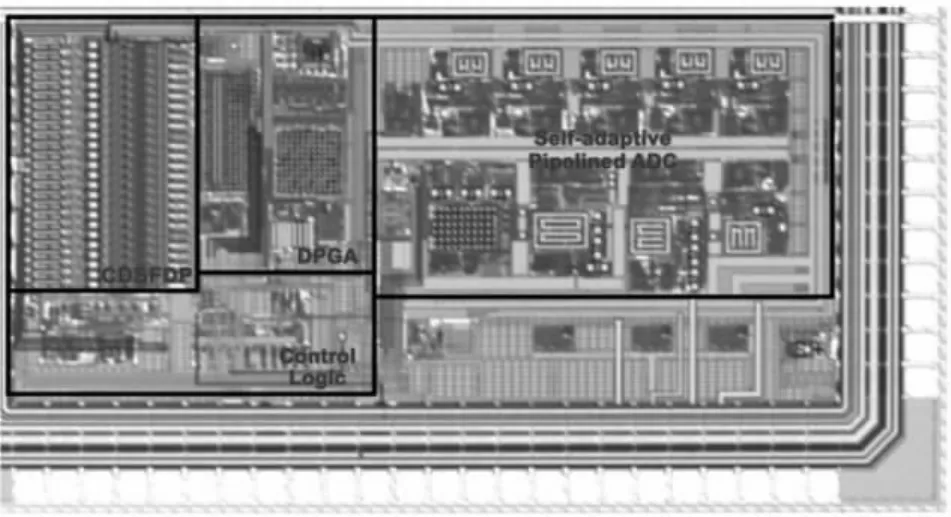

图9为列级和芯片级电路的版图照片,在电路设计中加入了数字可编程增益放大器(Digital Programmable Gain Amplifier,DPGA)用于调节 CDS 电路输出的像素读出值幅度,并对控制逻辑部分(Control Logic)进行了调整使其可以通过外部时序控制将AFB与自适应流水线ADC(Self-adaptive pipelined ADC)相隔绝,并控制ADC在整个量化过程中完全处于正常模式或压缩模式,因而增强了测试方案的灵活性。

图9 列级和芯片级电路的版图照片

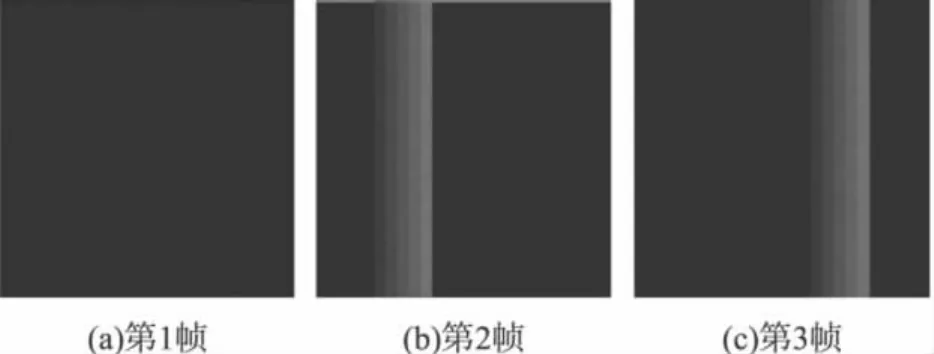

整体测试方案分3帧进行:第1帧作为参考帧,通过逻辑控制模块隔离ADC与AFB,并将ADC始终置于正常工作模式,此时对应的像素阵列的光输入为无光照的黑暗背景;随后,令一条格光源自左向右运动至像素阵列和黑暗背景之间,先后完成第2帧和第3帧采样,此时逻辑控制模块去除AFB和ADC的阻隔信号,开始自适应读出量化过程。

图10 条格光源帧间运动测试结果

最终的3帧图像输出结果如图10所示。其中,图10(a)为第1帧参考帧,由于像素阵列和读出量化电路均工作在正常状态,像素KTC噪声和闪烁噪声等随机噪声使得无光照的黑暗背景存在一定程度的噪声影响;图10(b)为第2帧图像,此时自适应读出机制已通过外部控制信号激活,像素阵列可以识别出已运动至阵列左侧的条格光源为非舍弃数据,其余部分像素阵列的输入仍为未变化的黑暗背景,为舍弃数据,通过观察分析可见,条格光源区域由于自适应读出电路处于正常模式,因此在第1帧中存在的随机噪声仍可见,但在其他区域由于自适应读出电路处于压缩工作模式,输出的图像灰度均为0,以无法观察到随机噪声;图10(c)为第3帧图像,此时条格光源已经从阵列左侧运动至右侧,一方面第2帧中条格光源所在的像素阵列部分输入变为黑暗背景,另一方面两帧之间条格光源又运动至阵列右侧区域代替了部分黑暗背景作为像素阵列的输入,因此这两部分均被识别为非舍弃数据,对应的自适应读出电路将保持正常状态,两区域均可观察到随机噪声的影响,而其他区域的输入仍为未变化的黑暗背景,被识别为舍弃数据,输出图像灰度均为0,且无法观察到随机噪声的影响。纵上所述,无论是CDS/FDP对像素信号和帧差信号的读出处理,还是基于芯片级ADC的自适应读出量化电路均工作正常,配合良好,符合前述压缩感知CIS的要求。

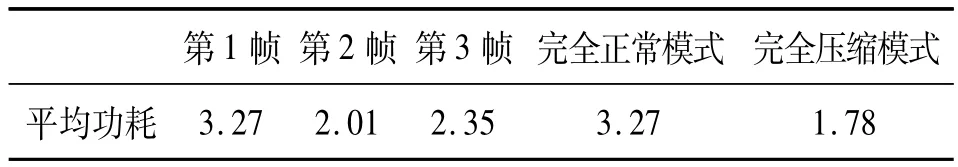

最后,分别对3帧图像以及完全工作在正常模式和压缩模式所对应的ADC平均功耗进行统计和计算,列表如表2所示。结果显示第1帧即正常工作模式下功耗最高,完全压缩模式功耗最低,约为正常值的54%;第2、3帧为正常模式和压缩模式混杂的情况,且第3帧所含非舍弃数据多于第2帧,平均功耗相应也较高,两者分别为正常值的61%和71%。

表2 各种工作情况下ADC平均功耗统计表 单位:mW

综上所述,本文所提出的压缩感知CIS在兼容传统芯片级ADC的条件下,可以有效削减舍弃数据处理带来的无谓功耗消耗,并完成对于舍弃数据的实时压缩。

4 结论

本文利用基于输出总线复用的有源像素及其储存单元以及基于芯片级流水线ADC的自适应读出电路,设计了一种压缩感知CIS。理论分析和测试结果表明,其可以在兼顾像素面积、填充因子、固定模式噪声、灵敏度、图像储存精度等关键CIS指标的前提下,同时输出正常像素读出值和对应的舍弃标志位,并可以利用舍弃标志位实现舍弃数据和非舍弃数据的自适应处理,有效提高了芯片的功耗效率,

实现了传感过程和压缩过程在CIS上的集成。结果表明,本CIS设计可适用于图像视频无线传感网等需要低功耗且带宽压力较高的领域。

[1]Theuwissen A J P.CMOS Image Sensors:State-of-the-Art[J].Solid-State Electron,2008,52(9):1401-1406.

[2]El Gamal A,Eltoukhy H.CMOS Image Sensors[J].IEEE Circuits and Devices Magazine 2005,21(3):6-20.

[3]Bigas M,Cabruja E,Forest J,et al.Review of CMOS Image Sensors[J].Microelectronics Journal,2006,37(5):433-451.

[4]陆洲,王宝光.基于FPGA的嵌入式彩色图像检测系统[J].传感技术学报,2007,20(3):618-622.

[5]王永灿,冯远静,俞立.基于无线视频传感网的高压塔架监控系统研究[J].传感技术学报,2008,21(12):2039-2043.

[6]Chi Y M,Mallik U,Clapp M A,et al.CMOS Camera with in-Pixel Temporal Change Detection and ADC[J].IEEE Journal of Solid-State Circuits,2007,42(10):2187-2196.

[7]Kramer J.An on/offTransientImager with Event-Driven,Asynchronous Read-out[C]//IEEE International Symposium on Circuits and Systems,Arizone,IEEE,2002:165-168.

[8]Susli M,Boussaid F,Shoushun C,et al.Efficient Event-Drivern Frame Capture for CMOS Imagers[C]//9th International Symposium on Signal Processing and Its Applications,Sharjah,IEEE,2007:1-3.

[9]Gruev V,Etienne-Cummings R.A Pipelined Temporal Difference Imager[J].IEEE Journal of Solid-State Circuits,2004,39(3):538-543.

[10]Dickinson A,Ackland B,Eid E S.A 256×256 CMOS Active Pixel Image Sensor with Motion Detection[C]//IEEE International Solid-State Circuits Conference,San Francisco,IEEE,1995:226-227.

[11]Culurciello E,Etienne-Cummings R,Boahen K.Arbitrated Address Event Representation Digital Image Sensor[C]//IEEE International Solid-State Circuits Conference,San Francisco,IEEE,2001:92-93.

[12]Zhao Shibin,Yao Suying,Xu Jiangtao,et al.Smart APS Pixel with Full Frame Self-Storage and Motion Detection Capabilities[C]//International Symposium on Photoelectronic Detection and Imaging,2009,Proc.SPIE,7384:73842R-73842R-6.

[13]Zhao Shibin,Yao Suying,Nie Kaiming,et al.Area-Efficient Low Power CMOS Image Sensor Readout Circuit with Fixed Pattern Noise Cancellation[J].Transactions of Tianjin University,2010,16(5):342-347.