一种新颖的捷变频频率合成器设计

2011-09-28王立生

王立生

(成都天奥电子股份有限公司,成都611731)

1 引 言

目前,数字频率合成器的基本设计方法主要分为两大类,即基于锁相环(PLL)的间接频率合成和基于直接数字频率合成器(DDS)的直接频率合成。随着电子技术的日益发展,具有高集成度的新器件不断推出,使得基于PLL的频率合成设计愈加简便,有利于小型化通用化设计,其主要技术指标优良,已经成为主流设计方法。但是,由于PLL自身的固有特性,作为一个相位负反馈系统,本身是一个惰性环节,其锁定时间较长(通常是几十微秒至几百微秒),无法应用于对跳频时间要求高的场合。而DDS在频率转换时间上有明显优势(纳秒量级),且具有频率分辨率极高的特点,非常有利于实现细步进捷变频设计。但DDS也有明显不足,输出频率较低、带宽较窄、杂散较丰富是主要缺点[1]。

工程上需要一种工作在C频段的频率合成器,要求实现优于3 μ s的捷变频指标,PLL方案不能满足跳频时间要求,只能采用基于DDS的直接合成设计方法。考虑到DDS受限于器件自身特性无法实现高频率输出,且带宽较窄,因此设计思路的重点在于降低DDS输出信号频率,压缩DDS输出信号带宽,通过精心规划频率关系,在充分发挥DDS跳频时间上的优势的同时,实现低杂散指标要求。

2 主要技术指标和设计方法

频率合成器主要技术指标如下:工作频段为C频段,信号带宽600 MHz,频率步进1MHz,跳频时间优于3 μ s,相位噪声优于-90 dBc/Hz@10 kHz,杂散抑制优于60 dBc,谐波抑制优于40 dBc,输出功率优于10 dBm。本频率合成器的主要技术难点是要求优于3 μ s的跳频时间,PLL无法实现,必须采用DDS直接合成方案。基于DDS实现的捷变频频率合成器设计方法有采用DDS直接倍频后再混频进行频谱搬移的方案[2],或采用DDS输出信号作为参考源直接驱动PLL的锁相倍频方案[3]。前一方案的局限在于不能实现宽带信号输出,且倍频次数高会恶化杂散指标;后一方案的不足之处在于其跳频时间主要取决于PLL的锁定时间,为数十微秒量级,不能满足本项目指标要求。本方案采用了新颖的频率关系设计,选择DDS+开关变频+分段滤波+直接倍频实现,发挥了DDS捷变频的特点,在尽量避免恶化杂散的同时有效拓展了输出信号带宽。方案框图如图1所示。

图1 频率合成器方案框图Fig.1 Block diagram of the frequency synthesizer

DDS用来产生具有一定带宽、细步进的低频信号,通过微波混频器与本振信号混频,实现频谱搬移,提高了输出频率;频率合成器需要输出信号带宽600 MHz,通过采用直接二倍频器、开关切换两个混频本振的方式,将DDS输出信号Fdds带宽压缩为150 MHz,有效解决了DDS输出信号带宽较窄、难以在宽带场合应用的缺点。对由变频器的非线性产生的无用边带信号、交调杂散成分以及本振信号泄漏,在混频器输出端采用分段开关滤波器组,将信号分为4段,每段信号带宽75 MHz,分别进行窄带带通滤波,大大降低了带通滤波器的设计难度,使得对信号的滤波能够实现,从而获得良好的杂散抑制指标。

混频器本振信号采用两个L频段点频源,通过开关切换输出,DDS与本振LO1混频选取上边带信号,与本振LO2混频选取下边带信号,使得两个本振信号位于所需信号带外,混频后经过带通滤波器组分为4段分别带通滤波,其频率关系如图2所示。

图2 频率关系Fig.2 Relationship of frequency

对DDS器件的选择,从提高频率合成器的性能指标考虑,应选择时钟频率高、DAC位数高、SFDR低的器件。经过综合考虑,选择 ADI公司的AD9912,时钟频率1 000 MHz,内部集成14位DAC,当输出201 MHz时窄带SFDR高达-91 dBc(±250 kHz),宽带 SFDR也有 -61 dBc(0~500MHz),采用高速SPI串口实现频率控制。

作为DDS时钟的1 000 MHz点频源和2个L频段点频本振信号均由PLL实现,外部输入10MHz晶振信号作为PLL的参考,通过3个SPDT开关对2个混频本振信号进行切换。混频后的开关滤波器组由4个介质带通滤波器、2个SP4T开关和4个SPDT开关构成,其中4个介质带通滤波器是关键器件,每个滤波器的1 dB带宽为75 MHz,带外抑制优于70 dB。在每一个滤波支路中串入一个SPDT开关是为了进一步提高路间隔离度,优化杂散指标。

接口控制电路采用高速FPGA器件,实现对DDS频率设置、本振选择开关和开关滤波器组状态的控制。

3 主要指标分析计算

3.1 跳频时间分析计算

由于频率合成器是基于DDS的直接频率合成设计,无PLL惰性环节,因此其频率转换时间取决于DDS的频率转换时间和开关通断状态切换时间。DDS的工作原理是在输入参考时钟的控制下,相位累加器对频率控制字进行累加,得到的相位码对波形储存器寻址,输出对应的幅度码,经过D/A转换器和低通滤波器得到所需模拟信号输出。由上述DDS频率产生过程可知,DDS的频率转换包括DDS频率控制字的译码计算、DDS频率控制字的SPI串口写入和DDS自身频率切换3个过程。FPGA控制开关切换过程可以与DDS的频率控制并行进行,根据所选开关资料,其最长开关切换时间为150 ns,远小于DDS的频率转换时间,因此频率合成器的跳频时间等于DDS的频率转换时间,如图3所示。

图3 频率转换时间示意图Fig.3 Diagram of frequency switching time

外部输入并口控制信号实现频率控制,通过高速FPGA实现频率控制字的译码,产生对应的DDS串口控制字和开关控制电平。FPGA时钟信号75 MHz,一个指令周期时间为13.3 ns。为最大限度缩短译码计算时间,DDS频率控制字的译码计算由FPGA采用硬件乘法器实现,每次计算需要20个指令周期,则DDS频率控制字译码计算时间为267 ns。

AD9912的SPI串口最高时钟频率为50 MHz,控制产生一个频率需要写入64 bit数据,选用SPI控制时钟频率37.5 MHz,则SPI串口送数时间为64/37.5=1.7 μ s。根据经验数据,AD9912的频率切换时间小于100 ns。

因此,可以计算出DDS频率转换时间(即频率合成器跳频时间)为267 ns+1.7 μ s+100 ns=2.067 μ s。

3.2 杂散分析

本频率合成器的杂散成分主要有以下来源:DDS产生的杂散、混频器非线性引入的频率交调产物、点频PLL的鉴相频率泄漏、倍频器产生的杂散。

DDS的杂散主要来源于3个方面:相位截断误差、幅度量化误差和DAC的非线性[4]。本方案中DDS选择的是AD9912,具有优良的杂散性能,当时钟信号为1 000MHz时在所需频段内近端杂散优于-90 dBc,完全满足要求,而DDS的宽带杂散可以依靠开关滤波器组中的介质带通滤波器抑制。

DDS输出信号与两个本振混频,除了得到所需频率信号外,由于混频器的强烈非线性作用,还产生了大量组合杂散信号。在方案设计上,对两个混频本振分别采用高、低本振方式,使得本振信号落在所需信号带外,以便于滤波器滤除;对两个混频本振分别采用单刀单掷开关以提高本振之间的隔离度;对混频后的宽带射频信号,采用开关切换分段滤波器组,各段均采用单刀单掷开关提高隔离度。

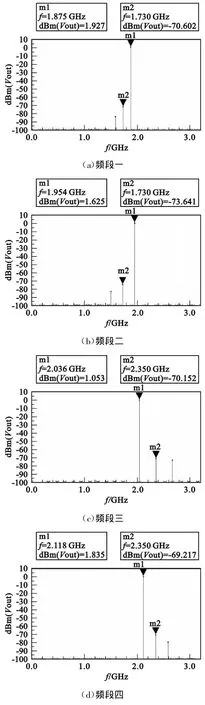

用谐波平衡法对混频+开关滤波器组的输出频谱进行仿真,如图4所示。由仿真结果可以看出,采用分段滤波器组有效滤除了带外组合交调成分,输出信号杂散主要为混频本振泄漏和无用边带频率成分,其抑制指标取决于各段窄带带通滤波器的指标。从仿真结果看,开关滤波器后输出信号杂波抑制优于70 dB,由于后级二倍频恶化6 dB,最终输出信号杂波抑制约为64 dB。

图4 混频杂散仿真结果Fig.4 Simulation results of spur at mixer

频率合成器中 3个点频源鉴相频率均为10 MHz,由于鉴相频率较高,通过合理选择环路带宽,加强电源滤波隔离,能够对10 MHz鉴相参考信号实现很好的抑制,可以达到约75 dB的抑制度,经过后级二倍频恶化6 dB,输出信号对10MHz的鉴相杂散抑制约为69 dB。

二倍频器采用无源器件,输入基波激励电平15 dBm,倍频损耗约15 dB,对基波、三次谐波、四次谐波的隔离度为45 dB(相对于输入电平),因此二倍频输出信号对基波、三次谐波、四次谐波抑制度为30 dB。在倍频后采用带通滤波器,可以实现65 dB的杂散抑制度。

4 测试结果

基于以上方案设计出的捷变频频率合成器,其外形尺寸为205 mm×80 mm×22 mm(内部还包括了一个S频段双路输出点频源)。测试频率合成器跳频时间的方法如下:设置频率合成器在两个频点间跳频,与信号源输出固定点频信号下混频,得到的L频段的中频跳频信号送入高速示波器DPO7254。采用示波器抖动分析模块,分析区域选择垂直光标范围包含两次跳频周期,通过软件进行一次测量生成图表,即可读出跳频时间约为2.2 μ s,测试结果见图5。

图5 跳频时间测试结果Fig.5Measured result of frequency switching time

用Aglient公司频谱仪E4440A,测试输出信号杂散指标为-63 dBc,相位噪声-93 dBc/Hz@10 kHz,其余各项指标均满足设计要求。

5 结论

本文介绍了一种采用直接频率合成方案设计的频率合成器,针对捷变频这一关键技术指标提出了设计思路和实施方案,实测各项技术指标满足要求且与分析论证结果吻合,产品已经应用于某舰载电子设备中。本项目的成功研制,提供了一种同类型捷变频频综器的设计方案,具有较高的应用价值。今后的研究方向应针对超宽带应用领域,进一步提高频率捷变时间和实现更低的杂散抑制指标。

[1]杨木意,鲍景富.现代频率合成技术的研究进展[J].电讯技术,2007,47(4):1-5.YANG Yi,BAO Jing-fu.Research Progress of Frequency Synthesis Techniques[J].Telecommunication Engineering,2007,47(4):1-5.(in Chinese)

[2]阚玉利,王振容,薛明华.捷变频频综源研究[J].电子测量技术,2006(4):27-28.KAN Yu-li,WANG Zhen-rong,XUE Ming-hua.Research on Frequency Synthesis Source[J].Electronic Measurement Technology,2006(4):27-28(in Chinese)

[3]梁强,杨永跃,陈仁北.捷变微波频率合成器的设计[J].国外电子测量技术,2006(8):39-42.LIANG Qiang,YANG Yong-yue,CHEN Ren-bei.Design Scheme of an Agile Microwave Frequency Synthesis[J].Foreign Electronic Measurement Technology,2006(8):39-42.(in Chinese)

[4]刘兰坤,潘明海.DDS的杂散分析及降低杂散的方法[J].电子器件,2007,30(2):572-574,578.LIU Lan-kun,PAN Ming-hai.Spurious Signals Analysisof Direct Digital Frequency Synthesizer and Spur Reduction Techniques[J].Chinese Journal of Electronic Devices,2007,30(2):572-574,578.(in Chinese)