74LS161异步置零法构成任意进制计数器的Multisim仿真

2011-09-19任骏原

任骏原

(渤海大学 数理学院物理系,辽宁 锦州 121000)

Multisim仿真软件是由加拿大InteractiveImageTechnologies公司开发的一种基于SPICE工业标准的EDA软件,它就像一个真正的实验工作台,将电路原理图的输入、虚拟仪器的测试分析和结果的图形显示等集成到一个设计窗口[1-3]。

在用Multisim仿真软件进行计数器状态变化过程波形仿真分析时,用虚拟仪器中的字组产生器做实验中的信号源产生所需的各种输入信号,用四踪示波器观测输入、输出波形,可直观描述计数器的工作特性,且解决了计数器工作波形无法用实际电子实验仪器进行分析验证的问题[1]。

1 74LS161的功能及异步置零法

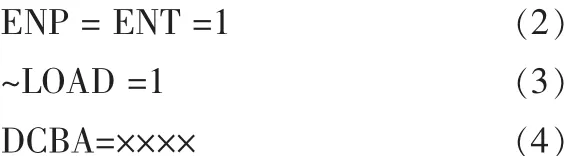

74LS161是集成4位二进制加法计数器[1-2],功能表如表1所示。其中CLK为时钟脉冲输入端、ENP及ENT为计数控制端、~LOAD为预置数控制端、~CLR异步置零控制端、DCBA为预置数输入端、QDQCQBQA为状态输出端、RCO为进位输出端,单片74LS161有从0000~1111共16个计数状态。

利用74LS161的预置数控制端~LOAD或异步清零端~CLR在计数循环过程跳过2n~N个状态,可构成任意N(N<2n)进制计数器,基本方法有置零法和置数法[1-2]。

用异步置零法将74LS161构成任意进制计数器时,使用计数和异步清零功能:用计数功能完成0~过度状态(最后一个有效状态 +1的状态)的状态转换、将过渡状态进行译码产生~CLR=0的异步置零信号在过渡状态异步清零。

过渡状态持续时间极短,~CLR=0的异步置零信号形成并完成置零后立刻消失。

过渡状态非完全译码时,仅由过渡状态中为1的Q端状态产生~CLR=0 信号,~CLR 的逻辑表达式为[1-2]:

即~CLR等于过渡状态中值为1状态变量的与非。

74LS161的其他控制端、输入端的逻辑表达式为[1-2]:

表1 74LS161功能表Tab.1 Function table for 74LS161

2 异步置零法Multisim仿真方案设计

2.1 异步置零法的状态图及仿真方案设计要求

用Multisim10版本以构成10进制计数器为例,说明Multisim仿真方案设计。

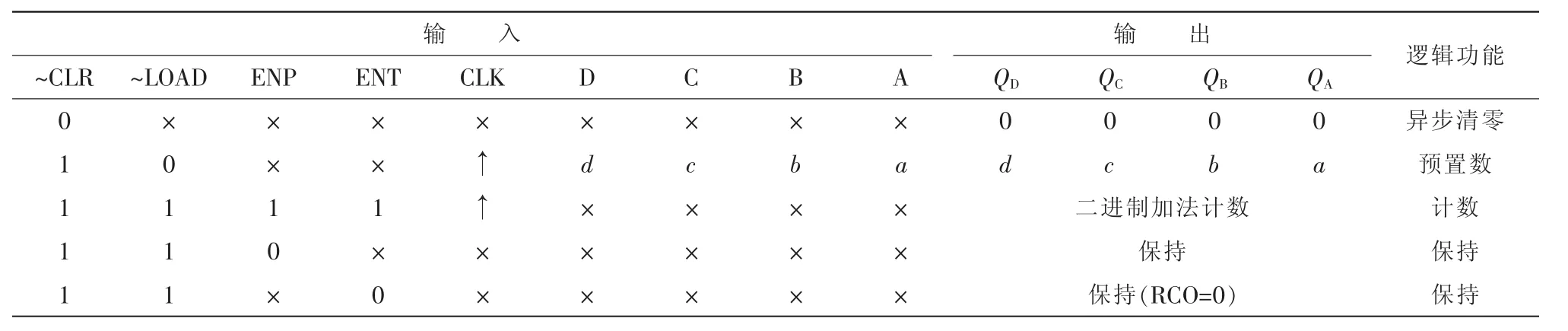

异步置零法10进制计数器的状态图如图1所示,其中0000~1001为正常计数的状态,过渡态为QDQCQBQA=1001+1=1010,1010过渡状态形成~CLR=0信号完成置零后消失,作用10个时钟脉冲完成一个计数周期的循环。

图1 异步置零法的10进制计数器状态图Fig.1 State diagram of decimal counter using asynchronous reset method

仿真方案设计的要求是以时序波形图方式直观显示计数过程、过渡状态形成~CLR=0信号的过程,从而便于直观理解过渡状态的作用及计数原理。

其中,持续时间极短的过渡状态及~CLR=0信号的形成过程的波形显示是用Multisim软件仿真的技术关键,在实际硬件实验中是难以实现的,用Multisim软件仿真亦需要对仿真方案进行正确的设计。

2.2 Multisim仿真实验方法

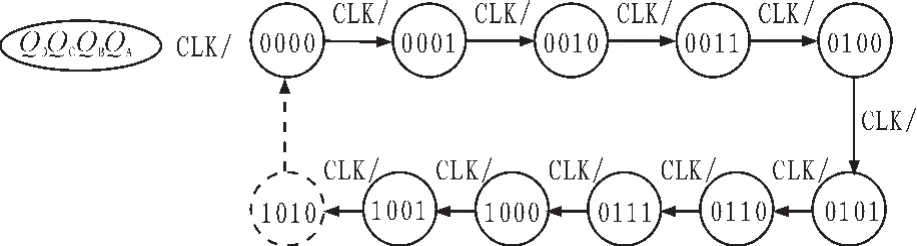

构建的仿真实验电路如图2所示。

1)时钟信号选择

选择Multisim中的字组产生器产生计数器的时钟脉冲信号。

字组产生器输出10进制计数所需的10个时钟脉冲信号,需在字组产生器的数据栏内以16进制(Hex)依次输入 0、1、0、1、0、1、0、1、0、1、0、1、0、1、0、1、0、1、0、1、0 共 21 个 字 组数据,并对最后一个字数据进行末地址设置 (Set Final Position),完成所有字组信号的设置[3-4]。并设置频率为fCLK=1 kHz(周期 TCLK=1 ms)。

仿真实验时,字信号发生器的输出方式为全部(BURST)时刚好显示一个计数周期的波形、字信号发生器的输出方式为单步(STEP)时可逐个脉冲输出便于观察每个时钟作用后计数器的状态变化情况。

2)74LS161集成4位二进制计数器触发方式修正

Multisim10版本中,集成4位二进制计数器74LS161的时钟脉冲触发方式有错误,为CLK为下降沿触发,附加反相器74LS04(图2中U3A)修正为和实际器件一致的上升沿触发方式。

3)显示仪器选择

图2 异步置零法十进制计数器仿真电路Fig.2 Simulation circuit of decimal counter using asynchronous reset method

实验表明,Multisim中的逻辑分析仪可以同步显示多路数字信号的波形,但对持续时间较短的~CLR信号及过渡状态却显示不出来。因此图2中选用Multisim中的2个四踪示波器同步显示时钟脉冲信号CLK、异步置零信号~CLR及状态输出信号QAQBQCQD,其中四踪示波器XSC1同步显示CLK及~CLR信号,四踪示波器XSC2同步显示QAQBQCQD信号,两个示波器的面板以部分重叠方式显示,如图3所示,且两个面板的Timebase区中的Scale、X position要设置一致,显示一个计数循环周期的波形。

4)过渡态及~CLR异步置零信号的延时

图2中U2A与非门74LS00用于在过渡态形成~CLR=0的异步置零信号,为能明显观察过渡态、~CLR信号的形成过程,需对与非门74LS00的上升延迟时间及下降延迟时间进行增大设置,通过Edit Model设置成rise delay=0.05 ms,fall delay=0.05 ms,使74LS00的平均延迟时间tpd=0.05 ms,亦可大于或小于0.05 ms,以能明显显示过渡状态及异步置零信号为原则,但不能大于时钟信号的周期。

3 仿真结果分析

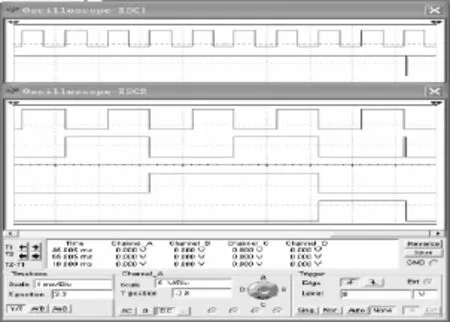

仿真显示的时序波形图如图3所示。

图3 仿真时序图波形Fig.3 Timing diagram of simulation

图3中,由上至下依次为时钟脉冲信号CLK、异步置0信号~CLR、状态输出信号QA~QD的波形。

从左至右观察图3可看出:第1个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=0001,~CLR=1;第2个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=0010,~CLR=1;第3个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=0011,~CLR=1;第4个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=0100,~CLR=1;第5个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=0101,~CLR=1;第6个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=0110,~CLR=1;第7个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=0111,~CLR=1;第8个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=1000,~CLR=1;第9个时钟脉冲信号CLK上升沿到来后计数器的状态为QDQCQBQA=1001,~CLR=1;第10个时钟脉冲信号CLK上升沿到来后计数器进入QDQCQBQA=1010的过渡状态,使~CLR=0,持续暂短时间后计数器异步置零,使QDQCQBQA=0000。

经过10个时钟脉冲信号作用后完成一个计数周期的循环,仿真实验结果和图1所示状态图的要求一致。

4 结束语

由于受实验仪器的限制无法对计数器工作波形进行硬件实验验证,主要是,现有的信号发生器不能产生多路同步信号,现有的示波器多为双踪示波器无法同时观测多路波形,用Multisim软件仿真解决了这一问题。

本文的仿真电路,用2个四踪示波器以时序波形图形式显示计数器输出状态,可直观显示计数过程、过渡状态形成~CLR=0信号的过程及状态变化与时钟脉冲信号边沿的对应关系。

所述方法具有实际应用意义。

[1]任骏原,腾香,马敬敏.数字电子技术实验[M].沈阳:东北大学出版社,2010.

[2]阎石.数字电子技术基础[M].北京:高等教育出版社,2006.

[3]任骏原.用Multisim仿真软件分析触发器的状态变化过程[J].实验科学与技术,2011,9(1):53-56.

REN Jun-yuan.The state transition analyzing of flip-flop by multisim[J].Experiment Science&Technology,2011,9(1):53-56.

[4]任骏原.Multisim在触发器工作波形分析中的应用[J].现代电子技术,2010,33(15):184-186.

REN Jun-yuan.An application of multisim to the working wave analyzing of flip-flop[J].Modern Electronics Technique,2010,33(15):184-186.

[5]任骏原.电子技术课程CAI教学模式的探索与实践[J].电气电子教学学报,2009,31(4):99-100.

REN Jun-yuan.The exploring and practice of CAI teaching mode of electronics technology course[J].Journal of Electrical&Electronic Education,2009,31(4):99-100.

[6]任骏原.基于次态卡诺图的J、K激励函数最小化方法及时序逻辑电路自启动设计 [J].浙江大学学报:理学版,2010,37(4):425-427.

REN Jun-yuan.Minimization method of J and K excitation function based on next-state karnaugh maps and self-starting design of sequential logic circuits[J].Journal of Zhejiang University:Science Edition, 2010,37(4):425-427.

[7]张晶,李心广.基于Multisim的电路设计与仿真[J].计算机仿真,2005,22(5):l09-152.

ZHANG Jing, LI Xin-guang.Multisim based schematic design and simulation[J].Computer Simulation,2005,22(5):l09-152.

[8]任骏原.数字电子技术实验教学模式的改革与实践 [J].渤海大学学报:自然科学版,2010,31(2):l65-167.

REN Jun-yuan.The reformation and practice of digital electronics practice teaching mode[J].Journal of Bohai University:Natural Science Edition, 2010,31(2):l65-167.