LT3599的LCD LED背光驱动控制电路的设计

2011-09-19于玖爱刘学满

于玖爱,刘学满

(长沙湘计海盾科技有限公司 湖南 长沙 410005)

相对传统的CCFL液晶显示器背光源存在色阶差、色纯度低、需高压驱动导致功耗大、屏厚度大等缺点而言,LED背光源以其功耗低、寿命长、更环保、屏厚度低等优点[1]在民用和军用显示产品上得到更多应用。尤其是它超强的色彩表现力更是CCFL背光源远不及的,其色彩饱和度达到甚至超过Adobe RGB和NTSC色彩标准要求[2],可以达到NTSC ratio 100%以上平面光源特性,而CCFL背光只能实现NTSC色彩区域的78%。另外,LED的高刷新频率使其在视频方面有更好的性能表现,LED显示屏的单个元素反应速度是CCFL背光液晶屏的1 000倍,即使是在强光下也可以照看不误,并且适应零下40℃的低温。

随着LED背光源越来越广泛地应用,其驱动电路的良好设计也就显得格外重要。对于普通的小型液晶显示器而言,通常只要几个LED灯便可满足其显示要求,因此对驱动电路的要求也较低。对于中大型液晶显示器而言,常需要几十、上百个的LED灯,对电路驱动能力的设计要求就更高。笔者介绍的基于LT3599 LED背光源驱动控制电路,可以适用于中大型液晶显示器 (同样也可适用于小型液晶屏背光源的驱动)。此电路经测试和试验验证,能满足各种常规中大型液晶显示器的背光驱动控制电路的要求。

1 LT3599简介

LT3599是一款真彩色PWM脉宽调控的DC/DC转换器,它的占空比高达3 000:1,带有4路LED驱动,每路可驱动120 mA电流,且每路的电流大小均可编程控制和独立开关。它能适应3.1 V~30 VDC的宽输入电压范围,输出电压高达44 VDC,开关频率范围为200 kHz~2.1 MHz,同步时钟的选择灵活——即可接外部时钟也可用自带同步时钟。

LT3599带过压、欠压、过流、过热、抗较大浪涌电流、输出短路或开环保护等完善的保护功能,是一款安全可靠的集成控制芯片。

2 电路的总体设计

整个驱动控制电路的整体构成框图如图1所示,由多路电源输出模块、LT3599控制模块、FPGA可编程PWM脉宽控制模块、LED灯组模块组成。LT3599内部是升压电路,将输入的电压在FPGA模块的控制下转换成LED灯组所需的稳定电流和电压,从而实现亮度、对比度调节,提供给液晶屏稳定均匀的背光源。

图1 驱动控制电路系统框图Fig.1 Block diagram of drive control circuit

2.1 多路电源输出模块的设计

设计时选用了日本COSEL公司的CBS502424、CBS502403集成电源块,设计成可调稳压电路。外部电源只有一路(+28 VDC)输入,经内部的整流、滤波、电压转换和稳压处理后,转换输出给FPGA模块以及LT3599控制模块所需要的+5 VDC、+3.3 V和+24 VDC等多路电压。

2.2 LT3599控制模块的设计

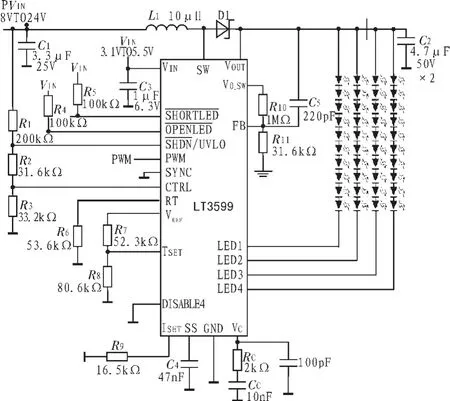

LT3599有2种封装:28个管脚的封装和32个管脚的封装,其中32个管脚的封装是热控增强型封装,对于高亮及中大型液晶屏来说,选择32个管脚的热控增强型封装设计电路更稳定可靠。其典型控制电路如图2所示。

图2 LT3599典型应用电路Fig.2 Typical application circuit of LT3599

2.2.1 输出LED驱动电流大小的设计

LT3599有4路LED电流输出通道,每路输出的电流大小在30~120 mA之间,具体通过设置ISET管脚所接电阻RISET值大小来控制,此RISET电阻值范围在11~44.2 kΩ之间,RISET值与LED驱动电流大小的具体计算方法为:

LT3599通过PWM脉宽调控来改变其输出给的LED电流值大小,从而改变LED的亮度,实现对液晶显示器亮度和对比度的调节。PWM脉宽与LED电流的关系曲线图如图3所示。

图3 PWM脉宽时序与LED电流关系图Fig.3 Relation diagram between PWM timing sequence and LED electricity

2.2.2 开关频率的设计

LT3599有很宽的工作开关频率,在200 kHz~2.1 MHz之间,具体由管脚RT所接电阻值的大小来决定,RT值与开关频率大小的关系图如图4所示。

图4 开关频率与管脚RT所接电阻值关系曲线图Fig.4 Relational graph of switching frequency and resistance value connected with RT

要想设计出最适合的电路开关频率,需综合考虑几个方面:

1)开关频率越高则电感值越小,高频开关损耗也就越小;

2)对于低压驱动多个LED灯的情况,需尽量设置低的开关频率;

3)设计时需考虑总电压功率的损耗。

4)LT3599内部的同步时钟频率在 240 kHz~1.5 MHz之间,对于启用了LT3599内部SYNC同步时钟频率的电路,电路的开关频率设计时需低于LT3599内部同步频率的20%,否则会导致电路工作不稳定。

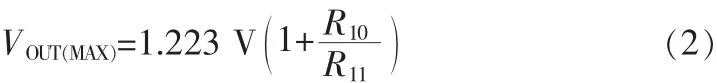

2.2.3 输出LED所需电压的设计

LT3599输出电压的大小通过设置电阻R10、R11的值来确定,计算公式为:

为了确保电路长期使用的可靠性和输出效率,设计时输出电压值一般要高于LED所需电压的10%。为了减少输出纹波,在LT3599电压输出端需还接一个4.7~10 μF的电容。另外需注意,Vout管脚处所接肖特基稳压管允许通过的平均电流需大于LED驱动电流,此肖特基稳压管的最大反向电压还需大于LT3599输出电压Vout。

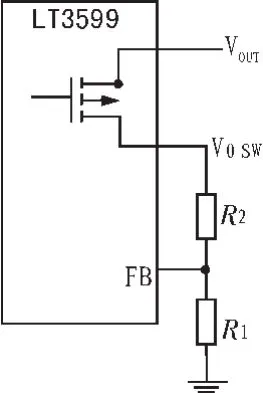

2.2.4 保护电路的设计

1)过压保护的设计:通过FB管脚设计电压反馈环路从而实现过压保护功能。FB脚参考电压为1.233 V,具体的保护电路设计如图5所示。

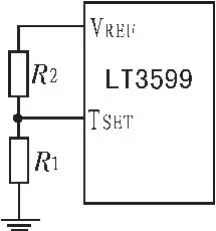

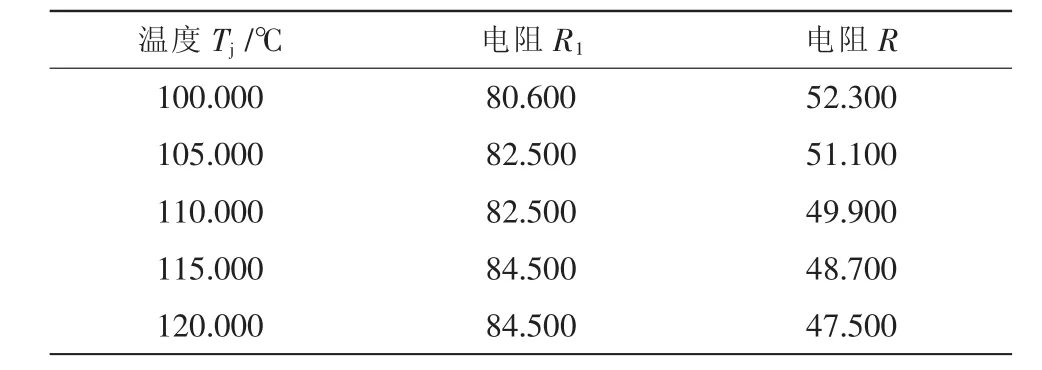

2)热保护电路的设计:用VREF、TSET管脚设计热保护电路。预先设定一个LT3599内部极限保护温度,当LT3599芯片温度超过这个值时LT3599输出给LED灯的电流就自动降低,从而使芯片的温度慢慢降低。LT3599内部设定给VREF的参考电压时1.227 V,VREF最大输出100 μA电流。具体的电路设计如图6所示,LT3599内部最大控制节点的温度值与电阻R1、R2的选择对应关系如表1所示。

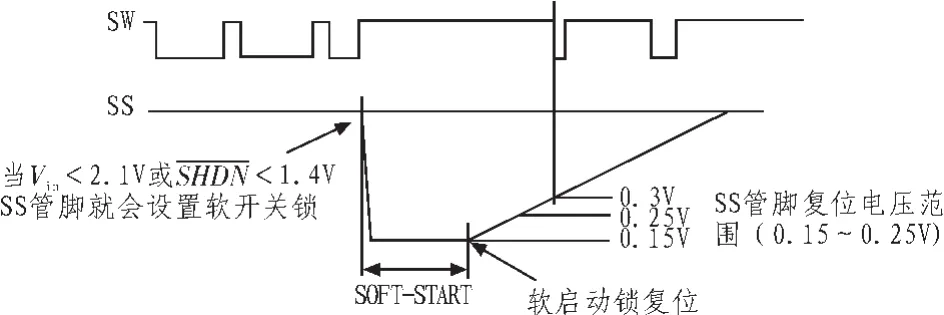

3)欠压保护电路的设计:通过SHDN/UVL0管脚设计欠压保护电路。为了避免电路在超低电压下工作导致出现不稳定状况,当此管脚电压低于1.4 V时LT3599会自锁。LT3599的关断电压和接通电压可分别通过式(3)和式(4)计算而得:

图5 用FB管脚设计过压保护电路Fig.5 Overvoltage protection circuit designed with FB basepin

图6 用TSET管脚设计温度保护电路Fig.6 Temperature protection circuit designed with TSETbasepin

表1 LT3599芯片内部最大节点控制温度与电阻R1、R2的对应关系Tab.1 Corresponding relationship between controlling temperature of maximal node inside chip LT3599 and resistance R1、R2

图7 欠压自锁控制电路Fig.7 Undervoltage self-locking control circuit

通过SS管脚设置软启动开关锁的控制时序图如图8所示。

图8 软开关控制启动时序图Fig.8 Sequence diagram of soft on-off control start-up

2.3 FPGA可编程控制模块的设计

FPGA采用的是高速串行接口通讯,和传统的并行接口相比,串行通讯能提供更大的带宽、更远的距离、更低的成本和更高的扩展能力[3]。

在设计FPGA[4]对LT3599的控制功能时,充分利用其内部可进行灵活设计的特性。首先检测视屏驱动板输出给显示屏的视频信号[5],识别出非标准信号,必要时FPGA内部产生标准视屏信号,然后对行场同步信号进行数字滤波、时钟锁相,解决因长距离传输导致信号出现衰减失真以及电磁干扰等现象,再将RGB信号按照预定的曲线进行Gamma和对比度调节。

在进行视屏信号检测时,用板卡上的系统时钟对输入HS、VS等信号的上升沿或下降沿进行计数,如果在设定时间内检测到边沿次数大于某一个限值则表示有信号输入,否则为无信号输入。这种方法输入信号的格式范围宽、可实现性强。

在进行Gamma、对比度调节时,FPGA采用的是通过PC机查表方式,即对每一个输入给出一个确切的输出值,此值预先根据一定的算法计算好、使用C语言程序编程设定,然后将相关数据加到FPGA工程代码中。通过预先设定好的通信方式,在需要进行调整时,将要调整到的信息发送给FPGA,FPGA根据设定好的等级选择输出不同的值,以完成相应的调整功能。

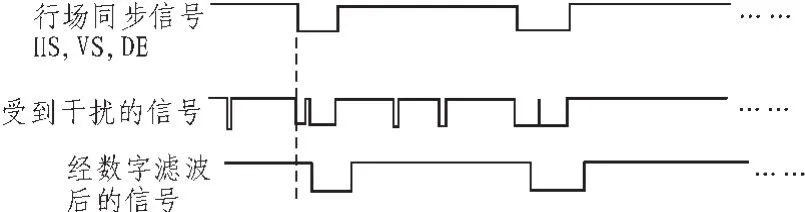

数字滤波采用的是对FPGA内部的电平调节的方式,因为HS、VS等信号上出现的不正常电磁干扰信号一般脉宽很窄,而HS、VS、DE的脉宽较宽,因此,只要能够消除非正常脉冲,就可以保证画面稳定正常显示。关于数字滤波解决EMC电磁干扰的时序图如图9所示。

图9 数字滤波时序图Fig.9 Sequence diagram of digital filtering

2.4 LED灯组

由于LED的亮度是由通过其内部的电流决定的,因此进行LED灯布局时,一方面要考虑到整个液晶屏的亮度均匀性,另一方面要减小电路微小电压波动给LED灯亮度带来的影响。对于普通中小尺寸的液晶屏,由于背光源大都用的是侧光式,LED灯组可采用串联和并联相结合的方式。对于大尺寸液晶屏来说背光源一般采用直下式[6],为了提高亮度均匀性、减轻显示器重量,LED灯组还可采用正三角阵列布局[7],能更好地实现对LED灯的保护且提高亮度的均匀性。

3 结束语

本文所介绍的LED背光驱动电路,其电路效率可达90%以上。该电路设计上各相关参数都可以精确计算和控制,电路的保护措施齐全、控制效果好、抗干扰能力强,并且可以根据所需背光亮度和屏的大小灵活组合使用。经试验以及使用测试验证,是一款较理想的驱动控制电路。

[1]周志敏,纪爱华.LED背光照明技术与应用电路[M].北京:中国电力出版社,2010.

[2]彭波.多媒体技术教程[M].北京:机械工业出版社,2010.

[3]李大鹏,陈长胜,王世奎,等.基于FPGA的高速串行传输接口研究与实现[J].航空计算技术,2008,38(2):100-103.

LI Da-peng, CHEN Chang-sheng, WANG Shi-kui,et al.Research and implementation of high speed serial transmission interface based on FPGA [J].Aeronautical Computing Technique,2008, 38 (2):100-103.

[4]黄智伟,王彦,陈琼,等.FPGA系统设计与实践[M].北京:电子工业出版社,2005.

[5]Jack K.Video Demystified[M], Elsevier:Newnes,2005.

[6]马丽,张丽蕾,万丽芳,一种直下式LED背光源的设计[J].现代显示,2009(9):50-54.

MA Li,ZHANG Li-lei, WAN Li-fang.The design of a direct-type LED backlight[J].Advanced Display, 2009(9):50-54.

[7]王帅,李荣玉,陈秀锦,等.新型直下式正三角阵列LED背光源的光学分析与设计[J].液晶与显示,2009,24(6):845-849.

WANG Shuai, LI Rong-yu, CHEN Xiu-jin,et al.Design of noveltriangularLED array unitfordirecttype LED backlight[J].Liquid Crystsls and Displays, 2009,24 (6):845-849.