直扩-变换域滤波接收机设计与实现

2011-09-13张爱民王星全张德兴

张爱民, 王星全, 张德兴

(总参谋部通信训练基地,河北 宣化 075100)

0 引言

直接序列扩频通信系统具有较强的抗干扰能力和防截获能力,从理论上讲,通过提高扩频通信系统的处理增益可以得到任意等级的抗干扰能力,但处理增益不断增加会造成接收机复杂度的提高,甚至是不可实现的,当干扰信号的功率超过一定限度后,直扩系统的性能会降低,甚至造成通信中断。为了在不增加扩频增益的条件下进一步抑制窄带干扰,需要在解扩前采用信号处理技术来抑制干扰,弥补扩频增益的不足。变换域处理方法利用宽带扩频信号和信道白噪声与窄带干扰在频域上的不同特征来判断干扰的位置和强度,采用适当的陷波算法对干扰谱线进行抑制,从而有效的提高信噪比。所以在战场通信环境下直扩和变换域滤波联合进行干扰抑制是提高无线通信设备生存能力的理想方案之一。

1 接收机的射频前端电路设计

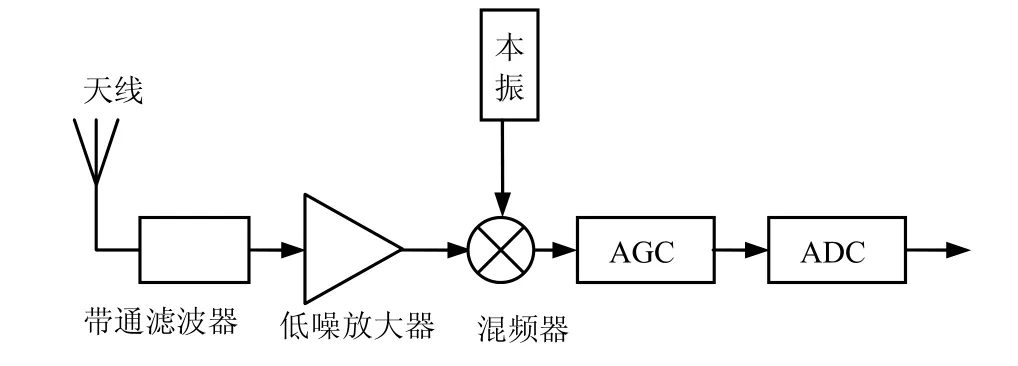

该接收机射频前端电路吸取了软件无线电接收机的设计思想,软件无线电提出对射频模拟信号数字化尽可能地靠近天线,通过对大规模集成器件或专用数字信号处理器的软件化编程来完成各种功能,如上下变频、调制解调、加密模式、数据帧格式、通信协议等。然而由于ADC/DAC性能和数字信号处理器速度的限制[1],现在一般可行的方案是中频带通采样。在中频进行数字化较射频模拟信号直接进行数字化,接收机射频前端电路结构会相对复杂,但A/D设计的大大简化,数字信号处理器件负担的大大减轻。基于中频带通采样的接收机系统框图如图1所示。

由接收机系统框图可知,射频信号经天线接收下来以后,先通过射频带通滤波器,之后由低噪声放大器对信号进行放大。接着进行混频,然后经过中频滤波器送入放大器进行滤波、放大,此时如果中频滤波不充分,寄生响应和本振泄漏会屏蔽用户信号,从而严重影响接收机正常通信。最后由自动增益控制(AGC)输出至 ADC。中频滤波器后的变增益放大器主要用来抑制噪声,降低信号的动态范围,同时将信号放大到A/D转换器所需要的幅度。中频放大器的增益变化对系统增益影响较大,所以需要根据不同信号强度进行调节,这也就是自动增益控制加入接收机的原因。虽然此接收机结构具有相当优异的性能,但在其模块的接收机实际制作上,仍存在镜像信号[2]。镜像信号干扰的产生,主要是由于在接收机中,所使用的下变频混频器会产生对称于本振输出频率的两侧、距离一个中频频带处的信号,以相同的转换响应下变频至中频频带,因此对于有用的信号在中频频段造成干扰。下变频后的信号需要进一步滤波与放大处理以提升信噪比并抑制干扰信号。

图1 基于中频带通采样的接收机系统

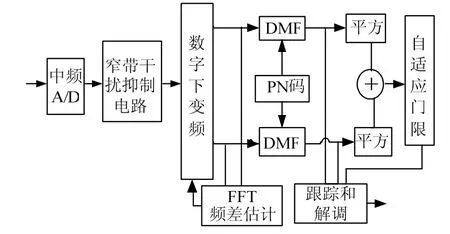

2 接收机的中频和基带电路设计与实现

混频后产生的中频信号首先进行A/D采样、其次进行强窄带干扰抑制,考虑到强窄带干扰电路对后端载波同步环路的影响,窄带干扰抑制模块在数字下变频之前完成。然后进行数字下变频,产生出两路正交的基带信号,接着采用DMF(数字匹配滤波器)进行的PN码快速捕获与跟踪,在进行PN码同步的同时进行载波同步,较大的载波频率偏差会对PN码同步产生严重的影响,必须进行载波频率偏差估计。为了提高PN码的捕获性能采用自适应门限设置技术、最后进行解调。上述模块除中频 A/D 采样和数字下变频采用专用器件完成外,其他功能模块均在FPGA 上通过VHDL程序设计来实现。主要包括窄带干扰抑制模块、频差估计和校正模块、基于DMF的PN码快速捕获模块等。该接收机的中频和基带电路设计框图如图2所示。

2.1 中频采样和数字下变频模块

中频采样设计就是根据系统带宽和灵敏度的要求来确定ADC的性能。选择AD公司生产的模数转换器件AD6645。AD6645 采用三级子区式转换结构,这样设计的好处既满足了转换的精度和速度,又获得了较小的功耗和封装尺寸。内含采样保持电路和基准源,功耗为1.5 W,量化位数为14。数字输出可工作在+3.3 V,方便与数字ASIC接口连接,中频采样频率的典型值为70 MHz,采样速率可达80 Ms/s。其输出信噪比SNR为74.5 dB、无杂散动态范围100 dB,,工作带宽270 MHz,对200 MHz的信号采用时采样抖动0.1 ps。

图2 接收机中频和基带电路设计

数字下变频器件主要完成三个功能,一是数字正交混频,二是数据速率转换,最后是滤波整形输出。选择的是Analog Device公司的多通道数字下变频器件AD6635。它具有如下特性: 17 位线性比特补码输入;四通道实数输入模式的最大输入数据速率达80MSPS,具有四个实数输入端口,两个复数输入端口,四个16位并行输出端口,四个在96 dB内可编程的数字AGC环,四个插值半带滤波器等。

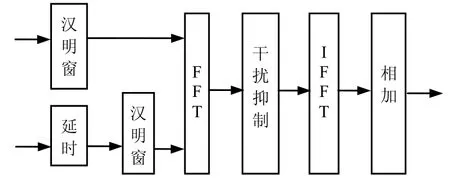

2.2 窄带干扰抑制模块

窄带干扰抑制方法实现的关键模块是中频数字信号加窗、FFT /IFFT运算及窄带干扰谱线检测与处理,下面分别讨论这三个模块的实现。硬件平台使用的FPGA的是Xilinx公司的 Virtex2 系列芯片—xc2v6000-4。基于模块复用的变换域窄带干扰抑制结构图如图3所示。

图3 基于模块复用的变换域窄带干扰抑制结构

2.2 .1中频数字信号加窗子模块

由于DFT假设了一个长度为有限序列的周期延拓,隐含了对长度为 N 的截断序列进行周期拓展, 如果截断后序列在边界不连续, 则会导致信号经过DFT变换之后出现频谱泄漏, 从而使得窄带干扰信号的能量对临近的频谱产生严重的“污染”, 为了减轻DFT变换的能量泄漏, 常用的方法是在对信号进行DFT之前进行加窗, 窗函数的引入使得截断序列的边界变得平滑, 因此可以减轻DFT的能量泄漏问题。但是窗函数的引入也使得信号波形产生失真,从而使得信号信噪比下降, 为了减轻加窗对信号波形产生的失真, 可以通过在相邻的变换截断序列之间存在 50% 重叠的方法来减弱加窗对信号波形的失真的影响[3]。如图3所示。

2.2 .2基于FFT /IFFT运算的信号变换子模块

由于进行FFT和IFFT会消耗大量的FPGA资源,加窗后的两路数据可采用分时复用的方式处理。实现快速傅里叶变换模块时可以使用开发工具ISE8.2带有的专用IP核[4],IP核生成器是FPGA设计中的一个重要设计输入工具,其实现结果在面积和速度上都令人满意。因此可以利用IP核生成器来方便的设计,提高工作效率。ISE8.2带有的FFT/IFFT专用IP核可以完成实数、复数信号的FFT和IFFT。

Fast Fourier Transform核为通用的FFT/IFFT核,输入数据可为8、12、16、20和24位五种不同的格式,输出可选scaled模式或unscaled模式,即可选择输出数据位数与输入数据相同或保留所有有效位。Fast Fourier Transform核可支持N( N = 2m,m = 4 ~14)点的FFT/IFFT运算,且可实时方便地配置成FFT或IFFT变换模式。它内部已经自动集成了RAM,不需要外接 RAM,且提供了丰富的对外接口。Fast Fourier Transform核支持三种工作模式,以方便用户在权衡转换速度及资源消耗时做出切合实际的选择。这三种工作模式分别是 Pipelined Streaming I/O,Radix-4,Burst I/O,Radix-2,Minimum Resources。

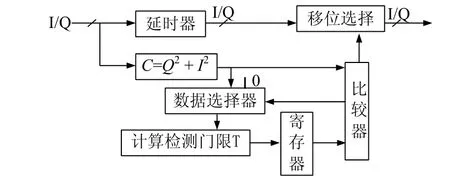

2.2.3 干扰谱线抑制子模块

窄带干扰抑制算法较多,文献[5]提出的自适应滤波的干扰的抑制算法,这里采用文献[6]提出的干扰的抑制算法,该算法根据信号在频域上的统计特性利用最大似然估计方法估计出干扰检测门限,对幅度的平方大于干扰检测门限的谱线被认为是干扰谱线,根据窄带干扰谱线的幅度值来决定谱线衰减的程度,幅度衰减通过二进制移位就可以完成,所以占用的资源比较少,适用于FPGA实现。

由快速傅里叶变换(FFT)后的 I/Q两路数据首先进行求模运算,也即求出 Ci= Qi2+ Ii2,同时还计算出检测门限T。为了保证对干扰检测门限估计的样本值的有效性,在谱线幅度值与干扰检测门限比较之后再决定样本值是否有效。如果样本值大于干扰门限,那么数据选择器将输出 0。该控制信号有比较器来输出,同时比较器不断将输出谱线的幅度与干扰检测门限作比较,输出信号的衰减因子,衰减的幅度由移位来完成的。窄带干扰抑制模块 FPGA实现原理图如图 4所示。

2.3 频差估计和消除模块

当载波频差较大时,扩频码同步和载波同步互为前提,扩频码的同步必须以载波的粗略同步为前提,而载波的精确同步又要以扩频码的同步为前提。无线通信系统经常在高动态环境下工作,使得接收信号的载波存在着较大多普勒频移,对PN码的同步造成很大的困难,甚至根本无法同步,这时必须预先估计载波频偏并进行校正,实现载波频率的捕获与跟踪。

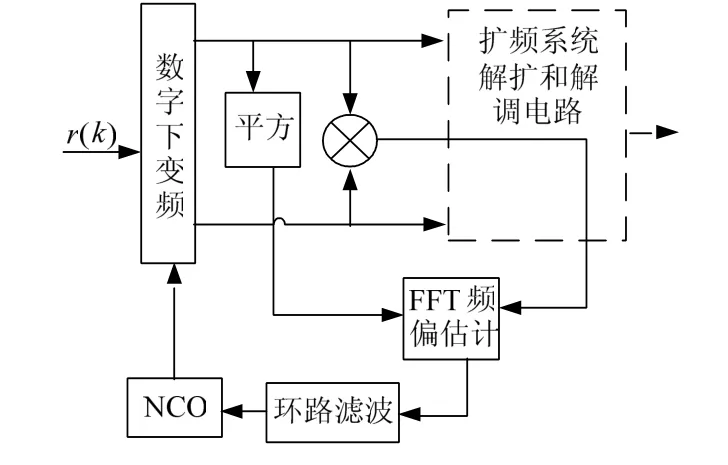

笔者在文献[7]中提出了一种基于复矢量 FFT估计载波频差的方法,这种方法简单易行,且频率估计误差小,能有效的解决高动态载波大频差下伪码捕获的问题。载波频差估计和对消原理框图如图5所示。基本原理是:多卜勒频移是运动中的通信系统的接收机相对于发射机的径向运动速度所致, 而这种速度变化通常很慢, 在相当一段观测时间内,这种载波频偏可以近似为一单频信号,在频谱上呈现出尖峰,很容易被检测出来,经过FFT的频偏估计以后,fΔ并不能完全被消除而是被限制在一个比较小的范围,将频偏估计值经过AFC环路进行滤波后去控制本地NCO的频率,使其跟踪输入中频信号的变化,从而使得数字下变频的输出始终为零中频的数字基带信号。

图4 窄带干扰抑制模块FPGA实现原理

图5 载波频差估计和对消原理

2.4 直扩系统PN码捕获模块

PN码捕获模块采用基于FPGA的非相干DMF伪码捕获技术[8],基本原理如图2所示,主要包括三个子模块,数字匹配滤波器子模块、平方和子模块、自适应门限判决子模块。平方和子模块用ISE8.2带有的专用乘法器IP核和一个加法器就可以实现,电路设计比较简单。对于数字匹配滤波器子模块的设计,在硬件资源充足的情况下,可以考虑采样直接型FIR或倒置型FIR滤波器结构来实现,在ISE8.2中带有的高性能的FIR滤波器的IP核,可以方便的设计多种类型的数字匹配滤波器。对于较长PN码的捕获,由于硬件资源的消耗太大,就要考虑用折叠匹配滤波器结构,折叠匹配滤波器可以由VHDL程序设计来完成,自适应门限判决子模块依据自适应门限算法,在FPGA通过VHDL程序设计实现,具体方法在这里不再赘述。该子模块是用硬件描述语言来对电路的结构和功能进行设计和实现,与传统的专用集成电路相比,具有能处理信号的形式灵活,成本低,体积小,系统的整体性能高等优点。

3 结语

直扩-变换域滤波联合抗干扰接收机克服了单纯依靠处理增益抗干扰的不足,降低了接收机的复杂度,且大大提高了无线通信系统的抗干扰能力,尤其适用于存在强窄带干扰的复杂电磁环境,随着高密度、高速度 FPGA器件的出现及相应EDA软件的成熟,在FPGA上进行数字信号处理的方法显示出巨大的优势。所以直扩和变换域滤波联合进行干扰抑制的接收机在未来战场通信环境下具有广阔的应用前景。

[1] HAMADA N. Digital Signal Processing: Progress over the Last Decade and the Challenges Ahead[J]. IEICE Trans. Fundamentals,2001,E84-A(01):80-90.

[2] 高峻. 无线通信射频接收前端研究与设计[D].成都:西南交通大学,2006.

[3] 张春海,卢树军,张尔扬.基于加窗DFT的DSSS系统变换域窄带干扰抑制技术[J]. 解放军理工大学学报,2004,4(15):11-15.

[4] 田耘,徐文波,张延伟.无线通信FPGA设计[M]. 北京:电子工业出版社,2008.

[5] 张毅,王辉.一种直扩通信窄带干扰抑制的自适应滤波技术[J].通信技术,2008,41(04):13-15.

[6] 张爱民,胡艳龙,韩方景.低信噪比下基于自适应门限的窄带干扰抑制研究[J]. 电子信息对抗技术,2009,24(01):51-54.

[7] 张爱民.高动态下基于DMF的伪码捕获频差估计研究[J]. 空间电子技术,2009,6(04).12-15.

[8] 桂岳,蔡德林,范晓东,等.非相干匹配滤波算法的 FPGA 实现及分析[J].通信技术,2008,41(12):296-298.