基于FPGA的视频采集与显示系统设计

2011-08-09李江辉王景存

李江辉,王景存

(武汉科技大学 信息科学与工程学院,湖北 武汉 430081)

责任编辑:任健男

0 引言

如今视频监控领域迅速发展,各种格式的视频信号需要在不同的媒体上播放,而各种播放媒体普遍较贵,并且各种播放媒体采集和传输的视频、音频信号的格式不尽相同,在众多的显示媒体之间还没有一个统一的标准接口来实现音、视频信号的显示和播放。笔者设计了一种PAL转VGA接口的视频信号传输与显示控制器,简单地实现了一种显示格式到另一种显示格式的转换。

1 系统方案设计

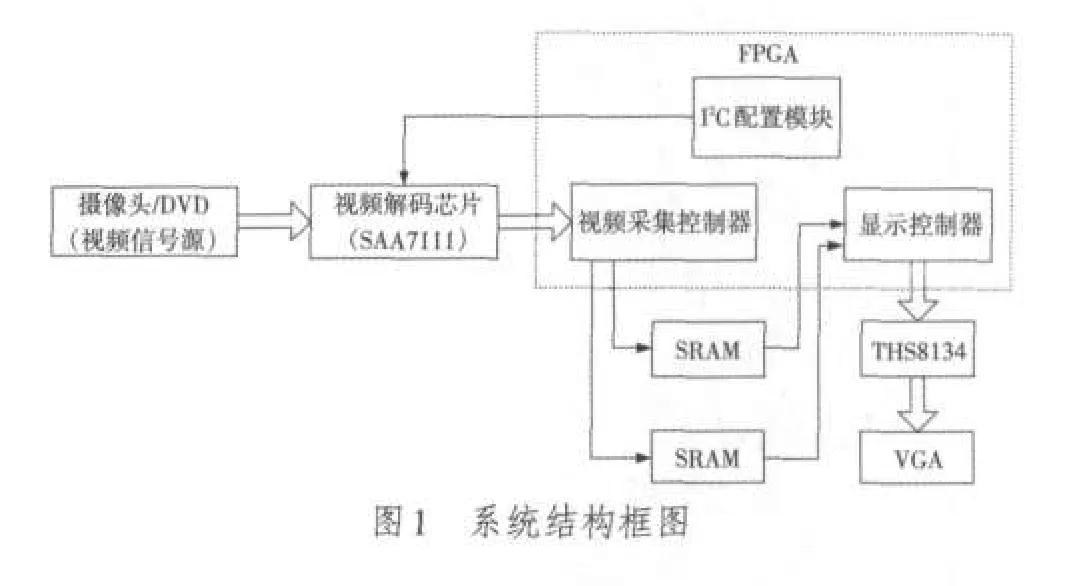

本系统是基于FPGA的视频显示系统,不仅具有摄像头或DVD视频信号采集功能,还具有视频格式转化和实时显示功能。首先在FPGA内部设计I2C配置模块来配置片外SAA7111[1],摄像头/DVD输出的模拟视频信号经过SAA7111后得到RGB格式的数字信号,视频采集控制器采集到该数字信号后,送入片外的2片SRAM进行乒乓操作来完成帧频,显示格式的转换,显示控制器读取SRAM中的数据送入THS8134进行D/A变化,从而形成完整的数据流。D/A变化后的数据送入CRT显示器实时显示。系统结构框图如图1所示。

2 视频信号采集与存储

2.1 I2C配置模块

由于视频解码芯片SAA7111需要合理配置后才能完成视频数据的采集和相应格式的数据输出。对其配置即是对其片内寄存器进行设置,它具备I2C总线接口,有32个控制寄存器,其中20个可编程。窗口大小、A/D转化速度、帧/场模式等参数都可以在工作过程中对相应的寄存器进行设置,从而实现对SAA7111的实时控制。

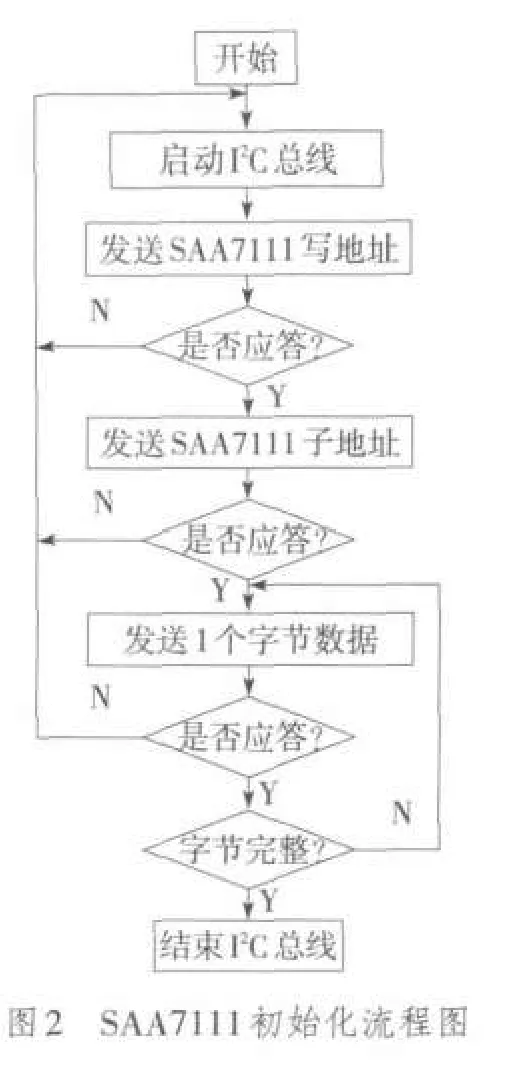

在对SAA7111进行配置时需要注意,写完一个字节后,一定要等应答后开始下一个字节。用I2C总线配置SAA7111时,系统时钟频率不能太快,如果太快会使SAA7111来不及响应。一般系统时钟频率采用400 kHz,配置可靠。I2C总线的时钟与数据要严格按时序的逻辑编写。在开始与停止时,时钟高电平间数据可以变化;在传送数据时,时钟高电平期间数据不能发生变化。SAA7111初始化流程图如图2所示。

2.2 视频采集模块

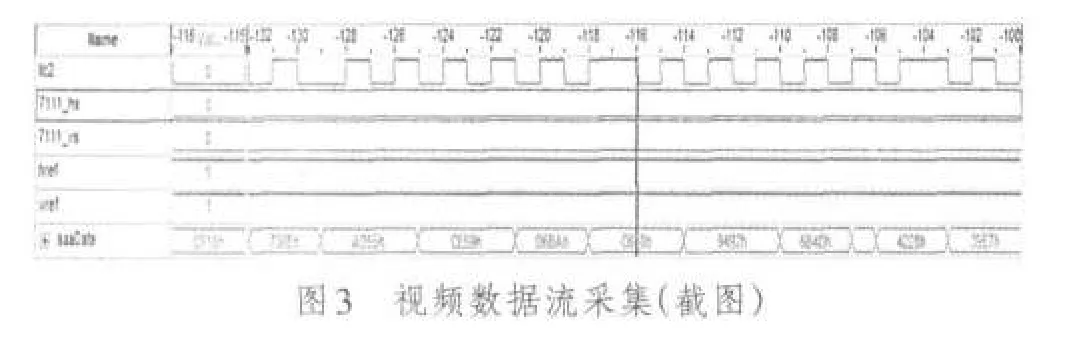

SAA7111通过I2C配置模块初始化完成后,FPGA便可以采集到SAA7111输出的像素时钟、行同步、场同步、16 bit RGB信号、行参考、场参考、奇偶场识别等信号。视频数据流采集如图3所示。

其中,llc2为SAA7111输出的像素时钟,且llc2为13.5 MHz,SAA7111在该像素时钟的节拍下输出像素点的RGB数据信号。7111_hs为输出视频流的行同步信号,7111_vs为场同步信号,href为行参考,vref为场参考信号,saaData即为16 bit RGB数据信号,R∶G∶B=5∶6∶5格式,并且该视频流的分辨力为720×572。

2.3 视频帧合成模块

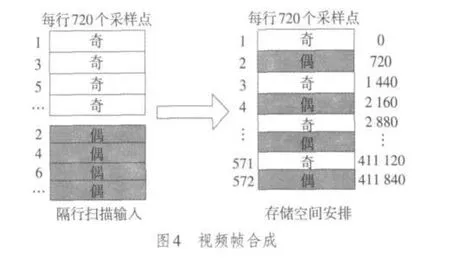

PAL制式视频信号具有隔行扫描的特性,因此采集的视频数据被分为奇数场和偶数场,而在实时显示的CRT显示器是需要完整的视频帧[2-5]。所以需要将奇偶场的视频数据进行合成。当一帧开始时,首先是第1,3,5行等奇数行的数据进行缓存,然后在第2,4,6行等偶数行的数据采集进来时,结合奇场数据,根据PAL视频数据格式合成帧数据,如此便能形成完整的视频帧用于处理。1帧数据由2个部分组成:偶场地址=基地址E+偏移地址E;奇场地址=基地址O+偏移地址O。视频帧合成如图4所示。

本设计中通过行列计数器按照完整视频的数据格式,产生地址计数,然后将这些地址计数送到SRAM的地址总线上,这样就可以在采集视频的时候,实时地将每一个采样数据送入到SRAM中进行存储,保证数据的完整性。实质上就是对每一个视频数据通过行列计数器分配了唯一的地址,然后通过这些地址从SRAM中对视频数据进行读写,而仅仅是在FPGA内部对数据进行了地址编码,这样就大大节省了FPGA内部资源,同时也提高了系统的实时性。

2.4 SRAM乒乓操作模块

乒乓操作处理流程可以描述为:输入数据流选择单元等时地将数据流分配到两个数据缓冲模块;而数据缓冲模块可以是任何的存储模块,双口RAM、单口RAM和FIFO均可以用来进行数据缓冲。把乒乓操作模块当作一个整体,从这个模块的两端看数据流,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此它非常适合本设计中视频流不间断的要求。

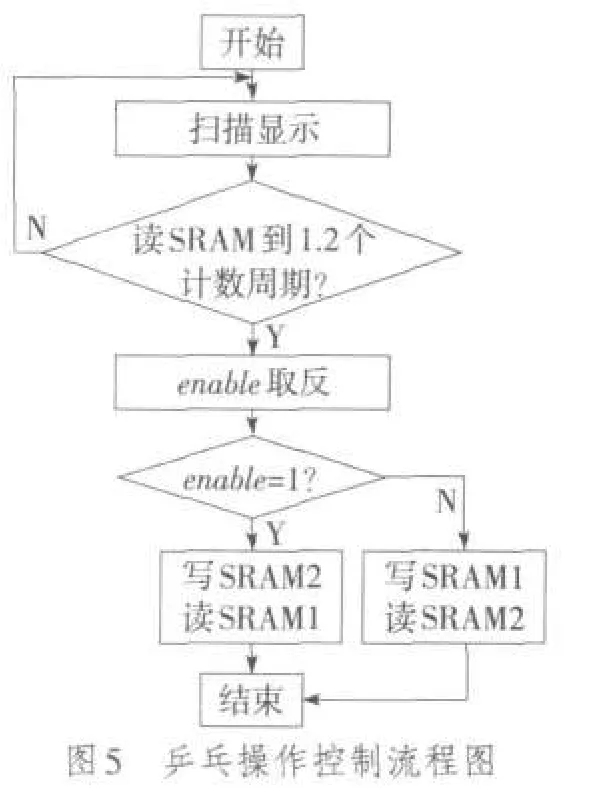

将上述由奇场、偶场合成的每一帧视频数据存入到SRAM的同时,为保证视频流不间断,就要完成帧与帧之间的交替。因为每一帧都对应一个SRAM的读写,所以帧与帧之间的交替变化为2个SRAM之间读写的切换。本设计中设置了1个状态变量enable,当enable为0时写SRAM1,同时读 SRAM2;当enable为1时 读 SRAM1,同 时 写SRAM2。当然 enable的初值为0,其他是根据帧频变化中是否完成了读SRAM所要求的1.2个计数周期,不断取反得到。图5为乒乓操作控制流程图。

3 D/A及显示控制模块

因为本设计中采用CRT显示器作为显示输出,要在该显示屏上连续显示一帧一帧的图像,需要按照标准的VGA接口规范来控制时序。而VGA接口上主要包括了行同步、场同步、RGB三基色信号。并且VGA接口上的行同步、场同步是数字信号,FPGA可以直接控制,而该接口上的RGB三基色信号是模拟信号,所以FPGA从片外SRAM读出的视频流需要经过帧频及分辨力变化,D/A转化后才能送到VGA接口上显示。

3.1 帧频及分辨力变化

该摄像头输出PAL制式图像,规定场频为50 Hz,图像的分辨力为720×572,而本设计用的VGA接口标准为800×600@60 Hz。不同的格式显示,需要进行帧频和分辨力的变化。帧频变化具体实现:当SRAM进行乒乓操作时,当向进行写操作的SRAM写入1帧原始信号时,从另一个SRAM读出数据,完成当前帧输出后再从进行写操作的SRAM首行起读出数据(多读0.2个计数周期),开始新一帧输出。即读SRAM行地址计数器从原值继续计至行最大值后再从0开始重新计数。共完成写SRAM 1个计数周期,读SRAM 1.2个计数周期后,再进行SRAM的读写切换。每经过5次这样的乒乓操作切换(1个循环),便能完成帧频变换。

而对于分辨力的变换,因为分辨力增加后,每场行数增加,每行像素点也增加,故每场需要产生新的行数据,每行需要产生新的像素值。而采用均匀插值的方式,即对原始信号中的某些行进行重复读取,对所有行的某些像素进行重复读取,可以很好地完成分辨力的变化。

3.2 VGA控制模块

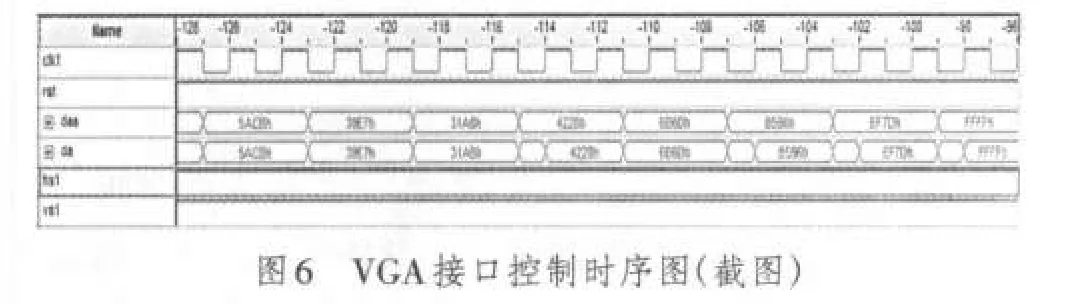

该模块从乒乓操作的SRAM中读出处理好的数据以后,需要按照VGA接口的时序送到THS8134。这里的时序需要产生行同步、场同步信号(即CRT显示器的消隐信号)。另外要在非消隐期将处理好的视频数据送出去。其中clk1为时钟,rst为复位信号,daa为从SRAM读入的数据,da为输出的数据,hs1和vs1为行场同步信号。图6为VGA接口控制时序图。

3.3 D/A变化

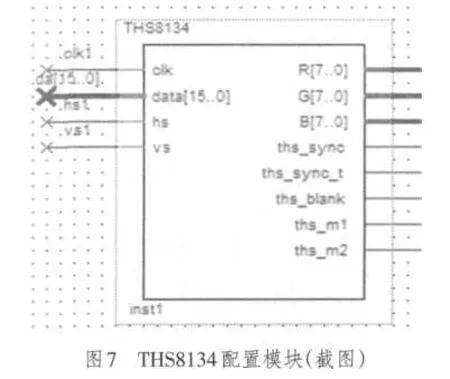

THS8134芯片为TI公司主要应用于图像方面的D/A芯片。THS8134的ths_m1和ths_m2用于配置输入图像的数据格式,该芯片可以配成输入4种不同的数据格式,分 别 为 RGB 3x8b-4∶4∶4;YPbPr 3x8b-4∶4∶4;YPbPr 2x8b-4∶2∶2和YPbPr 1x8b-4∶2∶2。本系统输入的图像数据格式为RGB 3x8b-4∶4∶4格式。而ths_blank用来控制输出消隐,ths_sync_t控制三电平同步的正同步头宽度,ths_sync控制D/A输出信号同步的宽度。THS8134配置模块如图7所示。

由于THS8134每次接收24 bit数据再进行D/A,在该模块中还需要将VGA模块输出的16 bit RGB转化为24 bit RGB。在本设计中采用低位补零的方法来实现的。即当输入格式R∶G∶B=5∶6∶5时,给R,G,B总线的低位分别补3 bit的0、2 bit的0、3 bit的0即可。该方法虽不是很精确,但可以满足本系统设计要求。

4 小结

本设计以FPGA为核心,实现了PAL转VGA接口的视频流显示。详细介绍了隔行转逐行,帧频、分辨力转化,SRAM读写,乒乓操作等方法。实验验证,该设计实时显示效果良好,设计简单,具有较高的实用价值。

[1]SAA7111 Enhanced Video InputProcessor(VIP)[EB/OL].[2010-10-20].http://www.datasheetdir.com/SAA7111+Video.

[2]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2007.

[3]刘凌.数字信号处理的FPGA实现[M].北京:清华大学出版社,2002.

[4]徐洋,黄智宇.基于Verilog HDL的FPGA设计与工程应用[M].北京:人民邮电出版社,2009.

[5]龙在云,武斌.DVI数字视频图像数据的实时截取方法[J].电视技术,2010,34(2):32-33.