基于DDS的正弦波信号发生器的设计★

2011-08-07崔唯佳高磊陈晓军

崔唯佳,高磊,陈晓军

(中北大学信息探测与处理技术研究所,山西 太原 030051)

0 引言

随着科学技术的发展, 普通的性能单一的波形发生器已经越来越不能满足实际的需求, 要想实现性能复杂、波形多样的发生器, 频率合成技术是一种较好的实现方法。频率合成技术分为直接数字频率合成技术( Direct Digital Frequency Synthesis, 简称DDS 或DDFS)、间接频率合成技术、直接模拟频率合成技术。基于DDS的任意波形发生器对硬件要求低, 频率切换速度快,很容易提高其频率分辨率和改变其频率范围。本文采用基于DDS技术结构构造正弦波形发生器, 充分利用单片机灵活的控制、丰富的外设处理能力和外设的替代性,实现频率、幅值可调的函数波形输出,同时可以根据需要方便地实现各种比较复杂的调频、调相和调幅功能, 具有很好的实用性。

1 基本理论

DDS的工作原理:DDS是以相位累加器为核心的,它由一个N位字长的二进制加法器和一个N位寄存器组成,作用是对频率转换字(w )进行线性累加; 正弦查找表中所对应的是一张函数波形查寻表, 对应不同的相位码址输出不同的幅度编码。相位累加器累加输出的序列对查找表寻址,得到一系列离散的幅度编码。该幅度编码经D/A转换后得到对应的阶梯波,最后经低通滤波器平滑后可得到所需的模拟波形。相位累加器在基准时钟的作用下,进行线性相位累加, 当相位累加器加满时就会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS 的信号的一个频率周期。输出频率 f t0为:

2 设计思想

2.1 系统原理框图

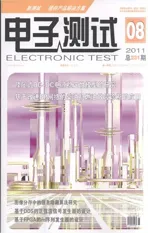

DDS以数控振荡器的方式产生频率、相位可控制的正弦波,主要由基准时钟fs、相位累计器、幅度/ 相位转换电路、正弦查找表、D/A转换器组成。如图1所示,它采用数字技术重复扫正弦查找表来获取数据,构筑处所希望的波形。

图1 系统原理框图

2.2 硬件结构图

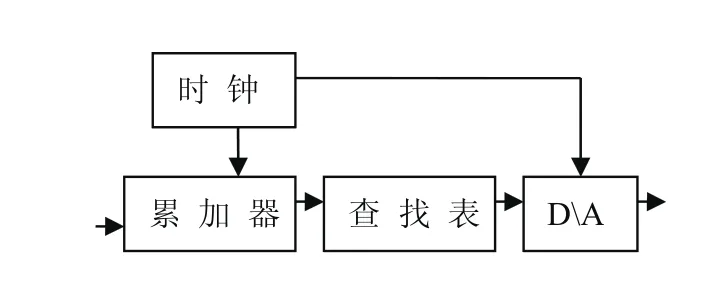

硬件结构总体方案是通过电源芯片对FPGA供电,由JTAG接口作为程序下载口,最后由示波器观察波形,如图2所示。

图2 硬件结构图

2.3 软件设计

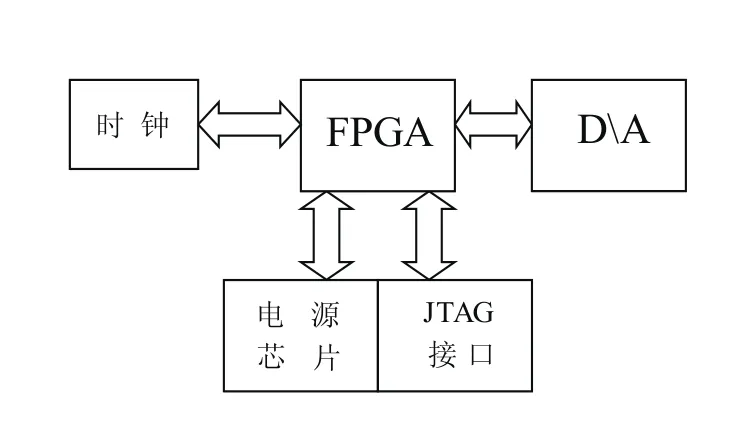

系统软件设计采用模块化思想, 可移植性、可读性强。DDS算法利用循环溢出的相位累加器产生正弦函数的相位变量。相位累加器每溢出一次, 就代表正弦波形的一个周期。相位累加器输入的频率控制字控制生成的正弦波形的频率, 累加器的瞬时相位输出作为ROM表的地址。ROM表是存有正弦采样值的存储器。系统流程图如图3所示。

图3 系统流程图

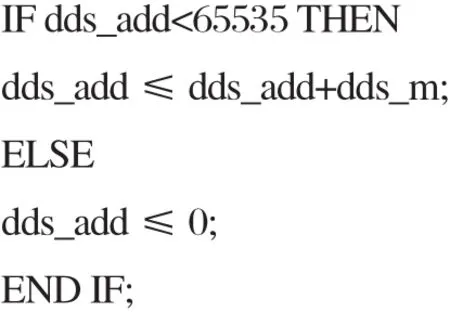

2.3.1 地址累加器模块设计

地址累加器的作用是将频率转换字输出的频率控制字进行逐步累加,并把结果送到查找表中进行寻址。部分VHDL源代码如下:

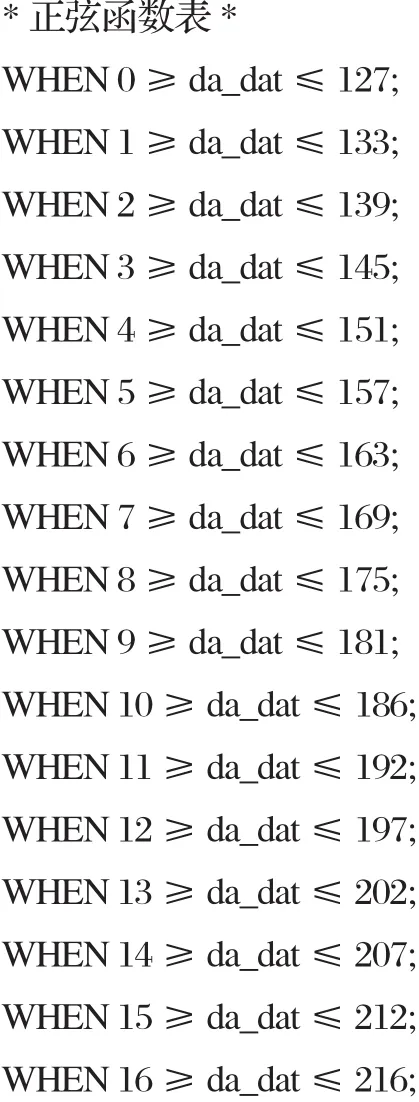

2.3.2 正弦查找表进程

正弦查找表:表中所对应的是一张函数波形查寻表,对应不同的相位码址输出不同的幅度编码。相位累加器累加输出的序列对查找表寻址,得到一系列离散的幅度编码。该幅度编码经D/A转换后得到对应的阶梯波,最后经低通滤波器平滑后可得到所需的模拟波形。部分VHDL语言如下(查找表数据过多,只罗列一部分数据):

3 实验结果

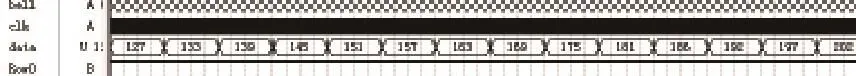

根据以上设计,可得出正弦波信号发生器的仿真图,如图4所示。正弦波模拟信号波形图,如图5所示。由此可知实验方案满足要求。

图4 仿真图

图5 正弦波

4 结束语

本文论述的基于DDS技术的正弦信号生成系统简单易行,具有很强的实用性,通过VHDL语言编写程序完成各个模块的产生,进而完成整个系统,为相关领域提供了较好的模型和方法,具有很强的实际使用价值。

[1]李晓芳,常春波,高文华.基于FPGA 的DDS 算法的优化[J].仪器仪表学报,2009(z1):896-898.

[2]傅文斌.遥控遥测系统[M].北京:机械工业出版社,2007:210-212.

[3]曾繁泰,陈美金.VHDL 程序设计[M]. 北京:清华大学出版社,2007:5-22.

[4]邬杨波,王曙光,胡建平.有限状态机的VHDL设计及优化[J].信息技术,2008,28(1):75-78.

[5]张力军.数字通信简介[J].电子工业大学学报,2003:552-552.

[6]夏宇闻.Verilog HDL 数字系统设计教程[M].北京:北京航空航天大学出版,2009.

[7]William,Sandoval.The ZigBee Revolution[DB/OL].[2005-09-23].

[8]林静宜.基于DDS 的多模式信号发生器的设计与实现[D].武汉:华中科技大学, 2008.