基于FPGA的高精度多通道采集系统及其性能分析

2011-07-07洑涵妤

洑涵妤

(江苏技术师范学院 计算机工程学院,常州 213001)

0 引言

随着信息技术的飞速发展和数据采集系统的广泛应用,数据采集系统的性能要求也越来越高。在图像处理与音频信号处理等高速、高精度和实时性强的处理中,高性能的数据采集系统尤为重要。

数据采集系统实时性与同步性的要求既限制了低速单片机数据采集系统的使用,也限制了基于DSP频繁中断的数据采集系统的采纳。如采用可编程逻辑器件设计数据采集系统具有开发周期短、集成度高、设计费用低、工作频率高、功耗低、编程配置灵活等优点。本文介绍一种基于FPGA的高精度多通道的数据采集系统,并对这个系统的高精度、多通道和高速度等性能进行了分析。

1 系统概述

基于FPGA的高精度多通道采集系统(如图1所示)由多路复用选择器、模数转换器、高速精密放大器、数模转化器和FPGA组成。多路模拟信号由多路复用选择器引入,经选择后通过高速精密放大器进行滤波处理,然后再进入高速精密模数转换器进行数据转换,在此过程中,模拟输入信号选择的控制和模数转换器的控制均由FPGA实现,而转换后的数字信号通过FPGA传输给处理模块。数字控制电机转动过程中,数字控制信号通过数模转换模块转换成为模拟信号。数模转换模块主要是和模数转换模块进行联调来证明整个采集系统具有高精度性能。

图1 数据系统采集框图

2 系统硬件结构

2.1 多路复用选择器

多路复用选择器采用的是ADI公司生产的ADG1406,包括16个单端通道。它可以将其中一个输入切换到公共输出,具体由4位二进制地址线决定(A0、A1、A2和A3)。这款器件EN引脚高低电平可以用来使能或禁用器件,禁用时所有通道都被关断;启用时每个通道都执行双向操作,输入信号范围可扩展至电源电压。这些开关具有超低的导通电阻以及导通电阻平坦度,是低失真度至关重要的数据采集与增益开关应用的理想解决方案,iCMOS®架构具有超低功耗性能[1]。

采集系统做了正负10V-0V的标定输入和10个单端模拟输入通道,其中IN1-IN9为模拟输入。正负15V电源供电,每个电源引脚上要接一个0.1uF的去耦电容,EN引脚接在高电平上。FPGA的I/O脚与A0、A1、A2和A3相连,通道选择的控制是通过写逻辑来完成的,D引脚是输出引脚。

2.2 高速精密放大器

OPA827是一款JFET输入运算放大器,其具有低功耗、超低噪声、小封装尺寸以及高带宽等特性和较好的AC性能与DC精度。尤其18MHz GBW、22V/us压摆率以及1kHz频率下的0.0004%总谐波失真(THD)的AC参数充分保证了系统的高速性[2]。

OPA827与电阻R17、电阻R18和电容C3组成一个单极点反相有源滤波器来实现二阶滤波,其具有较低的与电阻R17相同的输出阻抗[3]。采用±15V电源供电,分别在每个电源引脚接上0.1uF和10uF的去耦电容。从ADG1406出来的模拟信号由Ain进入滤波器,由Ain_opa输出。

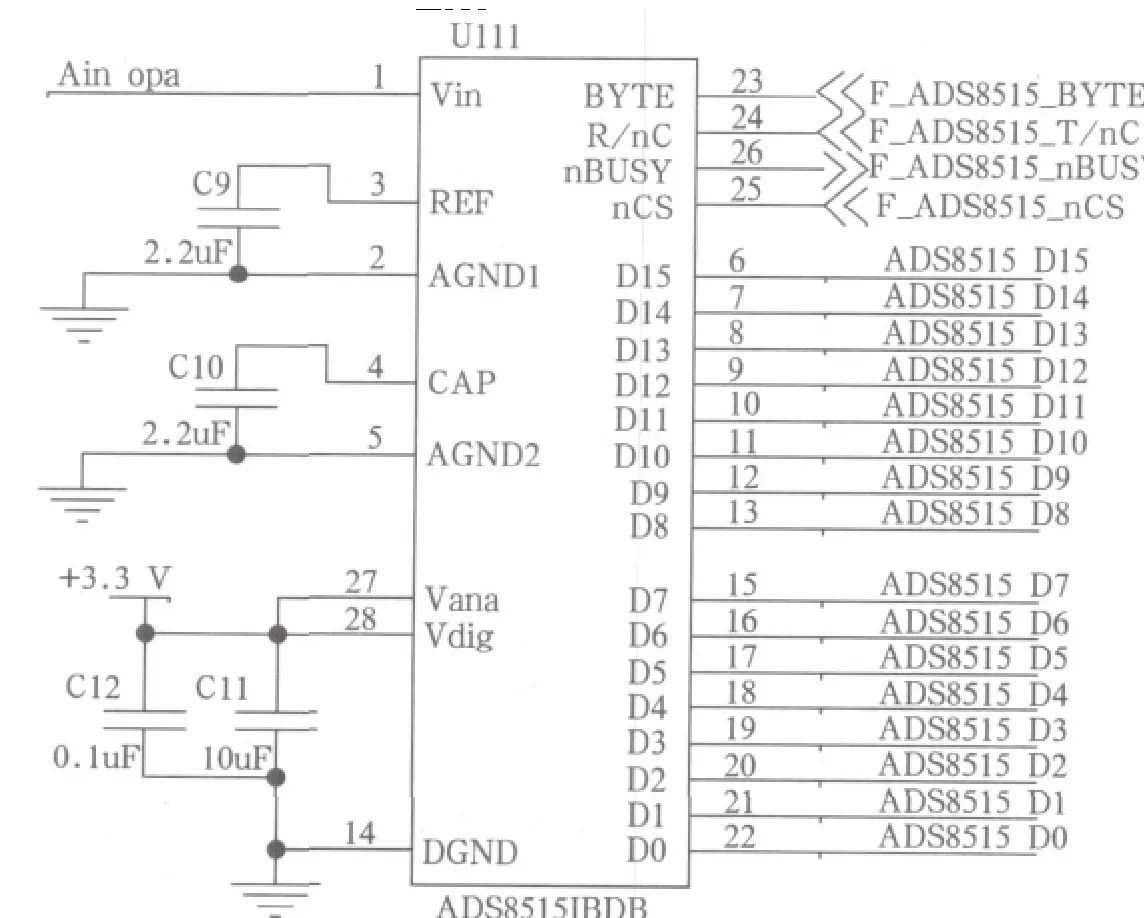

2.3 A/D模块

ADS8515是16位并行A/D转换器,其采样率为250KSPS。它属于逐次逼近寄存器型(简称SAR型)A/D转换器,如图2所示。其内部通常具有采样保持器,转换速率快[4]。Vin为信号输入引脚,A0~A15为转换输出的数字信号。采用3.3V的电源供电,不需要再通过电平转换器件即可以实现器件与FPGA的直接相连。

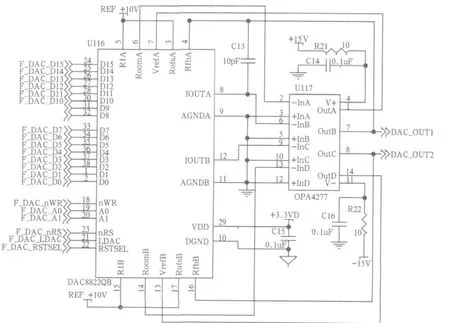

2.4 D/A模块

DAC8822是双路,并行输入的16位乘法数模转换器,2.7V-5.5V的单电源供电,模数转换器输出电流的满偏量程由其外部参考电压的大小决定。内部电阻(RFB)提供温度跟踪来得到满偏量程,同时并行输入接口决定了器件高速通信[5]。

图2 ADS8515硬件接线图

暂存于FPGA的数字信号从D0-D15流入模数转换模块。FPGA通过对A0、A1写逻辑来实现输出通道选择,同时对nWR和LDAC进行时序控制。此外,为了得到更好的输出模拟信号性能,在输出后端加入一个电压跟随器OPA4277,将原电流输出转换成电压输出,如图3所示。

2.5 FPGA

图3 模数转换模块硬件连线图

FPGA采用ALTERA公司Cyclone III系列的EP3C16F484C8N,静态功耗小于0.25瓦。采用+3.3V、+2.5V、+1.2V分别给不同区进行供电。灵活的I/O控制使得编程简化,电路设计方便[6]。采用AS和JTAG配置模式,配置芯片是EPCS16SI8N,器件的时钟配置为50MHz。

3 系统软件设计

采用Altera Quartus II9.0编写系统软件,用硬件语言verilog来实现。在这个采集系统中,要对多路复用选择器、D/A转换器和A/D转换器进行编程。通过对ADG1406的A0、A1、A2、A3进行写逻辑,从而决定输入通道的选择,可以分别选择0000-1111等16个通道的选择。

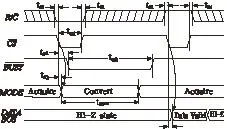

3.1 A/D转换器的编程

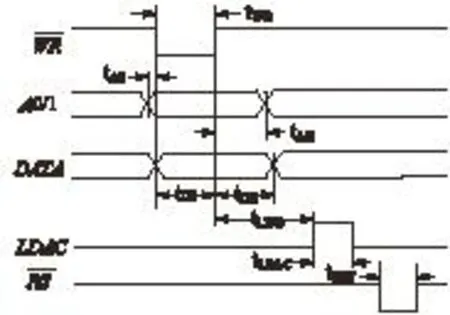

对A/D转换器的编程,主要是对A/D转换器的控制信号进行写逻辑。如图4所示,为以信号作为A/D转换器数据转换和数据读取的控制时序图。首先,检测和的状态,直到处于高电平和处于低电平;然后下降沿触发A/D转换器开始转换。当A/D转换器开始转换时,变为低电平,直到转换结束。在和处于低电平至少tw1(典型值为40ns)时间后,置为高电平。在转换结束后,器件内部寄存器会自动进行更新,变为高电平。对于数据的读取,同样需要检测和的状态,直到和都处于高电平,此时以的下降沿触发数据读取。

图4 为转换和读取控制的时序图

3.2 D/A转换器的编程

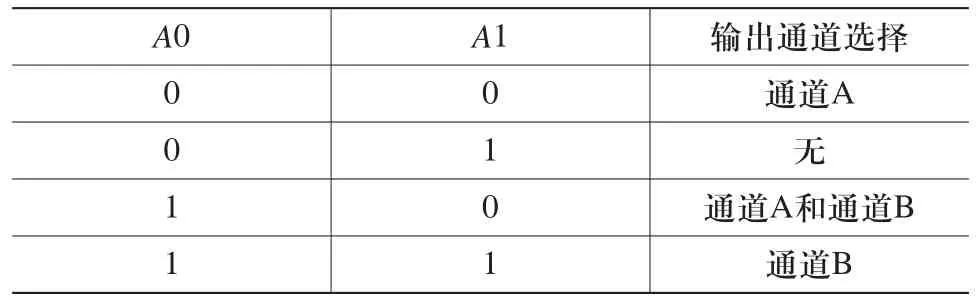

表 1 D/A转换器输出通道选择情况

图5 数模转换器编程时序图

4 系统实验结果及其分析

在测试过程中,为了验证本数据采集系统的性能,将D/A转换器的输出端接到多路复用选择器的输入端,即将D/A转换器的模拟输出作为A/D转换器的输入,然后将D/A转换器的数字量设定值和A/D转换器的输出结果作比较。将D/A转换器的模拟输出值转化成输入十六进制数字量,与实测结果十六进制数字量进行比较。一共分两组通过最小二乘标定将实测结果向理论结果逼近,一组测试值为正,一组为负,其采集值如表2所示。

表2 30个数据采集值

续表

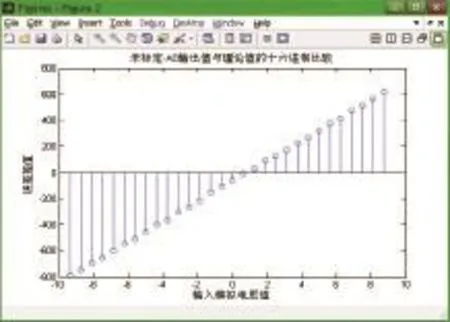

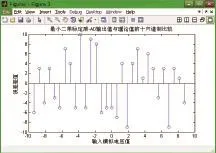

利用MATLAB绘图如图6、图7和图8所示。图6为输入模拟电压值与实测AD输出的曲线图;图7为未标定AD输出值与理论值的十六进制差值散点图;图8为最小二乘标定后AD输出值与理论值的十六进制差值散点图。

图6 表示输入模拟电压值与实测AD输出的曲线图

5 结论

图7 未标定-AD输出值与理论值的十六进制差值散点图

图8 最小二乘标定后-AD输出值与理论值的十六进制差值散点图

为了大大增加输入通道,采用多路复用选择器作为模拟信号输入前段;FPGA的电路设计和编程由于灵活多变的I/O而显得简单。采用模数转换器与数模转换器之间相互联调,可以在没有高精密电源和稳定模拟输入信号的情况下,对采集系统进行有效的评估。最后通过对结果的比较清楚地得到采集系统的最终精度14位。

[1] ADG1406,16-Channel,Differential 8-Channel, iCMOS Multiplexers [Z]. ADI.Inc.

[2] Bonnis Bake著, 李喻奎, 译. 嵌入式系统中的模拟设计[M]. 北京:北京航空航天大学出版社, 2006

[3] OPA827 Low-Noise, High-Precision, JFET-Input OPERATIONAL AMPLIFIER[Z]. TI. Inc. 2009

[4] ADS8515 16-BIT 250-KSPS SAMPLING CMOS ANALOG-TO-DIGITAL CONVERTER [Z] .TI. Inc. 2005.

[5] DAC8822 16-Bit, Dual, Parallel Input, Multiplying Digitalto-Analog Converter[Z].TI. Inc. 2008.

[6] Cyclone III FPGA Family datasheet[Z]. Altera, Inc. 2008.