SPI总线扩展PLC输入点数的设计与实现

2011-07-05曹凤莲

曹凤莲,李 磊,周 平

(淮阴师范学院物理与电子电气工程学院,江苏 淮安 223300)

0 引言

可编程控制器(PLC)具有结构简单、编程方便、性能优异和应用方便等特点,尤其近年来通用开发平台与软系统的开发,使得PLC成为当今用途最为广泛的工业控制器,但是随着应用复杂度的提高,PLC的应用瓶颈也开始显示出来,如EC10系列PLC主模块输入点数的范围是16点到60点。主模块以TMS470R1A288为控制核心,该芯片虽然有丰富的输入点数资源,但是一部分输入接口复用于控制和通讯功能之后,留作输入点数的只有30点左右,对于大于30点的模块必须考虑输入点数的扩展。在文献[3]、[4]中,这样复杂的控制采用多级PLC控制,将使整个控制系统复杂而不稳定。如果在PLC主模块中增加I/O端口数,将会减少使用PLC的级数,从而降低系统的复杂度。

本文提出了一种通过MCU的SPI总线与移位寄存器相结合扩展16路输入的设计方法。SPI总线模块工作在Master方式下,向HC165提供同步时钟输入。在EC10系列主模块中TMS470R1A288的SPI1用于主模块与扩展模块I/O之间的通讯,SPI2用来扩展主模块本机的I/O点数。SPI的信号线SPI2SOMI(主入从出)用于扩展输入点数,连接HC165的串行输出端。

1 系统设计

1.1 SPI总线时序选择

SPI总线用于微处理器与外设或其它处理器之间的高速通讯,它的时钟速度、数据位长度、时钟模式可以灵活控制,实质上是一个长度可编程的移位寄存器。SPI总线具有同步串行输入和输出接口,串行数据流在同步时钟的作用下移入或移出设备,且数据位数和同步时钟速率是可编程的。

SPI总线以主从模式工作,其接口的结构见参考文献[5],其中,主入从出(SOMI)用于数据输入,主出从入(MOSI)用于数据输出,还有控制时钟端(SPICLK)和片选端(NSS)。根据SPI时钟的相位和极性的不同组合,SPI模块有四种时钟模式。CPOL=0,串行同步时钟的空闲状态为低电平;CPOL=1,串行同步时钟的空闲状态为高电平。可通过配置时钟相位(CPHA)来选择两种不同的传输协议之一进行数据传输。如果 CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降),数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降),数据被采样。

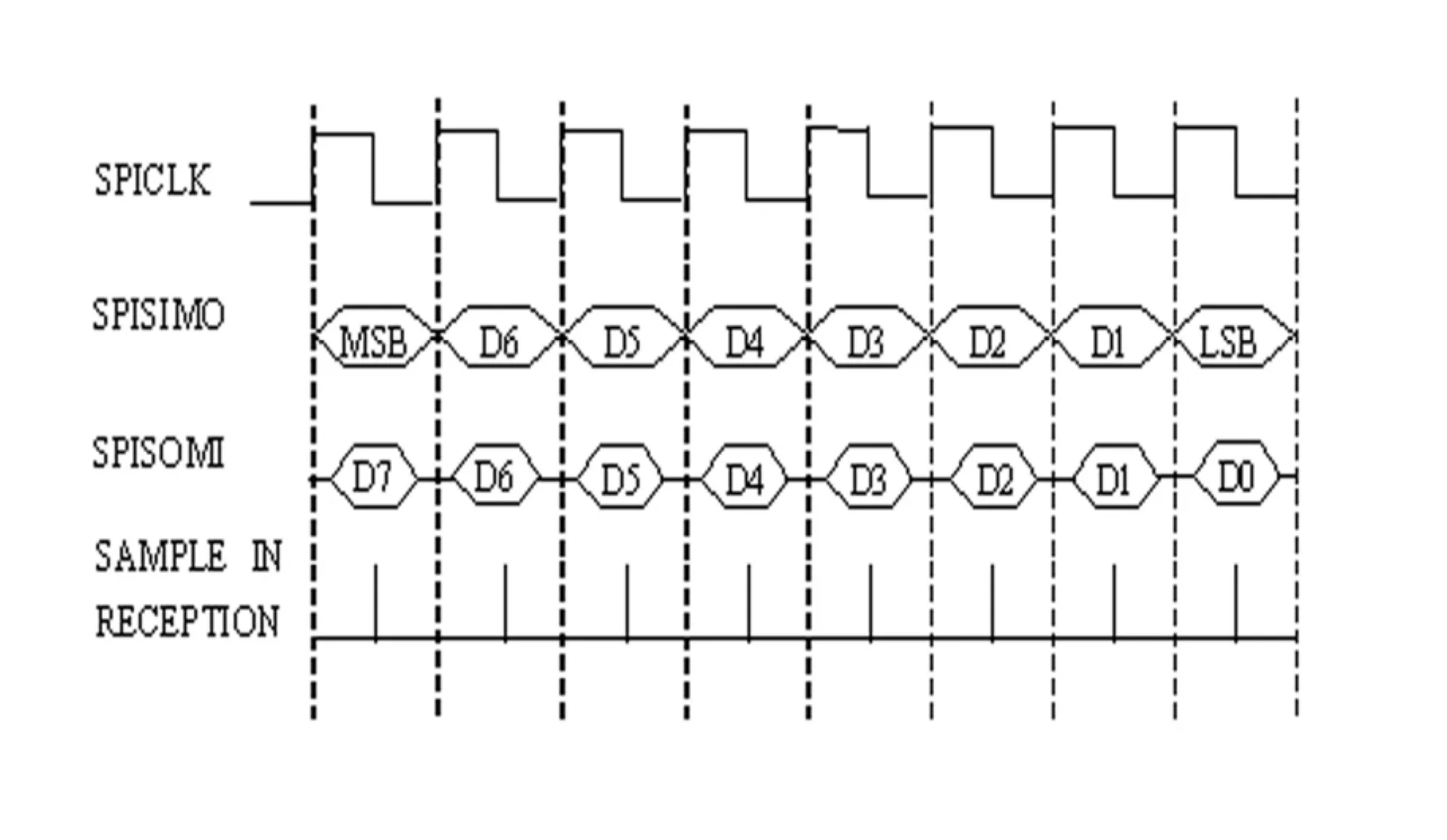

根据SPI时钟的相位和极性的不同组合,TMS470R1A288的SPI模块有四种时钟模式,这样可以适应不同的外部设备。HC165是由D触发器构成的寄存器,状态的变化都是发生在时钟脉冲的上升沿。根据HC165的时序特点,设计中选用SPI的时钟模式0,其时序图如图1所示。

图1 SPI时钟模式0的时序

从图1中可以看出,SPICLK的初始状态应该为低电平,SPISIMO的数据在时钟的上升沿输出,而SPISOMI的数据在时钟的下降沿被SPI模块采样锁存。

74HC165是8位并行读取或串行输入移位寄存器,方便多片级联和与SPI总线相连接。结合SPI总线的特点,因此选择74HC165来扩展嵌入式智能PLC的输入点数。74HC165状态的变化都是发生在时钟脉冲的上升沿,根据其时序特点及SPI时序特点,设计中选择SPI时钟模式0,即SPI总线模块工作在Master方式下。

HC165扩展16路输入的原理如图2所示,两片HC165为级联的关系,U1的串行输出端QH连接到U2的串行输入端SER,而U2的串行输出端QH连接到TMS470R1A288的SPI总线SPI2SOMI。两片HC165的时钟输入端同时接到SPI的时钟信号SPI2CLK。TMS470R1A288的另外一个控制信号为UDTX,同时连接到U1和U2的并行信号装入端SH_LD。UDTX上的滤波电容C1需要根据信号的实际应用速率来选取。

当SH_LD为低电平时,HC165会装入并行输入信号,所以在UDTX上加上拉电阻R1使CPU在不发出装入信号时SH_LD保持高电平。另外,在SPI2CLK端加下拉电阻R2,保证在CPU上电初始化时,SPI的时钟信号处于一个固定的状态,不至于是不确定的杂乱信号;同时要满足本设计中选取的SPI时钟模式的要求,SPI2CLK在初始状态时必须处于低电平。

1.2 电路设计

从HC165的时序图可以看出,8位并行输入数据装入移位寄存器后,最高位H直接输出到了串行输出端QH,当第一个移位时钟脉冲SPI2CLK的上升沿到来时,HC165的最高位H将从QH丢失,第七位输入G(LX17)的状态将会出现在QH。而且,SPI对SPI2SOMI的数据是在移位时钟脉冲SPI2CLK的下降沿被采样并锁存的。如果8位输入信号对应的接到HC165的输入端A~H的话,将会造成输入数据的最高位丢失。因此,U2的并行输入最高位H管脚接地,而8位并行输入的最低位LX10接到了下一级芯片U1的最高位H。图2中的这种设计可以使SPI采样到的第一个数据是LX17,而第八个数据是LX10。

图2 SPI输入扩展电路

SPI在同步时钟的作用下读入外部数据时,数据的第一位(HC165的第七位G)首先移入接收寄存器SPI2DAT0的最低位,然后依次向最高位移位,也就是说首先移入的数据位最终是SPI读入数据的最高位,这就决定了外部扩展输入LX10~LX17和LX20~LX27在HC165上的排列顺序。为了方便,在程序中将LX10~LX17作为一个字节处理,那么在HC165的接线上应该从LX17~LX10由高到低排列。

I/O电压为3.3V,因此设计电路中电源采用3.3V直流电,考虑系统外引线对 PLC的干扰,LX10~LX17和LX20~LX27接经过光耦隔离和门电路整形后的输入信号,而且电路中使用很多滤波电容,以降低扩展电路对PLC主模块的干扰。

2 系统编程实现

硬件系统设计完成后,通过软件编程进行调试。TMS470R1A288的SPI模块数据的接收是通过寄存器SPI2DAT0实现的。SPI工作于主模式时的读过程如下:

需要接收的数据从 SPI2SOMI端口移入SPI2DAT0的最低位。在设定的数据位数发送完成后,接收到的数据自动从 SPI2DAT0拷贝到SPI2BUF,读寄存器SPI2BUF就可以接收到数据。

输入扩展的主函数为Unsigned char ReadX(unsigned char*inputArray,unsigned char input-Num),*inputArray为接收到的输入量,inputNum为输出量的个数。接收的数据从SPI2SOMI端口移入SPI2DAT0的最低位,设置UDTX=1,读输入数据,当SPI2中断或读数读完,运行结束,具体程序如下:

在程序中首先要完成SPI2的初始化,如下所示:

读扩展输入数据的函数如下:

通过初始化及控制输入扩展主函数Unsigned char ReadX(unsigned char*inputArray,unsigned char inputNum)实现了SPI在时钟模式0条件下,时钟速率100K、数据长度8位、串行16位的扩展输入。

3 结束语

利用SPI总线时钟速度、数据位长度、时钟模式可以灵活控制,且具有同步串行输入、输出接口,以及数据位数和同步时钟速率可编程等优势,提出了SPI总线与移位寄存器74HC165相结合扩展PLC主模块输入点数的设计方法,电路设计简单,成本较低,而且输入扩展是一个独立的模块,应用起来比较方便,这种设计方案可以广泛地应用到PLC上。

[1]吴宁,葛芬.可编程逻辑控制器通用开发平台的设计与实现[J].仪器仪表学报,2007,28(8):1486-1491.

[2]吴玉香,周东霞,林锦赟.嵌入式软PLC系统的研究和实现[J].计算机工程,2009,35(10):235-237.

[3]张园园,龚庆武.基于IEC61850的数字化变电站开装设备接口装置[J].电力自动化设备,2009,29(1):108-111.

[4]王健强,王长润,孙纯哲,等.多PLC及多级现场总线在机器人焊装线中的应用[J].上海交通大学学报,2008,42(增刊):20-24.

[5]胡小乔,薛敏彪,王健.基于i.MX27处理器的串行SPI接口设计[J].计算机测量与控制,2011,19(2):442-444.

[6]Andrew Sloss,Dominic Symes,Chris Wright,etal.ARM System Developer's Guide:Designing and Optimizing System Software[M].Leiden:Elsevier,2003.