基于ARM+FPGA+多DSP的嵌入式实时图像处理系统

2011-07-02任晓波赵文龙陈思平

任晓波,赵文龙,唐 盛,陈思平,

(1.南昌航空大学 测试与光电技术学院,江西 南昌 330063;2.南昌航空大学 信息工程学院,江西 南昌 330063)3.深圳大学 医学院生物医学工程系,广东 深圳518060;

实时图像处理、高速数据运算处理要求其系统具有对数据处理速度快、数据吞吐率高以及多任务处理功能。目前大多数方案都是采用HPI数据传输方式,将ARM和DSP进行组合完成一些图像处理,DSP处理器只是完成图像采集、压缩、编码等简单的处理[1]工作,不能满足实时的智能识别或大数据量运算的视频处理要求。在应用领域方面也会因其处理速度问题受到一定的限制。

例如,胎儿性别屏蔽项目中,要对实时视频进行性别部位的检测和屏蔽,若采用单DSP则会出现漏帧或视频不流畅;应用于高速运动物体跟踪时,单DSP无法实现实时运动物体跟踪,例如汉王科技的运动检测和海康威视运动检测,都不能实时检测,即使检测也会出现漏检现象和视频不流畅。当处理4CIF或者更大图像时,单DSP的处理能力又会下降,虽然可以将图像缩小进行处理,但是缩小图像则会丢失一些重要的图像信息,使得智能识别准确率下降。

针对上述情况,设计一种能够实现进行快速信号处理和数据交换的实时图像处理系统很有必要。

1 系统结构

1.1 结构

系统功能:利用S3C6410进行数据整合、任务调度、人机交互;利用TMS320C6416进行算法运算;每个DSP与FPGA都是无缝连接。设计中利用FPGA实现的FIFO进行与DSP之间的高速数据传输以及ARM对多个DSP的任务调度处理等。

系统结构如图1所示。系统由1个ARM11处理器S3C6410(主处理器)与 4个 TMS320C6416(720 Hz)(从DSP)通过 FPGA(EP2C70~7)实现互联的 ARM+多 DSP的嵌入式图像处理系统。所有的DSP都通过外部存储器接口(EMIF)与 FPGA无缝相连,每个 DSP之间的数据传输是通过FPGA内部互联FIFO网络实现。

图1 系统结构

图2所示是一种互联的FIFO网络结构和高速数据传输网络结构。主处理器通过DMA数据访问模式与FPGA的双口FIFO连接,从而实现与FPGA通过FIFO连接的所有从DSP进行通信,所有FIFO都是双向的,FIFO及其读写控制逻辑都在FPGA内部实现。

FPGA中的FIFO读写状态控制、各从DSP之间通信的同步握手信号、S3C6410处理器数据请求等逻辑信号,都是由每个DSP的一部分GPIO口与EP2C70的I/O口连接实现。

1.2 特点

图2 一种高速数据传输网络互联结构

系统结构具有可重构特性,在硬件平台不变情况下,只需通过改变FPGA程序代码就可以完全改变系统结构,以适应不同的算法结构。如图2中屏蔽DSP1~DSP4之间的互相通信,即可组成主从并行的流水线结构;若需要串行的流水线结构,只需将DSP1~DSP4的其中一个与S3C6410通信即可;若需要设计更复杂的串并混合性结构,也只需改变FPGA的代码就能够很容易地实现。

2 S3C6410的DMA与FPGA的软FIFO接口实现

2.1 S3C6410简介

S3C6410是三星公司的产品采用ARM1176JZF-S核,包含16 KB的指令数据Cache和 16 KB的指令数 TCM;ARM Core电压为1.1 V时,可以在553 MHz下运行。在1.2 V时,可以在667 MHz下运行。通过AXI、AHB和 APB组成的 64/32 bit内部总线与外部模块相连。SROM Controller:6个片选,支持SRAM、ROM和 NOR Flash以及支持 8/16 bit,每个片选支持128 MB。JPEG Codec:支持JPEG编解码功能,最大尺寸为4 096×4 096。2D GRAPHICS:2D加速,支持画点/线 ,bitblt功能和Color Expansion。 3D GRAPHICS:3D 加速。

S3C6410可支持4个DMA控制器,用于系统总线内部或与外围总线之间的数据交换,每个控制器包含8个通道,支持8/16/32 bit传输。现以外部DMA请求为例简要介绍DMA的工作过程。图3所示为DMA基本工作时序。

图3 DMA基本工作时序图

当需要进行DMA操作时,外部DMA请求引脚XnXDREQ置为低电平。此时DMA控制器向CPU发出占用总线的请求,当总线请求成功后,XnXDACK引脚变为低电平,表示CPU已经将总线使用权交给DMA控制器,可以进行数据传输。当数据传输完成后,应答信号XnXDACK置为高电平,通知CPU完成一次DMA操作。

S3C6410提供了三种不同的DMA操作模式:单服务命令模式、单服务握手模式和全服务握手模式。在利用DMA进行数据传输前必须对其相关寄存器进行设置,包括源地址寄存器、目的地址寄存器和各自的控制寄存器以及配置DMA模式的控制寄存器等。

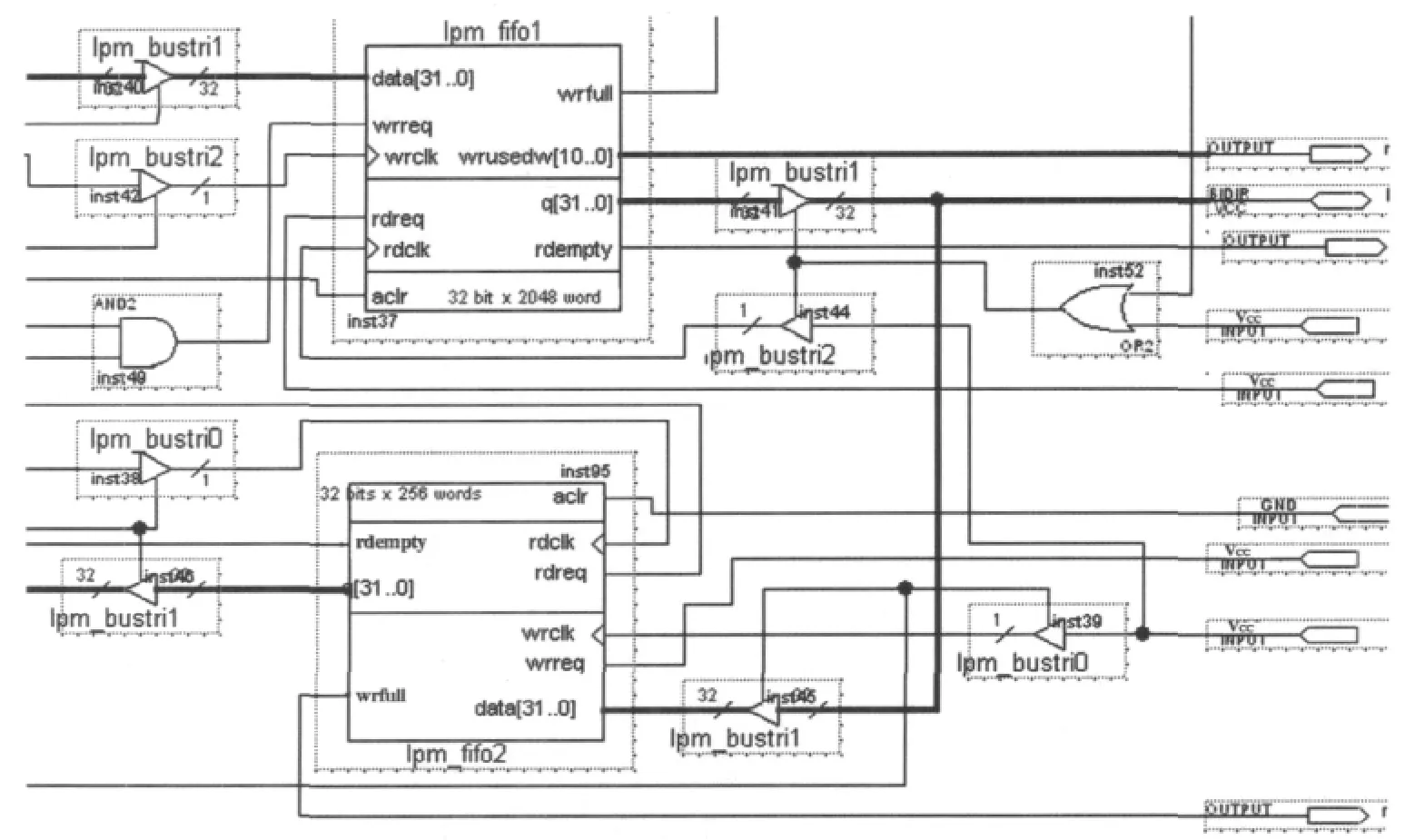

2.2 FPGA及其实现FIFO[2]

采用FPGA实现多时钟电路系统时,需要处理不同的时钟域之间速率匹配问题,可利用FPGA内部生成的异步FIFO来处理。异步FIFO主要由双端口RAM、写地址产生模块、读地址产生模块、满空标志产生模块组成。双端口RAM由FPGA的Block RAM块构成,FPGA采用Atera公司的EP2C70-896C7,其Block RAM读写时钟频率可以达到216.73 MHz,因此选用Block RAM作为存储体,不仅速度快,而且设计简单。设计时,一个端口配置成写端口,另一端口配置成读端口,然后把Block RAM的管脚与相对应的控制信号相接即可。读写地址通过FPGA芯片内部的二进制进位逻辑产生,以对应Read_En/Write_En作为使能信号在读/写时钟的控制下进行计数。空或满标志可以由读或写地址的相对位置来获得。本系统采用2个FIFO组成一路数据传输通道,双向FIFO的设计图如图4所示。

2.3 S3C6410的DMA与软FIFO接口实现

根据DMA接口原理,设计S3C6410与FPGA之间的接口简图如图5所示。

读时钟由ARM的时钟输出引脚CLKOUT0提供。CLKOUT0根据S3C6410内部寄存器的设置可以输出不同的时钟频率。FIFO输出数据经过以nGCS4为选通信号的缓冲器 (Buffer)后接到S3C6410的数据总线上。nGCS4是S3C6410存储空间中BNAK4的片选信号,当S3C6410对该信号对应存储空间进行读写操作时,BANK4为低电平,其余时间均为高电平。

FIFO的写请求信号由S3C6410与FIFO的满状态共同控制。当S3C6410发出START信号并且FIFO未满时,写请求信号为高电平,FIFO在写时钟的控制下写入数据;当START信号撤销或者FIFO满时,写请求信号变为低电平,停止写操作。

图4 双向FIFO设计图

图5 S3C6410与FPGA接口

FIFO的读操作与S3C6410的DMA操作配合进行。系统采用单服务命令模式的DMA操作,每次传输一个字节的数据。当DREQ0信号变为低电平时,DMA操作开始,每次传输一个字节后产生一个DACK0应答信号,而且只要DREQ0为低电平DMA操作就继续进行,直到DMA控制寄存器中的计数器为0,产生DMA中断。根据上述时序特点,将FIFO的空信号作为DMA的请求信号DREQ0。当CCD输出的数据写入FIFO中时,空信号跳变为低电平启动DMA操作,同时以DACK0信号作为FIFO的读请求。每次DMA传输完成后应答信号使FIFO的读指针移动一位,以实现数据的快速准确采集。

3 图像采集模块

用可编程视频输入处理器SAA7113H进行视频信号处理。SAA7113H内部集成了强大图像色度、亮度处理功能以及多种输出模式[3];有32个工作寄存器,在系统复位时,必须通过I2C总线对其进行初始化。本系统使用灰度图像,没有使用色度信号,所以数据线为8 bit。SAA7113H与FPGA的接口如图6所示。

在本系统中,FPGA内部需要设计一逻辑时序完成图像数据的采集,数据的传输采用异步FIFO完成。采用此方案可以解决CCD输出数据频率与从DSP和ARM不匹配的问题。

4 DSP的EMIFA与FPGA实现的软FIFO接口

4.1 DSP的EMIFA接口[4-5]

DSP(TMS320DM6416T)之间的通信都是通过外部存储器接口(EMIFA)访问片外存储器进行的。EMIFA由64 bit数据线D[63:0]、20 bit 地 址 线 A[22:03]、8 bit字节使能线 BE[7:0]、4 bit地址区域片选线/CE3~/CE0和各类存储器的读/写控制信号组成。TMS320DM6416T的每个/CEx空间都有256 MB寻址空间,并且可配置为与SRAM、SDRAM、ZBTSRAM、Flash、FIFO等各类存储器接口。EMIFA读/写各类存储器的时钟可由软件配置为 EMIF的 AECLKIN、CPU/4或CPU/6。本设计配置为 EMIF的AECLKIN,且为 133 MHz。

图6 SAA7113H与FPGA的接口

4.2 EMIF与软FIFO接口实现

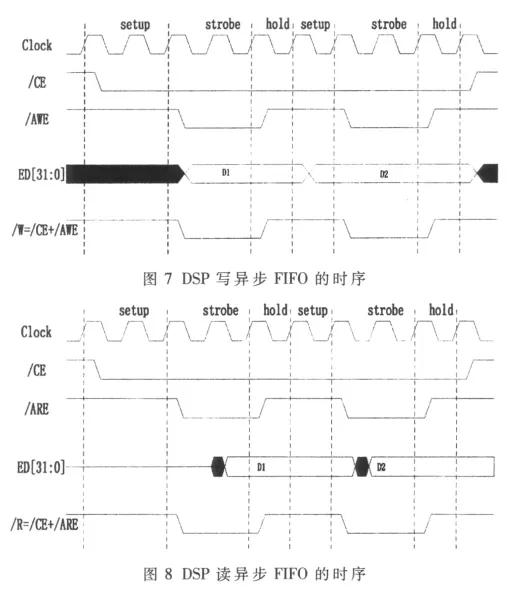

DSP之间通过EMIF口与FPGA实现的异步FIFO进行通信。EMIF异步接口的每个读/写周期分为三个阶段:建立时间(SETUP)、触发时间(STROBE)、保持时间(HOLD),且每个阶段时间可编程设置,以适应不同的读写速度。DSP读写异步FIFO的时序图分别如图7、图8所示[6]。DSP读写FIFO控制信号由FPGA产生,其逻辑关系如下:

写 FIFO信号:writ_clk=AECLKOUT

writ_req=!(/CE+/AWE)

读 FIFO信号:read_clk=AECLKOUT

read_req=!(/CE+/ARE)

另外,写 FIFO的DSP要相应为满状态标志,读FIFO的DSP则相应为半满状态标志。

5 DSP之间数据通信[7]

为了设计一款通用性比较强的图像处理平台,各处理器间的数据传输必需达到通用性,这样可以针对不同系统的应用,只须修改图像处理算法代码,而不须要修改各处理器之间的通信。具体设计分为如下两部分:

(1)数据通信协议说明(x=0,1,2,3)

Se/Re(Send/Receive)[0]:ARM通过 FPGA请求 DSPx接收(该数据位为1)或发送。

ARM[1:3]:该段数据为DSPx向FPGA发出请求数的DSP编号。

DSPx[4:6]:ARM处理器向FPGA提出要求响应的DSP的编号。

Da_Le(Data_Leng)[7:18]:ARM请求 DSPx接收或发送的数据长度。

Da_Un(Data_Unit)[19]:该标志位表示是否按照 Data_leng*K(1K=1 024 bit)的数据长度传输数据,若为 1,表示接收或发送数据长度为Data_leng*K(1K=1024 bit);若为0,表示接收或发送数据长度为Data_leng。

Da_Bl(Data_Block)[20:27]:该数据表示ARM请求DSPx接收或发送Data_Block个Data_leng K或Data_leng数据块。

Da_Ch(Data_Result)[7:18]:ARM 请求 DSPx接收或发送的算法代码中间运行结果或最终结果,此数据段与Data_Leng共用。

In_Pr(Interrupt_Priority)[27:30]:设置 DSP的中断优先权。

Ot_Use(DSP_State)[31:34]:DSP状态标志信息。

Pa_Ch(Parity_Check)[35]:奇偶校验位。 设 SUM,若为奇数,则 Parity_Check=1;否则为 0。

Ot_Use(Other_Use)[36:47]:用户自定义数据段。

(2)数据通信主要流程

首先,FPGA接收到ARM[1:3]处理器的请求信号,然后根据Data[0:34]计算出校验数据SUM与Parity_Check[35]比较,若不等,则FPGA向ARM处理器重新发请求信号;若相等、且 DSPx为空闲状态时,则FPGA由Send/Receive向DSPx发送接收或发送数据请求,并将采集到的图像数据传输给DSPx,同时使能对应的FIFO数据通道;DSPx根据收到的数据信息,同样计算出校验数据,若与Parity_Check相等,则根据Send/Receive标志位,采用EDMA方式向EMIF口接收或发送Data_Block*Data_leng(或 Data_Block*Data_leng K)数据。 如果 FPGA同时接收到2个或2个以上的DSPx数据传输请求信号,则FPGA根据Interrupt_Priority端口数据判其执行的先后顺序。

6 系统的性能分析[7]

影响系统性能的主要因素有:ARM处理器协调工作的响应速度、DSP处理数据的速度、数据在多处理器之间的传输速度。前两个因素主要由处理的主频和处理能力决定,因此不做测试。数据在处理器之间的传输速度则是本设计的主要部分之一,而数据传输带宽和数据传输延迟是衡量数据传输速度的重要指标。

表1 传输不同大小数据时测得的平均延迟时间值

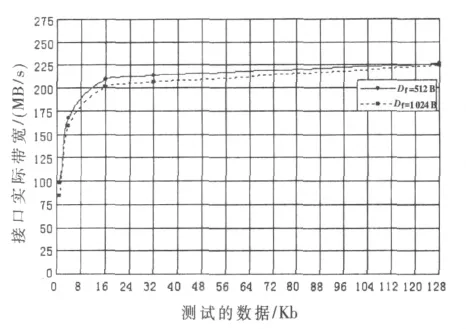

若系统中DSP读写FIFO的带宽为B(单位时间内DSP间的数据传输量),则:

其中,f=133 MHz是 FPGA内部软FIFO的读写时钟;w=32 bit是软FIFO数据总线宽度。本设计配置Nsetup=Nstrobe=1,Nhold=0,因此 B的理论值为 266 Mb/s。 但 DSP间数据传输的实际带宽主要受握手时间τhandshake、写FIFO到半满时间 τfifo_hf、响应中断启动读写操作时间 τgpio_interr、接收数据时间 τdata_receive四个延迟时间影响。其中,τhandshake、τgpio_interr由系统时钟决定,因此本文假设该值为固定的,而τfifo_hf是由于使用FIFO缓存数据引入的额外时间。FIFO的深度越长,τfifo_hf越大,则实际带宽 Bf就越小;反之则越大。

为了保证DSP间正确地数据通信,则要求DSPx开始从FIFO读取数据时,ARM还没有写满FIFO,即 τfifo_hf>τfgpio_interr。表示 FIFO 深度,可得

表1是ARM处理器分别与DSP1~DSP4传输不同大小数据时测得的平均延迟时间,图9是根据测试数据绘出的实际带宽Bf曲线。可以看出,随着传输的数据增大,Bf逐渐逼近B的266 MB/s的理论值。

图9 根据表2绘出的实际带宽曲线

本文基于 ARM、FPGA、多DSP设计的实时图像信号处理系统,使用FPGA芯片设计的一种高速数据传输网络互联结构,使得该系统的数据通信能力和DSP的运算能力能很好地匹配;通过数据传输控制总线,使得数据传输十分灵活;利用S3C6410对图像数据传输的调度,图像数据处理任务的分配,图像保存、显示、网络传输;利用4个TMS320C6416T对图像做算法处理。经测试,算法代码在单DSP(TMS320C6416T 1 GHz)平台下其处理时间小于0.2 s,而在本文平台下其处理时间小于40 ms,可以满足实时要求。另外,该系统可广泛适用于其他图像处理、电子对抗、雷达信号处理等各个领域。

[1]曹理发.尹勇.刘恒辉,等.基于 ARM和 DSP的视频监控系统设计与实现[J].电子器件,2009,32(1).

[2]Cyclonce Inc.Cyclone II device handbook.2005.

[3]龙再川,赵凯生,洪明坚,等.ARM系统中 DMA方式在数据采集中的应用[J].国外电子元器件,2007(2).

[4]Texas Instruments Incorporated.TMS320C6414,TMS320C6415,TMS320C6416FIXED-Point digital signal processor,2007.

[5]李方慧,王飞,何佩琨.TMS320C6000系列 DSPs原理与应用(第二版)[M].北京:电子工业出版社,2005.

[6]Texas Instruments Incorporated.TMS320C6000 EMIF to external FIFO interface.1999.

[7]周委,陈思平,赵文龙,等.基于 DSP EMIF口、FPGA设计并实现的多DSP嵌入式系统[J].电子技术应用,2008,34(12):6-8.