嵌入式闪存中浮栅多晶硅CMP制程的研究与改善

2011-07-02李冠华黄其煜

李冠华,黄其煜

(上海交通大学,上海 200240)

1 引言

化学机械研磨(Chemical Mechanical Polishing,CMP)技术可以有效地兼顾加工表面的全局和局部平整度。目前,CMP技术已成为在集成电路制造中最广泛使用的惟一的全局平坦化技术。随着CMP技术的日益发展和闪存特征尺寸的越来越小以及对多晶硅表面形态及前后层次间套准要求的提高,这一技术也被用于嵌入式闪存产品中浮动栅多晶硅的平坦化。嵌入式闪存集成了逻辑、存储等模块,存储单元结构复杂,工艺制作步骤多、难度大,尤其是浮动栅多晶硅的制作,因其质地软,研磨速度快,不易控制,再加上浮动栅多晶硅(Floating Gate poly)厚度及表面形态对器件的电性参数及后续工艺影响较大,因此怎样得到一个稳定的、厚度均匀及表面形态佳的浮动栅多晶硅显得至关重要。

在嵌入式闪存工艺开发过程中发现,浮动栅CMP后,在面积较大的STI 区域有Poly残余现象产生,如图1中位置A;同时在面积较大或密度较高的AA(有源区)区域颜色也不均匀(凹陷导致的poly厚度不均造成的),如图1中位置B和C。在后续的浮动栅刻蚀之后,在AB位置仍可能有多晶硅Poly的残留,导致电路短路,在C位置有源区出现刻蚀斑,衬底就会被破坏,导致漏电等电性失效,见图2。由于外围电路和逻辑区(Peripheral)区域内的有源区(AA)和浅沟槽隔离 (STI)面积大小不一且形状不规则,因此这两种缺陷更容易在外围电路(peripheral)区域产生。

图1 FGCMP之后的形貌

图2 FG Etch之后的形貌

2 缺陷形成原因分析及验证

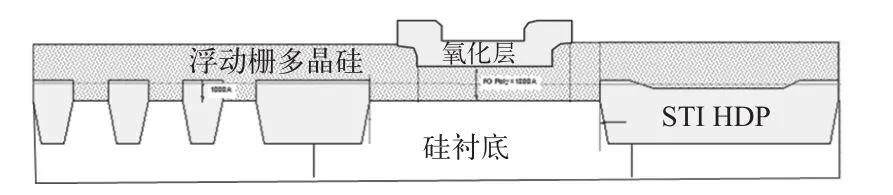

在STI CMP后,面积大的STI上的碟形凹陷(Dishing)较大,浮动栅多晶硅沉积后,也就意味着STI中间区域上的多晶硅较STI边缘及其他区域低,FG CMP难以将其研磨干净,而AA面积较大,FG poly在CMP就会产生大的Poly凹陷 ,如图3所示。

为了从根源上解决问题,首先分别对STI 宽度与凹陷程度及poly残余的关系和不同AA面积与poly凹陷程度的关系进行了研究。

图3 缺陷产生原因分析示意图

2.1 较大面积STI上的多晶硅残余形成原因分析

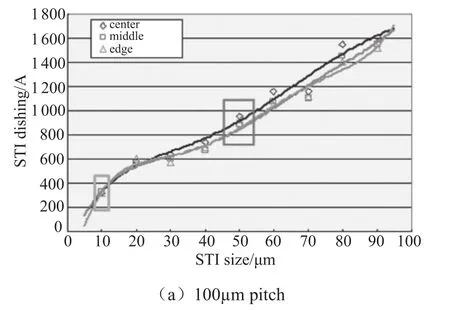

利用不同宽度和50% AA密度的STI测试图形,在STI CMP 后对这些面积和形态不同的STI上的碟形凹陷(Dishing)进行量测。从试验结果可知:STI碟形凹陷程度随着STI宽度的增加而增加;除STI宽度对碟形凹陷(Dishing)的大小影响之外,有源区(AA)的密度也是一个重要影响因素。同样的STI宽度,不同的有源区密度,其碟形凹陷程度也不一样,如图4中STI宽度同为20μm的情况下,20% AA密度上的凹陷为55nm,而50% AA密度上凹陷仅为36nm。浮动栅多晶硅研磨后,对不同宽度和50%AA密度上的STI上的多晶硅残余进行对比,如图5所示:在100μm pitch下和50% AA密度下,图形上的多晶硅残余数量随STI宽度的增加而增多。通过对比多晶硅残余与STI凹陷的数据,STI凹陷小于45nm时,在多晶硅CMP后就不会有多晶硅残余产生。

图4 不同宽度和50% AA密度上的STI与碟形凹间的关系

图5 STI宽度与多晶硅残留的关系

2.2 有源区上多晶硅凹陷的成因分析

在逻辑及外围电路(peripheral)区选择一块具有代表性的区域,有不同面积及不同密度的有源区(AA),图6为浮动栅CMP后外围电路区域不同AA上的多晶硅形貌。位置1:25μm×25μm,位置2:80μm×25μm,位置3:25μm×200μm,位置4:50μm×50μm,位置5:60μm×30μm,以及140μm×140μm的OCD(Optics CD)量测pad(主要监测Flash cell区域多晶硅的厚度)。在不同的研磨时间(从30s到50s,依次增加5s)下进行研磨,对该区域内七个不同面积大小的有源区上的浮动栅多晶硅分别进行测量,然后对其上的多晶硅厚度情况进行分析,这里测量得到的多晶硅厚度是图形中心位置的厚度,由于图形边缘的多晶硅高度是由AA 蚀刻时的阻挡层SiN厚度来确定的,图形边缘的多晶硅厚度可默认为是相同的,图形中心位置的多晶硅厚度可以侧面得到多晶硅的凹陷。具体数据如图7所示,从图上可以看出:

(1)各个不同面积有源区上的多晶硅厚度随着研磨时间的增加而减少。除OCD测量图形外,其余各区域上的多晶硅厚度随着研磨时间增加而减少的趋势基本一致。

(2)在从30s到50s的各种研磨时间条件下,有源区密度较高(如图6中位置4和5)和有源区面积大的图形(如图6中位置6)上的多晶硅厚度较密度低(如图6中位置2)和面积小(如图6中位置1)的有源区上的多晶硅薄。

图6 浮动栅CMP后外围电路区多晶硅形貌

图7 不同AA上的poly厚度与研磨时间的关系

(3)在从30s到50s的各种研磨时间条件下,OCD图形上的多晶硅厚度都较其他图形上的多晶硅厚,且有随着研磨时间增加而增大的趋势。

(4)高密度且面积大的活动区多晶硅厚度随着时间的增加减少较快,在浮动栅刻蚀之后就容易出现有源区的pitting(蚀刻斑)现象,从而导致器件漏电过大而失效。

3 缺陷改善及验证

3.1 多晶硅残余改善方案及试验验证

STI上的多晶硅残余,其主要是由于STI CMP后STI HDP凹陷过多而引起的,因此需要优化STI CMP的工艺程式(Process recipe)以减少 STI HDP的碟形凹陷程度。STI CMP时使用的是终点检测(End Point Detect)模式,也就是当研磨到阻挡层SiN后,检测装置就会探测到SiN的信号,为避免SiN上的氧化层没有被研磨干净而导致后续SiN去除不干净,通常会在探测到SiN后再过研磨(over polish)一段时间,由于STI CMP中SiN对HDP 氧化层的选择比较高,过研磨的时间长短决定着STI凹陷程度。因此通过对过研磨(over polish)时间的优化来减少STI HDP的凹陷应该是一种有效的方式。

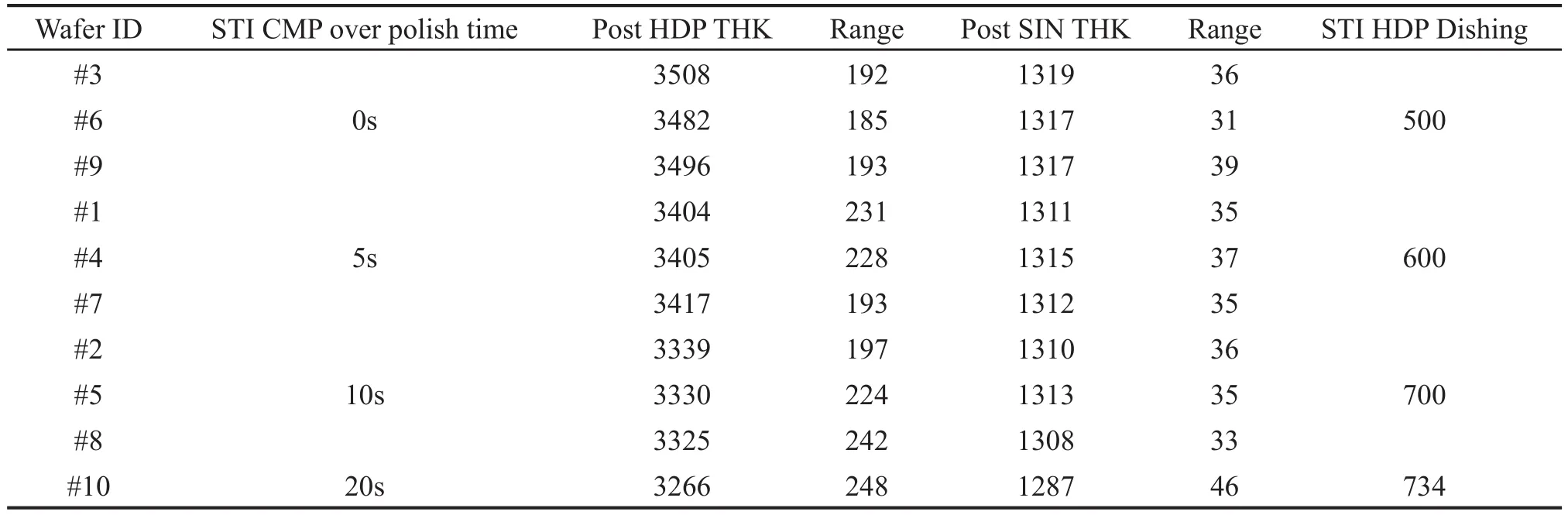

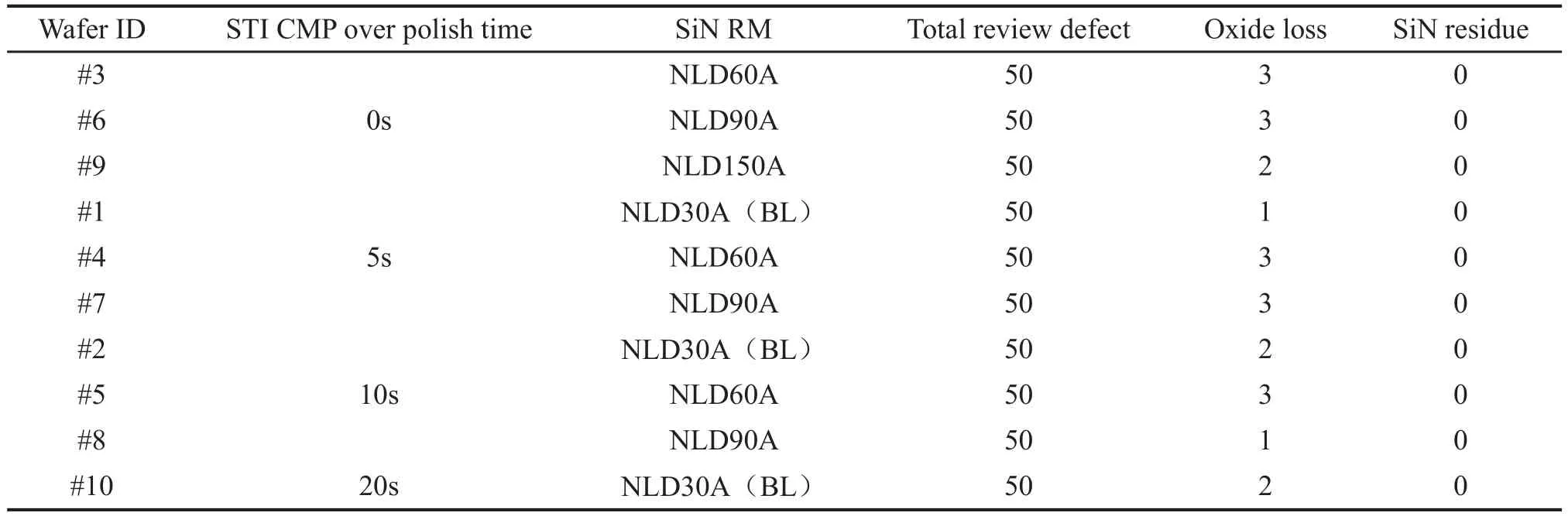

实验方案如下:保留原来STI CMP工艺程式中的设定和消耗材料,如Down Force、研磨液及研磨垫。对STI CMP在不同的过研磨时间(0s、5s、10s、20s)下做实验,为排除工艺或其他不确定因素造成的影响,每种研磨条件下取不相邻的三片进行试验验证。然后测量研磨后STI HDP 氧化层凹陷厚度及均匀性,阻挡层氮化硅厚度及均匀性并进行对比。从表1中明显可以看出,不同的过研磨时间对STI HDP氧化层和氮化硅的厚度及均匀性影响不大, 但对STI HDP凹陷影响特别明显,从过研磨20s下的73.4nm减少到0s过研磨下的50nm。因此从减少凹陷的角度来看,STI CMP过研磨时间为0s(没有过研磨时间)时,凹陷为最小。但氮化硅上的氧化层会因研磨不干净而影响氮化硅的去除,如果氮化硅去除步骤还沿用原来的工艺程式的话,氮化硅就有可能去除不干净。氮化硅去除程式增加氧化层去除时间以确保无氮化硅残余存在。分别用STI CMP不同过研磨时间的硅片做不同氮化硅去除厚度(NLD30A/60A/90A/150A)的试验,Defect扫描结果显示这十片硅片均无发现氮化硅残余,见表2。这足以说明氮化硅去除的工艺窗口比较大。

表1 不同STICMP 过研磨时间下SiN /HDP厚度、均匀性及HDP凹陷对比

表2 不同过研磨时间和SiN Removal下Defect情况对比

3.2 多晶硅CMP凹陷问题改善方案及试验验证

对于面积大或密度高的有源区(AA)上的浮动栅多晶硅的蝶形凹陷问题,对浮动栅CMP之前的形貌进行了检查和分析。如图8所示,在浮动栅多晶硅沉积之后,面积较大的有源区(图8中位置B)上的堆叠层高度要低于存储单元(位置A)和大面积STI(位置C)区。研磨过程中,位置A和C上的多晶硅先会被研磨到,且研磨速度较快,当A和C处 STI上的多晶硅被研磨到STI HDP氧化层上时,由于氧化层的研磨比多晶硅慢,此时B处的研磨速度反而比A和C处大。再加上大面积STI的HDP凹陷问题,多晶硅CMP必须给出一定的过研磨量,否则大面积上就会产生多晶硅残余。与此同时,面积较大的有源区上的多晶硅凹陷就会比较大,浮动栅多晶硅蚀刻后这一区域就出现蚀刻斑(Pitting)。

鉴于以上情形,在面积大的有源区上的多晶硅上沉积一层氧化层来作为浮动栅多晶硅研磨过程中的阻挡层或缓冲层,应该是一种减少大面积有源区上的多晶硅凹陷的有效方法。具体方案如下:浮动栅多晶硅沉积完,紧接着沉积一层缓冲氧化层,然后通过光刻和蚀刻将面积较大有源区(>5μm×5μm)以外其他区域上的氧化层去除,如图9所示。

图8 浮动栅多晶硅CMP前不同区域的堆叠层SEM图片

图9 浮动栅多晶硅CMP新方案示意图

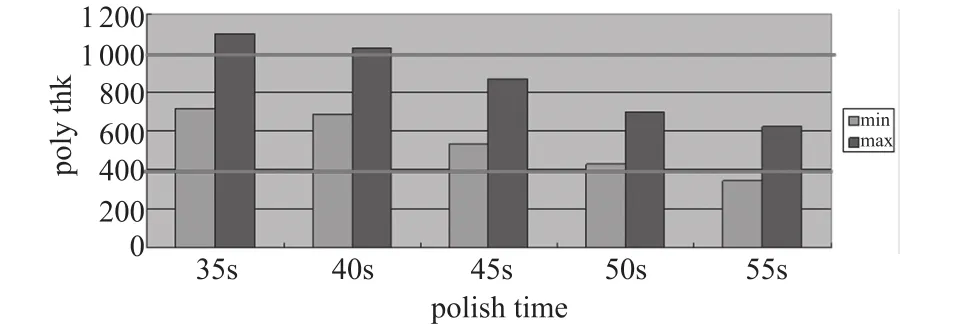

新方案实施及结果验证:在面积大于或等于5μm×5μm的有源区上的多晶硅沉积30nm的缓冲氧化层,然后用不同的FG CMP研磨时间试验。基于以往经验及估算结果,当Monitor pad检测图形(主要监测外围电路及逻辑区域上的多晶硅厚度)上多晶硅厚度大于100nm,后续的浮动栅蚀刻就难以将其蚀刻干净,会留下多晶硅残余;当多晶硅小于40nm时,浮动栅蚀刻时就破坏到硅衬底,留下蚀刻斑。从试验结果来看,只有45s和50s条件下多晶硅厚度满足要求,Monitor pad检测图形上最大值和最小值介于40nm~100nm之间(如图10所示)。在蚀刻之后Monitor pad检测图形上没有出现刻蚀斑(pitting)问题,与最初的工艺方案相比,浮动栅多晶硅研磨后的性能有了很大的改进。

这里只是在沉积30nm缓冲氧化层的情况下,做了不同研磨时间的试验。但沉积不同厚度的缓冲氧化层对浮动栅FG性能也应该会有较大的影响,紧接着做沉积不同厚度的缓冲氧化层的试验,通过在线测量和形貌SEM切片以及浮动栅蚀刻后在线缺陷扫描来验证。具体试验条件及结果见表3,从试验结果来看,在浮动栅CMP 50s条件下,浮动栅多晶硅CMP后,OCD pad(用于检测Flash cell上的多晶硅厚度)检测图形上的多晶硅厚度基本上没有变化(见图11);但Monitor pad上的多晶硅厚度随着沉积缓冲氧化层厚度的增加而增加,变化较为明显;在线量测的厚度和实际的切片结果也差不多,具体见图12,从中可以看出缓冲氧化层为35nm时为最佳条件。将这些硅片放到浮动栅蚀刻后继续对其缺陷情况进行检查和验证,缓冲氧化层厚度为35nm、40nm、45nm的情况下,都没有出现有源区的蚀刻斑。

图10 新方案下不同研磨时间下的多晶硅厚度对比

表3 新方案中试验条件及不同缓冲氧化层条件下的多晶硅厚度对比

图11 新方案不同缓冲氧化层厚度下的多晶硅厚度对比

图12 新方案不同缓冲氧化层厚度下的多晶硅厚度对比

图13 新旧方案浮动栅蚀刻后的缺陷情况对比

从图13新旧方案浮动栅蚀刻后的缺陷情况对比结果来看,STI CMP优化程式和FG CMP使用新方案后,这些硅片除#10上发现一颗多晶硅残余外,其余硅片上均没有发现大面积STI上的多晶硅残余和大面积及密度高的有源区上有蚀刻斑产生,这两种缺陷得到了很大的改善。

4 结论

本文对嵌入式闪存开发过程中出现的多晶硅残余及多晶硅凹陷问题进行了研究和分析,并通过实验验证了这两种缺陷出现的根源。以此实验结果,针对性地分别通过减少STI CMP后的凹陷及在大面积上的多晶硅沉积缓冲氧化层加以保护,使得这两种缺陷得到明显的改善。