带有小数补偿的低频数控振荡器及其基于FPGA的实现

2011-06-30朱峰李孝辉王国永

朱峰,李孝辉,王国永

带有小数补偿的低频数控振荡器及其基于FPGA的实现

朱峰1,2,3,李孝辉1,2,王国永1,2,3

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院精密导航定位与定时技术重点实验室,西安 710600;3. 中国科学院研究生院,北京 100039)

在分析数控振荡器(NCO)工作原理的基础上,以低频信号为例,研究了影响NCO性能的几个因素。结合杂散特性,着重讨论了频率控制字误差对输出频率带来的影响,提出在相位累加器中加入小数部分补偿,以使降低信号频率门限值和提高输出的准确性。最后采用FPGA(现场可编程门阵列)实现了带有小数补偿的NCO,在兼顾硬件资源的同时优化了系统性能,另外通过仿真验证了这种方法的可行性。

数控振荡器(NCO);查找表;杂散特性;频率控制字;现场可编程门阵列(FPGA)

数控振荡器(NCO)的目标就是产生一个理想的正弦波,更确切地说是产生一定范围内频率可变的正弦波。NCO是直接数字频率合成不可缺少的模块,在软件无线电中起着重要的作用,同时也是决定其性能的主要因素之一。

基于FPGA(现场可编程门阵列)的NCO实现受算法和硬件资源限制,杂散特性成为影响其性能的主要因素,这一特性直接关系着输出信号的准确性。其中,FPGA对频率控制字的取整累加导致输出低频信号时受杂散特性影响较大。因此,需要对舍去的频率控制字小数部分进行补偿,减小相位累加值误差,降低输出频率门限值并提高输出信号的准确性。

1 基于查找表的NCO工作原理

为了缩短转换时间,便于对频率和相位进行控制,NCO通常采用查找表方式产生可数控的周期信号,即事先对正弦波幅值进行量化,以相位角度作为地址把对应的量化值存储在表中,然后根据NCO相位累加值(作为查找地址)读取当前时刻的表中对应的正弦波幅值,从而产生所需频率的正弦波[1]。

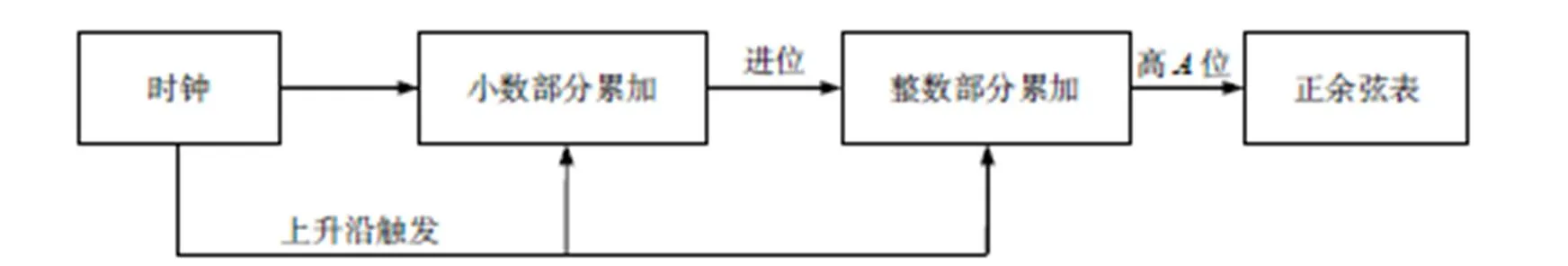

如图1所示,NCO主要由相位累加器、相位寄存器和正余弦查找表组成。位相位累加器在每一个时钟上升沿对输入频率控制字进行累加,相位寄存器接收累加的结果,一方面反馈给累加器作为下一时钟的数据输入,另一方面作为查找地址输出相应的正弦值。频率控制字与系统工作时钟频率,NCO输出信号频率,相位累加器位数之间的关系可表达为

由式(1)可见,NCO通过调整控制输出信号的频率,当相位寄存器中累加值超过时,即溢出一个周期信号。

2 NCO低频信号误差分析

当系统工作时钟给定时,基于查找表的NCO输出信号频率误差主要受相位累加器位数和查找表位数的影响。下面对基于查找表的NCO输出信号频率误差的分析中,系统工作时钟取10 MHz。

2.1 杂散特性分析

基于查找表方式实现的NCO,杂散特性成为影响其性能的主要因素。从对输出信号的影响来看,杂散特性主要指相位截断误差[2]。相位截断误差是实际应用中位相位累加器只有高位被用来寻址所引起的,通常的取值与硬件实现所允许的查找深度有关,一般最大能取到16。

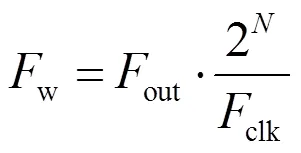

对于采用FPGA、基于查找表方式实现NCO的情况中,由于FPGA在此实际应用中不支持小数,所以对频率控制字一般都取整进行累加。但是当输出信号频率较低时,相位截断误差使被舍去的频率控制字小数部分引起的误差增大,会导致相位累加值减小,影响输出信号的准确性。这里对基于查找表方式实现的低频数控振荡器中不受相位截断误差影响的输出信号最低频率值进行了分析,推出了累加器位数和查找表位数与不受影响的最低输出信号频率值(即输出信号频率门限值)的关系,如图2(a)和图2(b)所示。

图2 杂散特性分析

图2(a)所示为查找表位数=16时,输出信号频率门限值与相位累加器位数之间的关系;图2(b)为相位累加器位数=32时,输出信号频率门限值与查找表位数之间的关系。可见,对频率控制字取整累加时,输出信号频率门限值随和的大小而变化。当和一定时,若想要输出更低频率的信号,需要对频率控制字进行小数补偿。

2.2 频率控制字误差分析

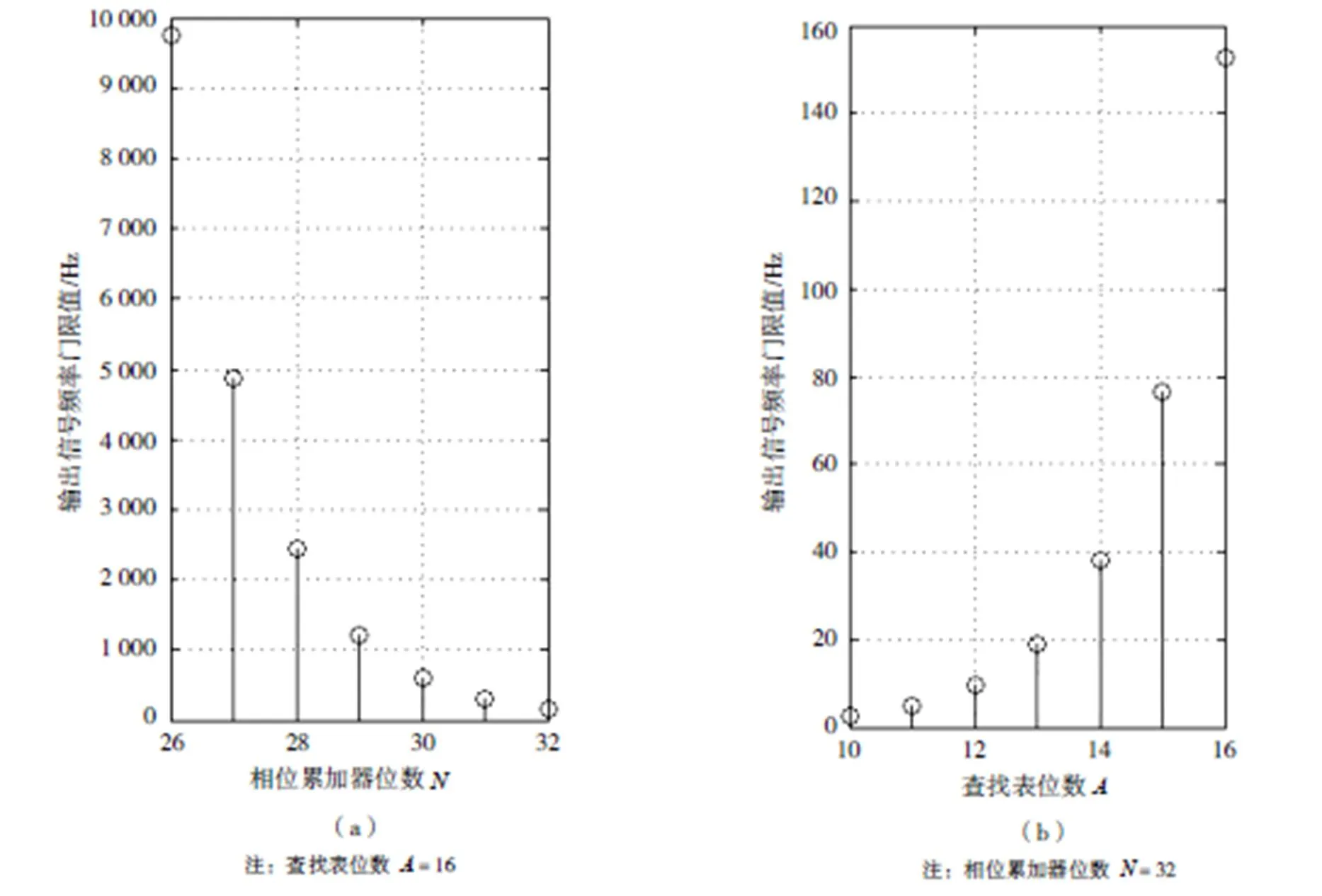

当输出较低频率的信号时,并非所有频率的信号都要进行小数补偿,而与频率控制字小数部分的大小有关。为了更直观地反应频率控制字误差对输出信号的影响,对周期信号能舍去的频率控制字小数部分的最大值(下面简称“小数部分最大值”)进行了分析。当相位累加器位数和查找表位数一定时(=32,=16),推出了10MHz~10Hz频率范围内频率与“小数部分最大值”之间的关系,如图3所示(图3横坐标所示的“周期信号采样点数”一一对应于10 MHz~10 Hz频率范围的频率)。

以输出信号频率10 Hz为例,其对应的周期采样点数为106,由图3可知“小数部分最大值”为0.1,但10 Hz对应的频率控制字为4 294.967296,小数部分大于0.1,因此不能舍去其小数部分,需要进行补偿累加。

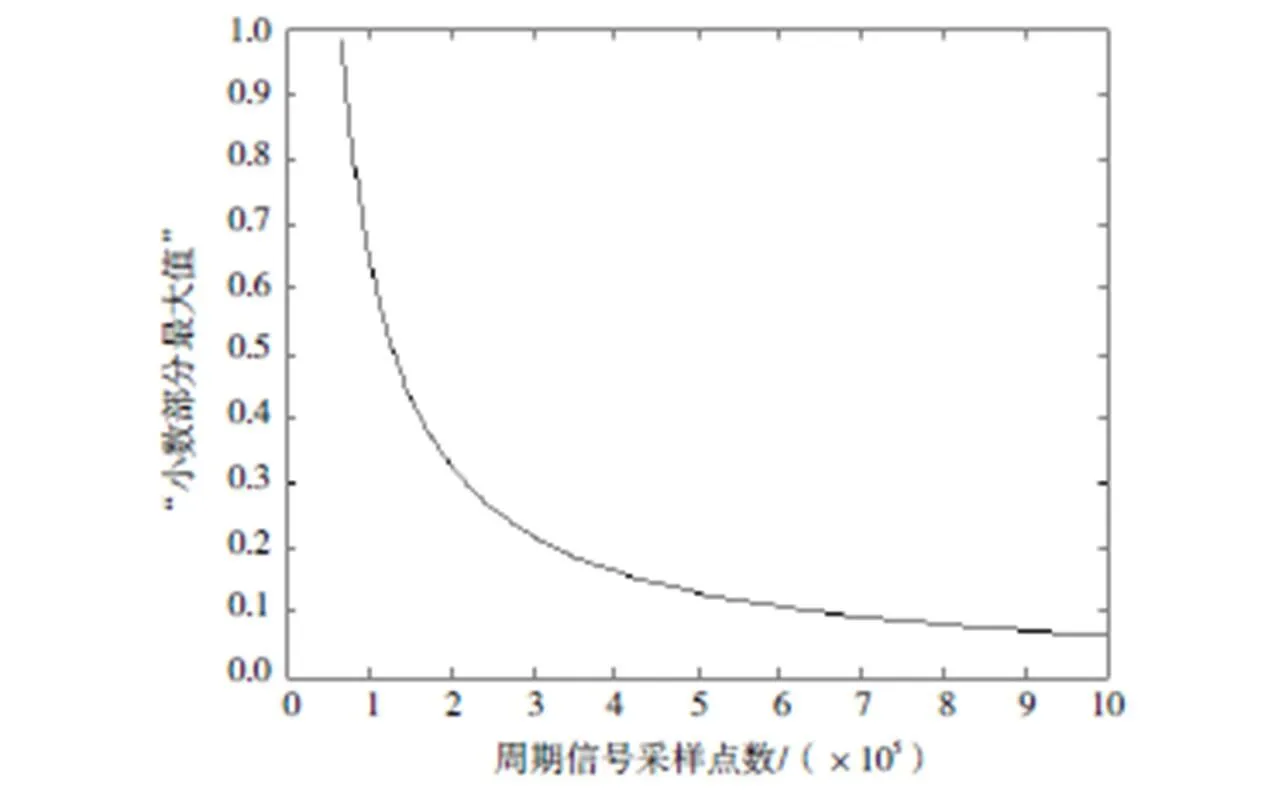

相位累加器加入小数补偿后,对于输出10 Hz周期信号而言,反映到截取位数为16的相位累加器中会带来数值为15的相位补偿,于是查找深度也相应增加了。将基于查找表方式实现的NCO输出信号的幅值16比特量化,对比小数补偿前后的变化,得到频率控制字加入小数部分补偿前后的变化与对应的输出信号幅度变化之间的关系,如图4所示。

图3 “小数部分最大值”与周期信号采样点数(与频率相对应)的关系

图4 小数补偿前后的变化

为了说明小数补偿对输出频率准确性的提高,在1~100Hz范围中随机选取5个频点进行分析,得到对每个频点而言加入小数补偿前后的输出频率值,如表1所示。

表1 小数补偿前后的输出频率值 Hz

3 采用FPGA实现带有小数补偿的NCO

调用FPGA(Xilinx xc4vsx55)中的IP核作为正余弦查找表[3],以系统工作时钟为触发,对频率控制字整数和小数部分分别进行累加,按照小数溢出整数进位的原则实现小数部分补偿,最后把整数部分累加值的高位作为查找表地址,输出相应频率值的信号,流程图如图5所示。

图5 FPGA流程图

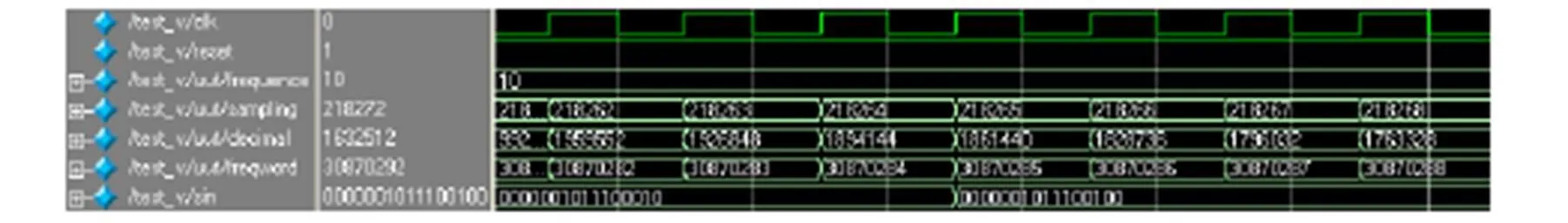

以输出10 Hz信号为例,实验采用Verilog在Xilinx 11.1环境下进行建模并综合,最后使用Modelsim 6.5进行了仿真,图6为NCO加入小数补偿后在FPGA中的仿真结果[5]。图6中,“sampling”表示系统工作时钟对应的采样点数,“decimal”为频率控制字小数部分累加值,这里按小数位数扩大了106倍,因此超过107就对“freqword”(频率控制字整数部分累加值)加1,高16位送入正余弦查找表输出正弦信号“sin”。

图6 FPGA仿真结果

4 结论

通过FPGA查找表方式输出低频信号时,不同的查找深度对应不同的频率门限值,不同频率的信号受杂散特性的影响也不同。本文在考虑FPGA硬件资源的基础上,对低频信号而言,在进行相位累加时加入了小数补偿,提高了输出信号的准确性。为了进一步减小低频输出信号频率值的误差,还可通过提高时钟采样率[4]和增加相位累加器位数等方式来提高输出信号的准确性。

[1] 王瑛, 曹闹昌, 向新, 等. DDS合成信号的频谱杂散性分析[J]. 现代电子技术, 2010, 6(3): 140-142.

[2] 俞麒. 基于改进算法的NCO杂散抑制实现[J]. 中国科技信息, 2009, 2(5): 37-41.

[3] 褚振勇, 田红心. FPGA设计及应用[M]. 西安: 西安电子科技大学出版社, 2002.

[4] JANISZEWSKI I, HOPPE B, MEUTH H. Numerically controlled oscillators with hybrid function generators[C] // IEEE Trans Ferroelectrics and Frequency Control, 2002, 49(10): 995-1004.

[5] 王朝刚, 卢晓春. UWB中Viterbi译码器的FPGA设计与实现[J]. 时间频率学报, 2009, 32(1): 63-69.

Low-frequency numerically controlled oscillator with decimal compensation and realization with FPGA

ZHU Feng1,2,3, LI Xiao-hui1,2, WANG Guo-yong1,2,3

(1. National Time Service Center, Chinese Academy of Sciences, Xi′an 710600, China; 2. Key Laboratory of Precision Navigation and Timing Technology, National Time Service Center, Chinese Academy of Sciences, Xi′an 710600, China; 3. Graduate University of the Chinese Academy of Sciences, Beijing 100039, China)

Bytaking low frequency signal as example, several factors of affecting the performance of the NCO (numerically controlled oscillator) are studied on the basis of analysing the principle of NCO. The influence of frequency control word error on the output frequency is discussed emphatically in the light of spurious characteristic, and it is presented to add the decimal compensation in the phase accumulator for reducing the threshold and improving the accuracy of the output signal. Finally an NCO with decimal compensation has been realized based on FPGA(field programmable gate array), which not only takes account of the hardware source, but also optimizes the system performance. The simulation has verified the feasibility of this method.

numerically controlled oscillator(NCO); look-up table; spurious characteristic; frequency control word; field programmable gate array(FPGA)

TN752

A

1674-0637(2011)02-0112-05

2011-01-07

国家自然科学基金重点资助项目(11033004);中国科学院“西部之光”人才培养计划资助项目(Y109YR2701)

朱峰,男,硕士,主要从事时间频率测量与控制方面的研究。