基于FPGA的多功能雷达信号处理板硬件系统设计

2011-06-28邓志清

杨 建,邓志清,高 峰

(1.解放军镇江船艇学院,镇江212003;2.空军驻沈阳军事代表处,沈阳110000)

0 引 言

雷达是现代高科技的集合体,而雷达信号处理作为现代雷达系统的重要组成部分,对雷达的技、战术性能起着关键的作用。为了不同的应用,雷达体制也分为很多类,相应的雷达信号处理系统也有较大差异,有些甚至有全局性的差异,因此给雷达信号处理系统的研制带来了巨大的挑战,并且对系统的故障检测和维护带来很多不利的影响。一般来说,雷达信号处理系统的功能主要包括:雷达全机定时、脉冲压缩、求权、恒虚警、积累检测、频率管理、通信接口、距离方位门(RAG)图,以及完成抑制杂波和干扰提取目标的处理等等[1]。所以雷达信号处理分系统一般由若干不同功能的电路板组成,以实现信号处理分系统所需的各种功能。

在最初设计的雷达信号处理系统中,采用的多个电路板几乎各不相同,在研制中需要多个设计人员共同研究,另外,还要有专业人员进行不同电路板的布线、调试等工作。因此,以往雷达信号处理板具有研制周期很长、可靠性差、不便于维修等问题[2]。近年来,随着雷达信号处理技术的成熟和高性能集成电路迅猛发展,尤其超大容量现场可编程门阵列(FPGA)技术日新月异,其现场可编程的优点使其应用的范围更加宽广,并且以往很多专用芯片完成的功能也能在FPGA中得以实现,这为设计一种多功能雷达信号处理板提供了可能。本文就以FPGA为核心,外加一系列电路来完成雷达信号处理的不同功能。设计的电路板是完全可编程的,不但可以用在不同的雷达上,而且可以实现雷达信号处理的不同功能。1部雷达信号处理机的全部功能只需几个雷达信号处理板就可实现。

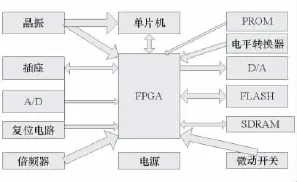

1 硬件系统设计框图

通过对雷达信号处理板的详细研究,依据雷达信号处理的需求,设计了1个以FPGA为核心处理器件的多功能雷达信号处理板。该电路板以1片大容量、高性能的FPGA作为雷达信号处理板的核心器件,用同步动态随机存储器(SDRAM)存储外部高速实时数据,用FLASH存储一些断电不能丢失的数据,单片机电路的设计使FPGA的功能进一步完善,对雷达信号处理机起到非实时的监控。为了使雷达信号处理的结果得以显示和各个元器件的正常运行,添加了显示和控制器件、不同电平之间的相互转换器件,最后,考虑不同信号处理板之间的通信和外部电源的供给,设计了插座。其框图如图1所示。

图1 多功能雷达信号处理板硬件框图

2 FPGA芯片电路的设计

FPGA电路的设计首先需要选择合适的芯片,FPGA芯片的选择一般要考虑三个方面:一是逻辑资源的多少;二是芯片外部I/O引脚的多少,I/O引脚越多,设计的灵活性就越强,可操作性就越强;三是价格因素。FPGA芯片是在仿真的基础上选择出来的,在雷达信号处理中,脉冲压缩滤波器是最占用资源的,只要能够满足脉压处理,其它功能都能实现。因此,对256阶脉冲压缩滤波器进行仿真,其占用资源大概为45 000个逻辑单元。通过综合考虑,选择了ALTERA公司CycloneII系列的1片EP2C70,该芯片价位低、性能高,作为通用信号处理模块的主处理器件完成了高速实时雷达信号处理的各种运算和繁琐的时序处理。ALTERA的EP2C70内部含有68 416个逻辑单元,150个18×18bit的乘法模块、250个 M4K存储器块,总存储容量可达1 152 000bit,4个锁相环(PLL)可以完成分频倍频和相移,有622个可用输入/输出(I/O)管脚。

FPGA的硬件设计主要涉及2个方面:(1)配置电路,是采用主动串行、被动串行还是联合测试行为组织测试(JTAG)配置方式,因为FPGA是基于SRAM结构,每次芯片重启时都需要重新下载程序,之后FPGA才能进行正常的工作;(2)FPGA与外围芯片的相互连接,互连的好坏直接关系到雷达信号处理板的功能。EP2C70配置电路采用的是主动串行(AS)和JTAG两种配置方式,而没有采用被动串行(PS)配置的原因是由于它会使设计的复杂度更高,控制起来不方便,有这两种配置方式在实际应用中已经足够。在程序编写期间或调试过程中,利用JTAG模式加载程序,这方便了程序的修改、优化。程序修改完善后,将程序下载到可编程只读存储器(PROM),以后每次重启时都自动从PROM中加载程序,这使整个过程的可操作性和可靠性得到很大提高。

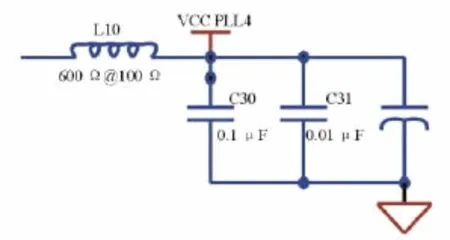

在互连电路设计过程中,有2个问题需要重点考虑:一是时钟信号的接入必须要慎重;二是着重考虑芯片之间的兼容问题。由于现在的雷达大都是全相参雷达,也就是雷达整机用1个频率源,其它频率都是通过频率源进行分频、倍频得到的,因此时钟信号的接入要充分利用FPGA的优点。FPGA中有专门时钟管脚,通过时钟管脚接入的时钟信号到其它各个管脚的时延基本一致,且抖动较小,这个优点对雷达信号处理非常有利。这样,从正射极耦合逻辑电平(PECL)器件和电平转换器件过来的信号都接到时钟管脚上。另外,与外围芯片互连时,必须注意兼容问题,由于本设计的外围I/O电平都是3.3V,只需要I/O电平一致即可。FPGA的PLL供电必须单独考虑,由于它是用模拟电路来实现的,对噪声比较敏感,所以在设计时,一定要充分考虑对电源的滤波和去耦。其电路图如图2所示。

3 存储电路的设计

图2 PLL模拟供电电路

存储电路需要保存断电易失数据和完成实时数据的存储,根据这个需求,需要由两种不同的存储器来组成。在设计时,采用FLASH和SDRAM相结合的存储方案,FLASH存储一些断电需要保存的数据,而SDRAM完成实时数据的存储。存储器都涉及存储容量大小的问题,一定要根据实际需求来设定,不要过大,同时不能小于所需容量,通过估算,选择FLASH存储器3片,型号为:SST39VF3201-7 0-4C-EK,每片的存储容量为3 2Mbit,3片32Mbit的FLASH足够满足雷达信号脉冲压缩处理时的匹配滤波器系数、动目标指示(MTI)处理时杂波加权系数、恒虚警率(CFAR)处理时的对数表以及一些函数求值需求。选择4片SDRAM,型号K4S641632N-LC/L75,每片存储容量为64Mbit。可以满足MTI处理时作为周期延迟器件、动态杂波图的存储和高速实时信号处理时的数据暂存等功能。

EP2C70有622个I/O管脚,使设计的灵活性大大增强,在与FLASH互联电路设计时,将FPGA的普通I/O管脚与FLASH的除电源和功能之外的管脚连接,这样,在后续的FLASH控制器程序编写时,只需要严格按照FLASH的工作时序编写相应的程序即可。另外,电源要按照正确的电压进行供给。SDRAM与EP2C70的互连电路设计基本上与FLASH一致,在此就不重复。由于EP2C70与FLASH和SDRAM互连的管脚较多,电路图设计时采用网络标号,而不用引线。

4 A/D转换和D/A转换的设计

电路板中设计模拟/数字(A/D)是因为从接收机过来的信号是模拟信号,而信号处理板处理的是数字信号,需要将接收机过来的模拟信号转变为数字信号。A/D器件性能的好坏会对后续的信号处理、数据处理和终端数据处理产生很大影响,因此在设计时必须高度重视。多功能雷达信号处理板用的是AD6640模数转换器,它是AD公司生产的12位转换器,采样速率能满足需求,功耗也不大。通过查询器件手册得知此A/D转换器所能转换的信号电平有一定的范围,而接收机信号电平有可能不满足此要求,如果不采取措施,处理结果就可能出现偏差,所以需要用一器件来完成信号幅度的调整,这时用的是运放器件,通过运放处理,信号再送入A/D转换器,就可以有效地进行转换。A/D转换器的设计要点之一就是要处理接收信号的幅度问题,其它电路的设计只要按照手册中的要求来完成即可。

信号处理的结果需要在示波器上直接显示出来,以便于设计人员和使用人员查看处理效果,因此,多功能雷达信号处理板需要数模/转换器。雷达信号处理机由10块左右的多功能雷达信号处理板组成,为了在单个多功能信号处理板和雷达信号处理机上能同时观察到信号波形显示,因此,数/模转换器需要是一个双通道器件,而AD公司有一器件为AD9767器件,它是一个高速、双通道数/模转换器,可以较好地满足设计需求,因此就选择这种芯片。模/数转换器和数/模转换器电路都是模数混合电路,在原理图和印刷电路板(PCB)设计时,必须重点考虑模拟地和数字地的分割问题,如果处理不好,会产生很大干扰。

5 单片机和电源电路设计

5.1 单片机电路设计

虽然FPGA信号处理能力比较强,但对采集到的数据处理能力较差,故需要将其采集到的数据送到其他单片机系统来实现数据的处理功能。这样,信号处理板中加入单片机,使信号处理板的功能更加完善。单片机的型号为:C8051F020,它最明显的优点是控制作用非常强。单片机设计最主要的目的是使处理板的控制更加方便、高效,通过先进的界面程序来控制整个处理板的工作,使操作人员不必掌握信号处理板的内部构造,就可以通过计算机上的图形界面对信号处理机进行非实时的控制。在硬件电路设计中,单片机有2个问题需要重视:(1)复位电路的设计,由于单片机内部的特殊功能寄存器控制各个功能部件正常工作,因此单片机工作时都需要进行复位控制,并且复位只能在外部进行;(2)由于单片机有A/D采样器,要注意模拟地和数字地的设计问题。一些参考资料中的复位电路不是太过简单就是太过复杂,由于信号处理板中有FPGA器件,所以,设计中就充分利用FPGA的优点进行复位电路的设计,先通过阻容(RC)设计一个简单的复位电路,使其通过FPGA转换,就可以控制复位时间的长短,使单片机正常复位。模拟地和数字地的设计可以参考A/D和D/A的设计。由于单片机需要调试程序,因此,设计时增添了1个JTAG口,方便单片机的控制,与FPGA互连时,只与FPGA的普通I/O接口连接,并且其自身电源和地线要单独设计。

5.2 电源设计

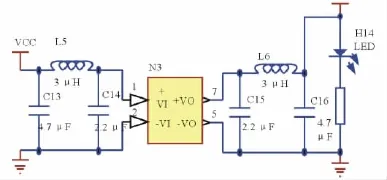

由于信号处理板是电子器件,而每个器件的正常工作都离不开电源的支撑,因此,电源也是设计中的一个难点。由于是多个元器件构成的系统,并且每个器件所需的电压标准又不一样,并且器件工作在不同频率时,功耗也不一样,同时还有模拟电源和数字电源,另外,在设计中必须充分考虑器件间的相互影响。多功能雷达信号处理板需要的电源电压类型主要有:数字电压1.2V,3.3V,模拟电压5V。如果电源选择不当,输出的电流、功率不够,会使元器件不能正常工作,严重时会损坏器件,因此选择电源时必须进行仿真和估算,并对得出的结果适当放宽,最终确定电源的选择。

电源型号确定之后,必须考虑电源的散热和滤波问题,散热在做PCB设计时予以考虑,而滤波则以并联电容加以解决。为了正常观测电源是否正常工作,则串联一个发光二极管,用以显示电源是否正常工作。下面给出一个模拟±5V电源的电路图,如图3所示。

图3 模拟+5V电路电路

6 其它电路设计

6.1 时钟电路设计

时钟和复位的设计关系到模块内的各个芯片能否协调工作,虽然现在的雷达基本上是全相参雷达,但在设计单板测试时,还必须有晶振。因此采用下列设计方案:正常工作时采用外部时钟,单板调试时采用处理板上的50M的晶振,另外还要设计1个晶振用于完成与计算机通信时的时钟,这个用44.236 8MHz晶振。单片机的复位前面已介绍,EP2C70复位电路只需要设计个复位开关电路即可。

6.2 电平转换和倍频电路设计

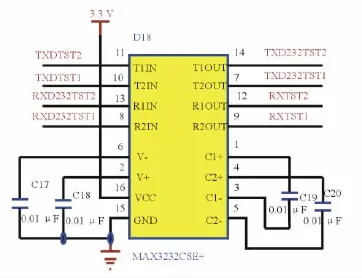

信号处理板与计算机和外围器件需要通信,由于不兼容的电平标准之间不能进行,因此,需要有电平转变装置来解决这个问题。选用MAXIM公司的MAX3232CSE+,该器件可满足2个串口通信,并与计算机连接,通过计算机进行控制。电路图如图4所示。

图4 RS-232与LVTTL电平转换电路

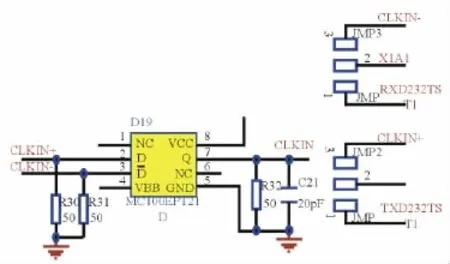

在信号处理过程中,有时接收到的信号为差分信号,因此需低电压(LV)TTL/LVCOMS转换器,用于高质量的时钟信号的处理。这里选用的转换器型号为:MC100EPT21D,通过这个器件的差分信号不仅干扰小,而且基本无抖动,这就确保了信号的质量。PECL信号是通过跳线连接到MC100EPT21D上,然后再接到EP2C70时钟管脚上,如图5所示。

图5 差分电平转换电路

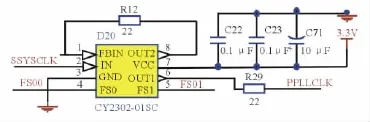

另外,还要考虑微动开关电路的设计,它主要用于状态控制。显示电路主要是用发光二极管,用作状态指示。由于EP2C70芯片有1个最低倍频值,频率如果低于这个值,锁相环是不能进行倍频工作的,为了充分利用锁相环的分频和倍频功能,需要在EP2C70处外接1个倍频器,这样,低于10MHz的时钟频率可以通过外部倍频器倍频后再送入EP2C70的时钟管脚。电路如图6所示。

图6 倍频电路

7 结束语

本文给出了多功能信号处理模块的设计框图,并对多功能雷达信号处理板的主芯片EP2C70和辅助外围芯片的选择和设计理念作了说明,解决了元器件之间的电气互联问题。

[1]何明亮,杨辉.通用雷达信号处理模块的研制和展望[J].电子工程,2006(3):21-25.

[2]王瑾,王刚.基于FPGA的通用雷达信号处理模块[J].电子工程,2005(2):15-18.