基于DDLMS算法的信道均衡器的FPGA实现

2011-06-14白勇博陈自力祁栋升

白勇博,陈自力,祁栋升

(军械工程学院,河北石家庄050003)

0 引言

在高速数字通信系统中,由于信道多径衰落效应的影响,会造成传输数据之间的符号间干扰(ISI)。严重的符号间干扰会使接收端误码率增大,甚至导致系统不能正常工作。为了克服ISI引起的失真,需要在通信系统中使用信道均衡处理技术,即在接收端添加均衡器。信道均衡器的实质是信道的逆滤波器,通过对一个未知脉冲响应的信道使用自适应滤波器操作信道输出,使得信道与自适应滤波器的级联提供理想传输媒介的良好逼近。

1 信道均衡器原理

1.1 信道均衡器

信道均衡器由滤波器结构和均衡算法组成,信道均衡的目的就是把接收序列y(n)恢复成原始数据In。均衡器通过跟踪信道C(n),使得均衡器的输出结果和原始数据之间达到匹配。理想的均衡器应该能实现F(z)=1/C(z),故均衡器又称为逆信道滤波器[2]。

目前常用的均衡器结构分为线性均衡器和非线性均衡器。线性均衡器的常见结构是线性横向滤波结构(LTE),而非线性均衡器常用的是判决反馈结构(DFE)。线性均衡器的结构简单,实现较容易,没有误码扩散的影响,因而在硬件实现中更为常用[3]。线性均衡器通过横向滤波器对输入信号进行乘加运算后与期望的信号或者是判决后的信号做差,用误差并结合对应的均衡算法去调整横向滤波器的抽头系数,进而实现处理后的信号与原始传输信号良好的逼近。这里实现的均衡器是线性横向滤波结构。

1.2 DDLMS均衡算法

均衡算法的选择是均衡器性能得以实现的关键。随着均衡技术的发展,有多种均衡算法可以使用,如LMS算法、递归最小二乘(RLS)算法、盲均衡的判决引导算法(Decision Directed)和CMA算法等。在诸多算法中,LMS算法以其计算量小和易于实现等优点而在实践中被广泛采用,这里实现的均衡器采用了判决引导算法与LMS算法的结合。DDLMS算法与LMS算法的不同点是误差信号的获取方式,LMS算法的误差来自训练序列d(n)与均衡器输出y(n)的差,而DDLMS算法的误差来自判决器输出^d(n)与均衡器输出y(n)的差。其中,核心的LMS算法[4]是利用梯度估计值来代替梯度向量的一种快速搜索算法,基本思想是调整滤波器的权值参数,使滤波器的输出信号与期望信号之间的均方误差(MSE)最小。其迭代更新过程如下:

①初始化W(0)=0;n=0;μ=const;

②更新n=n+1;

误差:e(n)=d(n)-WT(n-1)X(n);在DDLMS算法中,d(n)由判决器对均衡器输出信号进行判决产生。

更新抽头系数:W(n+1)=W(n)+μX(n)e(n)。其中,X(n)为输入信号;W(n)为抽头系数。

2 均衡器的FPGA实现

利用Xilinx公司的软件(System Generator)实现的基于DDLMS算法的基带信道均衡器,硬件实现主要分为横向滤波器模块、均衡算法模块和误差计算模块3个部分。

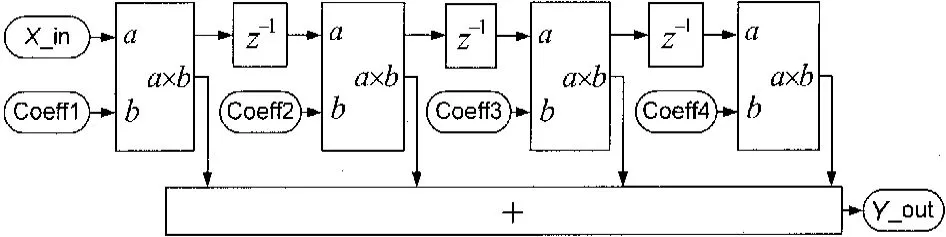

2.1 滤波器模块

滤波器是均衡器的核心单元,它决定均衡器的工作效果。设计中采用了一个8阶抽头系数可变的横向滤波器。横向滤波器的实现主要用到延迟单元、乘法器和加法器3个单元。其中最关键的模块是乘法器和加法器。乘法器完成抽头系数与输入信号的乘积,在设计中使用System Generator中的Mult模块来实现,Mult中可以根据自己设计的要求设定合适的延迟;加法器实现最后的滤波信号输出。在实现过程中,使用软件(Xilinx System Generator)中的乘法器和加法器构建横向滤波器的结构,加法部分采用了加法器树结构。4抽头横向滤波器结构如图1所示。图1中,X_in为待均衡的信号输入端口,Coeff为抽头系数输入端口。

图1 滤波器模块结构

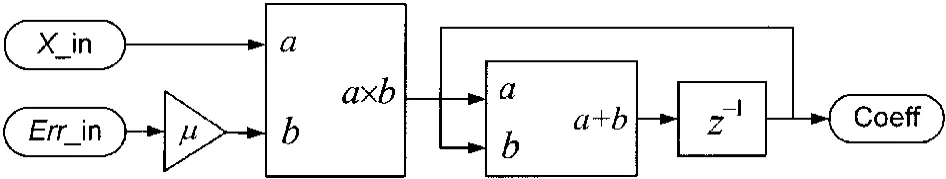

2.2 DDLMS算法实现模块

DDLMS算法的核心是基于LMS算法的系数更新方程:W(n+1)=W(n)+μX(n)e(n),它利用收敛误差以及迭代步长来控制抽头系数的更新。如图2所示,每一个抽头的系数的更新用到2个乘法单元和1个加法器,其中的迭代步长 μ取的是0.002 5。要实现均衡误差收敛,除了按照更新方程构建好算法实现模块外,还有2个关键点:①为保持输入信号X(n)和误差信号e(n)的一致性,要将输入信号X(n)进行合理的延迟以对齐误差信号e(n);②为了实现均衡器的收敛,滤波器主抽头的位置要确定好,并要对主抽头的系数设定一个合理的初始值。在该设计中,设定第3个抽头为主抽头,初始系数设定为1[5]。

图2 系数更新模块

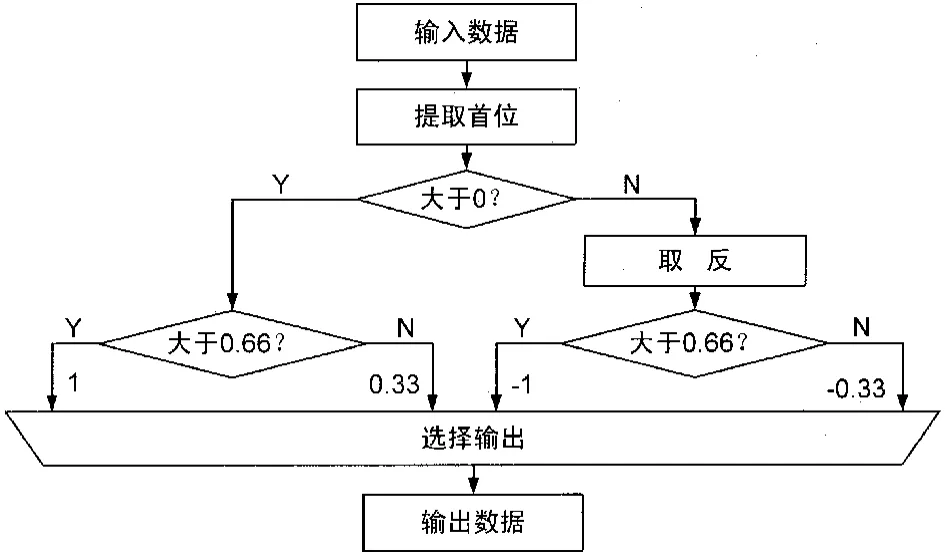

2.3 误差计算模块

判决器的实现是此模块的核心。判决流程如图3所示。均衡后的信号送到判决模块,首先提取首位判断其是否大于零,然后再进一步判定其绝对值是接近0.3还是接近1,根据这2个条件判决均衡后信号。再利用一个减法器将判决后的信号与滤波器输出信号做差,结果就是需要的收敛误差。此模块正常工作的关键是:①保证判决模块能得到正确的判决结果;②保持判决后的信号和滤波器输出信号的对应性,使误差e(n)对应正确的时刻。

图3 判决流程

3 仿真测试

3.1 测试模型设计

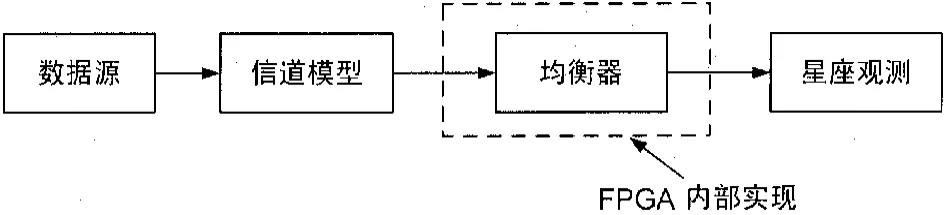

均衡器仿真测试利用软件(Matlab/Simulink)实现,首先使用工具(Xilinx Blockset)中的Gatewayin和Gatewayout模块界定好要在FPGA内部实现的模块后,再利用matlab构建相关的测试信源和观测模块。

利用Matlab中的随机信号源构建一个能随机产生(-1,-0.3,0.3,1)随机序列的数据源模块,把它作为输入信号。在数据源后端加入一个系数可调的数字滤波器来模拟多径信道,通过更改系数值来模拟不同的信道状况,此模型中滤波器的系数分别是0.9,0.36,0.25,0.107。最后将设计的信道均衡器加入系统中,构成如图4所示测试模型。

图4 信道均衡器测试模型

3.2 测试结果分析

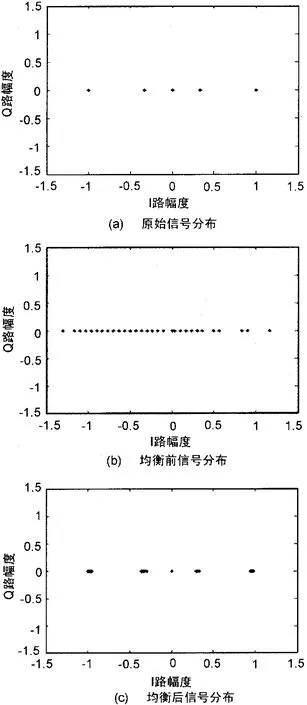

输入信号在均衡前后的信号分布如图5所示。

图5 均衡前后信号分布图对比

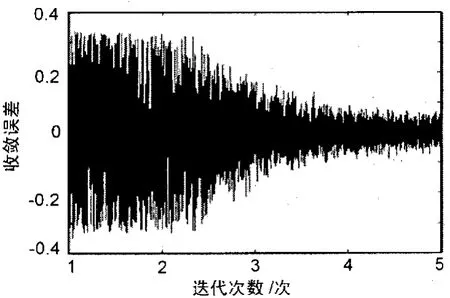

收敛误差随输入数据点数的增加的变化情况如图6所示。从测试结果来看,均衡后的信号能够很好地逼近原始信号,收敛误差在刚开始阶段较大,随着均衡的进行,误差最终能收敛在一个要求的范围内,并且比较稳定。测试结果表明,设计的信道均衡器达到了要求的效果。

图6 收敛误差图

4 结束语

设计实现了一个基于DDLMS算法的信道均衡器,利用Matlab和Xilinx的System Generator进行仿真验证,结果表明所设计的信道均衡器达到了理想的效果。设计基于Xilinx的System Generator实现,相对于传统的基于HDL的FPGA开发模式,这是一种比较快捷的实现方法,并且其与Matlab之间的无缝连接使得仿真测试更为方便。此外在该设计的基础上,可以尝试研究基于CMA等其他均衡算法的信道均衡器的开发。另外,该设计重点是功能实现,没有过多的考虑器件的资源利用率以及与通信系统其他模块之间的接口等问题,进一步的工作可以此设计为参考,使用硬件描述语言实现资源利用率高和结构更为优化的信道均衡器的设计。

[1]纪志成,高春能.FPGA数字信号处理设计教程——System Generator入门及提高[M].西安:西安电子科技大学出版社,2008.

[2]PROAKIS J G,SALEHI M,BAUCH G.现代通信系统(MATLAB)[M].北京:电子工业出版社,2008.

[3]TREICHLER J R,FIJALKOW I,JOHNSON C R.Fractionally Spaced Equalizers[J].IEEE Signal Processing Magazine,1996(5):65-81.

[4]张贤达.现代信号处理[M].北京:清华大学出版社,2002:188-213.

[5]张 建.短波数字通信中的均衡技术研究[D].成都:电子科技大学,2005:37-51.