基于FPGA的GMSK调制设计研究

2011-06-13赵飞燕

赵飞燕

(宁夏师范学院物理与信息技术学院,宁夏固原 756000)

0 引言

GMSK(高斯滤波最小移频键控)[1]调制作为一种连续相位的恒包络调制,具有带外辐射小、频谱利用率高的特点,在通信中获得了广泛应用,GSM系统中是BT=0.3的GMSK调制。在军事通信中,GMSK调制与跳频通信相结合,利用GMSK的恒包络、频谱利用率高的特性以及跳频通信的抗干扰、抗截获性,可以实现军事通信中的高速、安全的数据传输,因此研究实现GMSK的调制是很有现实意义的。

本论文首先介绍了GMSK调制的相关理论知识,其次用matlab软件对其进行建模并且仿真,最后在FPGA上实现了GMSK调制的功能。

1 GMSK调制相关原理

1.1 框图简介

在调制端首先将二进制输入数据进行双极性变换;然后送进高斯滤波器,对其相位进行平滑;用相位累加值进行查表得I、Q两路;然后通过内插滤波,将I、Q两路的速率和载波的速率进行匹配后采用正交调制的方法得到GMSK的数字信号;最后通过数模转换芯片将数字信号转换成模拟信号送到传输线上。

图1 GMSK调制框图

1.2 高斯滤波器原理

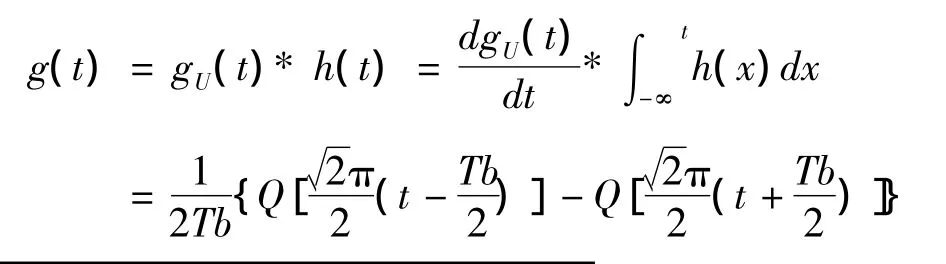

因此高斯滤波器的矩形脉冲响应为:

又因为在实际实现时,数据都是从t>0开始发送的,所以g(t)将向t轴正向移动

1.3 内插滤波原理[2][3]

在通信调制解调中一个重要的环节就是速率的变换。比较容易想到的方法是将数据直接抽取或者内插,然后通过一个低通滤波器去除谐波分量。但是这种算法对硬件的资源要求很高。

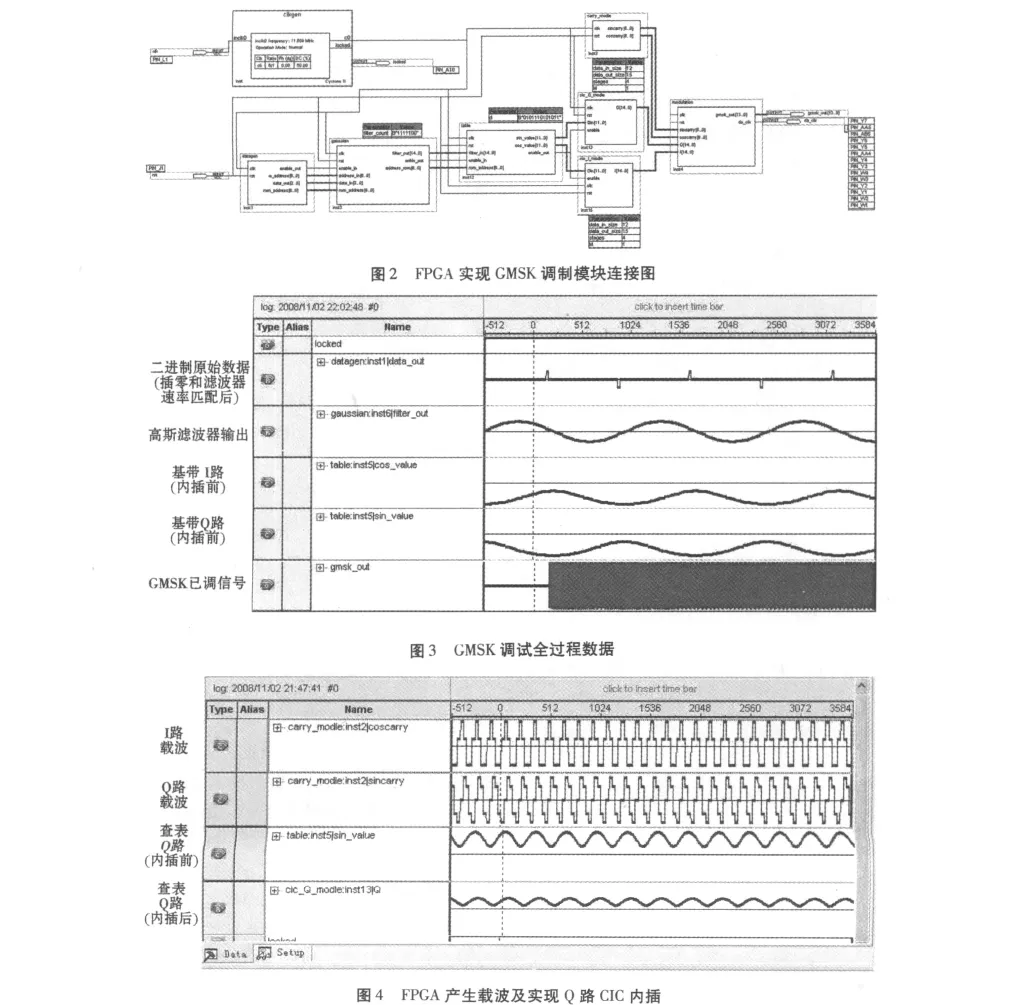

在数字信号处理中有专门的抽样率变换滤波器,它包括抽取滤波器和内插滤波器。在本文的GMSK调制过程中主要用到了累积梳状内插滤波器(CIC),这种结构的滤波器的基础是完美的极点零点抵消,算法适合硬件实现。

所谓累积梳状滤波器,是指该滤波器的冲激响应具有如下形式:

据Z变换的定义,单级CIC滤波器的Z变换为:

2 FPGA实现

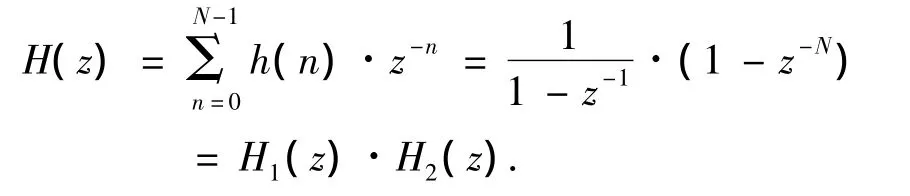

为了适应现代无线通信的快速发展,通信设备应该具有广泛的通用性能,即采用软件无线电技术。因此本论文采用可编程器件来实现上述的GMSK调制算法[5]。具体芯片为Altera公司的CycloneII系列的FPGA,开发平台为Quartus II软件,开发语言为硬件描述语言(VHDL)。

按照matlab仿真的算法和参数在Quartus中构建如下模块,并且采集在线调试的数据:

3 结束语

本文首先对GMSK调制算法进行了分析和仿真,整个仿真从原始的二进制比特流到高斯滤波,再通过内插,最后正交调制得到GMSK调制信号。为了验证该算法具有实用价值,在FPGA上对其进行实现,然后用数字示波器采集模拟线路上的输出,结果和仿真相一致。

[1]周炯槃,庞沁华,续大我,等.通信原理[M].北京:北京邮电出版社,2005.

[2]Uwe Meyer-Baese.数字信号处理的FPGA实现[M].刘凌,译.北京:清华大学出版社,2006.

[3]宋威,曾桂根,杨震,等.软件感应电台中的内插成形处理及其应用分析[J].南邮学报,2002(2):3-7,12.

[4]徐明远,邵玉斌.MATLAB仿真在通信与电子工程中的应用[M].西安:西安电子科技大学出版社,2005.

[5]潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2007.