March算法在BIST电路设计中的作用机制

2011-06-11张莹赵纶

张莹,赵纶

(电信科学技术研究院,北京 100094)

0 引言

随着So C技术的发展,为了弥补传统电路测试扫描技术效率低的不足,产生了一种能够快速并有效地对数字系统进行测试与诊断的方法,即:自测试技术.但自测试技术常常是在软件中实现的,致使在电路测试中不可避免的存在诊断分辨率差、诊断时间长、效率低和使用费用较高等缺点.为了解决上述问题,一种电路的硬件自测试方法,即:通过在芯片内部集成少量的逻辑电路实现对集成电路的测试技术应运而生,这就是内建自测试(BIST)技术.该技术具有结构简单、有效测试时间短、测试灵活性强、可以实现在线经常性测试等优点.

本文基于March CE算法,设计了一种基于HHNEC 0.13μm的多片单、双口RAM为测试对象的串行“BIST”电路.在电路内部自身生成测试向量,而不需要外部施加激励,并依靠自身决定得到的测试结果是否正确.该电路可以有效的满足嵌入式存储器的测试需求,实现对存储器的准确检验和故障定位.

1 一种可嵌入式BIST电路设计

1.1 BIST电路结构原理

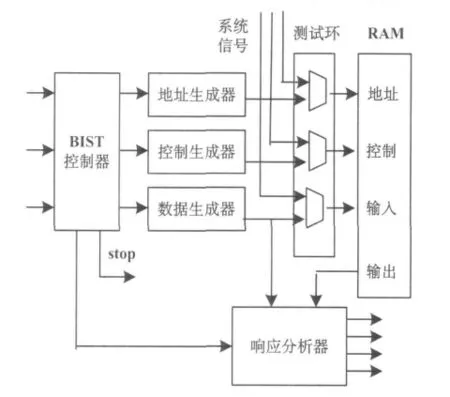

设计是基于March CE算法设计了一种可嵌入式BIST电路,这种BIST电路可以随意而灵活的嵌入到各种数字电路中,自动完成数字电路系统中的存储器测试,该电路的结构原理见图1所示.

图1 BIST电路结构原理图

图1电路系统的组成:①BIST控制器:它是算法控制的核心;②地址生成器:产生遍历整个RAM的地址序列;③数据生成器:产生数据及其“取反”的值;④控制生成器:在BIST控制器测试模式信号指挥下选择RAM的输入信号;⑤响应分析器:实现测试响应分析并行机制.

该电路的工作原理是:上电启动后,系统进入测试模式,开始测试存储单元.若发现故障单元,则BIST电路将故障信息传给响应分析电路,故障地址被保存到按内容寻址存储器中,生成故障位图.测试完成后,内建自修复算法根据位图提供的故障信息分配冗余资源覆盖故障单元.当进入正常工作模式时,BIST电路被旁路,要访问的地址被送往系统,由系统判断所需要的存储单元是否为已知故障单元.若是,则进行地址重映射,调用冗余单元;若不是,则访问正常的存储单元.

1.2 BIST电路设计与March算法的作用机制

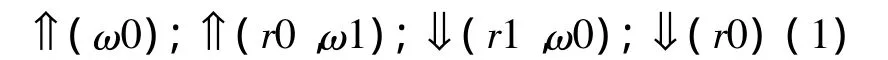

在BIST电路设计时,先要从故障覆盖率和实现的复杂度两方面进行综合考虑,来选择March算法的故障覆盖率高于80%,复杂度只有6n.March算法如下:

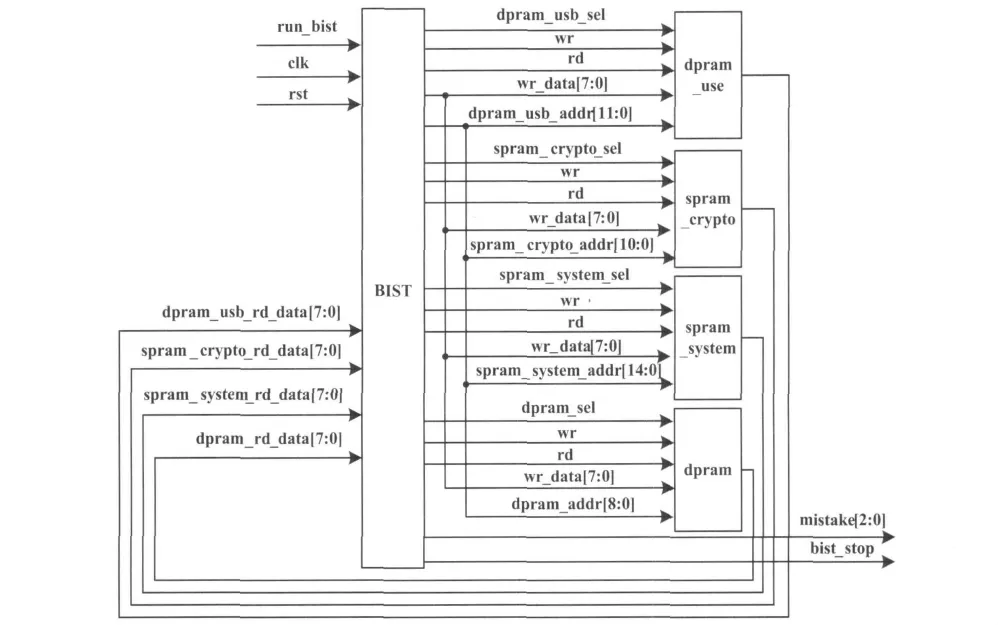

图2电路设计图中原理主要是依据式(1)的作用机制.依据图1的结构原理进行了BIST电路设计,电路设计图见图2所示.

图2 BIST电路设计图

其作用机制为:当run_bist信号有效,且clk为上升沿、rst为低电平,BIST模块开始工作.首先选择待测 RAM,其中:dpram_usb_sel为 dpram_usb的片选信号,其中0选择,1屏蔽;spram_crypto_sel为spram_crypto的片选信号,其中0选择,1屏蔽;spram_system_sel为spram_system的片选信号,其中0选择,1屏蔽;dpram_sel为dpram的片选信号,其中0选择,1屏蔽.rd为RAM三态开关,低电平有效.wr为读写控制信号,其中,低电平为写,高电平为读.当wr为低电平时,允许向RAM中写入数据,之后根据March CE算法进行操作,当wr为高电平时允许读出数据,并判断是否与写入的数据值相同,若相同则继续检测,若不同则报错.wr_data[7∶0]为写数据信号,0复位.dpram_usb_addr[11∶0]为 dpram_usb 地址线,12'd2303 复位;spram_crypto_addr[10∶0]为 spram_crypto地址线,11'd2047复位;spram_system_addr[14∶0]为 spram_system 地址线,15'd32767复位;dpram_addr[8∶0]为 dpram 地址线,9'd511 复位.dpram_usb_rd_data[7∶0]为 dpram_usb 读出数据线;spram_crypto_rd_data[7∶0]为 spram_crypto 读出数据线;spram_system_rd_data[7∶0]为 spram_system 读出数据线;dpram_rd_data[7∶0]为 dpram读出数据线.bist_stop复位值为0,当变为1时,表示RAM无错误测试完成.

2 BIST电路测试方案设计

在检测图2电路的测试方案设计中,应用March算法中通用的数据背景对数公式:

式中,X为测试所需的数据背景的个数;B为存储器字长.

考虑在高测试效率和故障覆盖率时,需要对测试向量进行扩展,并记录扩展后的数据背景.当March算法中的读写数据为1(或0)时,就将正向或反向的G个数据背景存储到对应的存储器上,依式(2)依次对每个数据背景按照次序执行相应的操作,由此制约了测试方案机理和测试步骤.

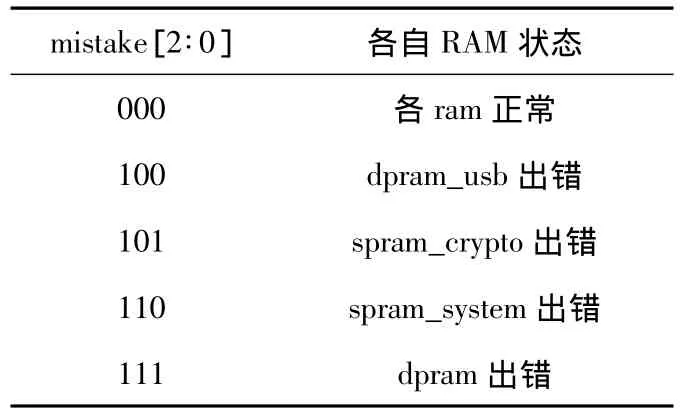

测试中先外加一个run BIST信号,分别对4片RAM进行串行检测,分别为各自的RAM选择信号,每次选择则由低电平表示有效.对选上的RAM进行March CE算法检测,若此片检测无误,则进行下一片RAM的检测.当四片RAM均检测完毕且无错误时mistake[2∶0]信号显示000;当RAM出错时,mistake[2∶0]信号则显示相应数字,并马上中断程序;标志寄存器mistake有5种数值状态,表示各自的RAM出错情况,见附表所示.

附表 RAM出错情况下的数值

在测试方案设计中最关键性技术是:使4片RAM的测试在同一个电路中执行,而各自RAM容量不同,且对于dpram_usb与dpram这样的双口RAM,需分别检测每一个端口.

在测试中,采用最大容量32 K,即地址位宽为15位,则dpram_usb地址线取其中的12位,spram_crypto地址线取其中的11位,dpram_addr地址线取其中的9位.对于双口RAM,在测试中,给出了一个单双口选择信号,在选择单口RAM时,此信号被屏蔽.

3 BIST电路自测试功能的测试

利用图2的BIST电路对2K+256Byte DPRAM、2K Byte SPRAM、32K Byte SPRAM 和512Byte DPRAM芯片进行串行检测.在测试过程中,采用March CE算法检测:固定故障、开路故障、转换失效故障、地址失效故障、字间耦合故障和动态故障.而其中,设计采用22个状态的状态机实现操作流程,并分别对4片RAM进行串行检测,其各状态机转移图见图3所示.

图3 March CE算法的各状态机转移图

图3中,ack为各RAM单个地址测试完成后的标志信号;ack_delay为ack的延时信号;在测试中,state 0确定单个地址是否测试完成,则把A1写入RAM,地址自减;若测试完成,则写入~A1,地址自增;state 1延迟一个clock;state 2确定单个地址是否测试完成,若未完成,则继续写入;若测试完成,则写入A1,地址自减;state 3写入~A1;state 4读数;state 5确定单个地址是否已经读完,若读完,则写入A3;state 6写入数据,地址自减;state 7若单个地址写满,则写入A2;否则写入~A3;state 8读出数据;state 9写入A3;state 10读出数据,地址自增;state 11写入A3;state 12若单个地址写满,则写入A4;否则写入~A2;state 13读数据;state 14写入A2;state 15读出数据,地址自减;state 16写入数据;state 17若地址已经写满,则写入~A4;若未写满,则读出数据;state 18读出数据;state 19写入A4;state 20读出数据,地址自增;state 21写入数据.其中:低电平为写,高电平为读.

4 BIST电路的仿真

在Modelsim环境下对所设计的BIST电路(图2)进行仿真,其Debussy仿真波形见图4所示.

图4 BIST电路的仿真图

从图4中可知,每次对选上的单口RAM进行一次March CE算法检测,对双口RAM进行两次March CE算法检测.当一片RAM测试完成时,result信号升起,若此RAM检测无错误,wrong信号为低电平,且 mistake[2:0]为000;当一片 RAM测试出错时,result信号为低电平,wrong信号升起,且mistake[2:0]根据不同的RAM现实不同值.

从BIST电路的仿真图中还可以看出,该电路能够检测出所有的注入故障,当内建自检测执行完毕后,stop信号自动置位.

5 结论

(1)在BIST电路设计中,采用March CE算法比其它算法精确度高,该算法制约了电路的工作机理和控制机制,制约了电路测试的工作步骤;

(2)本文设计的BIST电路可以同时对单口RAM(SRAM)和双口RAM(DPRAM)进行检测,检测速度快;

(3)当出现错误时,可以指出是哪片RAM上的哪个地址出错,可以指出出错的类型;

(4)只有一个输出信号,便于电路集成后读出信号;

(5)该BIST电路而不需要外部施加激励,并向系统返回测试结果;

(6)该BIST电路具有良好的测试灵活性,能够满足普通嵌入式存储器的测试需求,可实现对存储器的准确检验和故障定位.

[1]ZHAI M J,YIN J H.Memory BIST design and implement based on March C algorithm[J].Journal of Harbin University of Commerce(Natural Sciences Edition),2009,25(5):549-552.

[2]XU Z M,SU Y P.SRAM BIST Circuit Design Based on the March C Algorithm[J].Semiconductor Technology,2007,32(3):245-247.

[3]YAO L T,TAN E M.Pattern generation research of BIST based on low power[J].Electronic Design Engineering,2010,18(8):71-74.

[4]ZANG B C,JIANG D W.A BIST test scheme of embedded DRAM[J].China Measurement Technology,2005,31(1):69-71.

[5]YAN X L,TANG M.Design of Programmable Memory BIST for Embedded Dual Ports SRAM[J].Computer Measurement& Control,2006,14(7):853-854.

[6]WANG Y,CHEN H.Transparent based programmable BIST scheme for memory test[J].Electronic Measurement Technology,2007,30(4):6-8.

[7]ZHANG L,LOU S Q.Research of Embedded SRAM Build-in Self-test in the SoC[J].Electronics & Packaging,2007,7(11):28-30.