基于SPI接口ADC和FPGA的并行多通道同步采样系统设计*

2011-06-06胡生亮李朝旭

顾 颉 胡生亮 李朝旭

(91388部队93分队1) 湛江 524022)(海军工程大学电子工程学院2) 武汉 430033)

1 引言

并行多通道同步采样是实现基于传感器阵列的时延估计和目标定位的关键,在现有的数据采集系统中,通常采用单片机或DSP(数字信号处理器)作为CPU,控制ADC(模数转换器)、存储器和其他外围电路的工作[1~3],但基于单片机或DSP设计的数据采集系统都有一定的不足,均不适用于本文所述的基于传感器阵列的时延估计和目标定位系统,原因如下:1)单片机的时钟频率较低,各种功能都要靠软件的运行来实现,软件运行时间在整个采样时间中占很大的比例,效率低,难以适应波束成形和快速目标定位的要求;2)DSP的运算速度快,擅长处理密集的乘加运算,但实现复杂的外围硬件逻辑控制时依然需要软件编程实施,灵活性和可扩展性较差。

在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA擅长并行处理,时钟频率高,内部时延小,全部控制逻辑由硬件完成,速度快、组成形式灵活,可以集成外围控制、译码和接口电路;最主要的是FPGA可以利用EDA工具进行设计、综合和验证,加速了设计过程,缩短了开发周期,效率高而且扩充能力强。

而已有的基于FPGA的多通道同步信号采样系统往往基于ADC+多通道开关(也有集成化的含有多通道开关的 ADC,如 ADS8342/8361等)的方式[4~5],这种方案在信号采样时按时间片轮回,在波束成形时再做时间差补偿,实现了时基“软”同步,不仅结构复杂而且容易引入系统误差,也无法实现多路信号的高速同步采样[6]。本文针对垂直三阵元水听器对目标定位的应用需求,采用FPGA和SPI串行接口ADC实现了一种多通道同步采样方案,由FPGA并行同步控制多路SPI接口ADC的工作时序,实现了时基“硬”同步,具有结构简单、速度快、扩展性好等优点,仿真和试验验证了设计方案的可行性。

2 一种多通道同步采样系统的基本原理

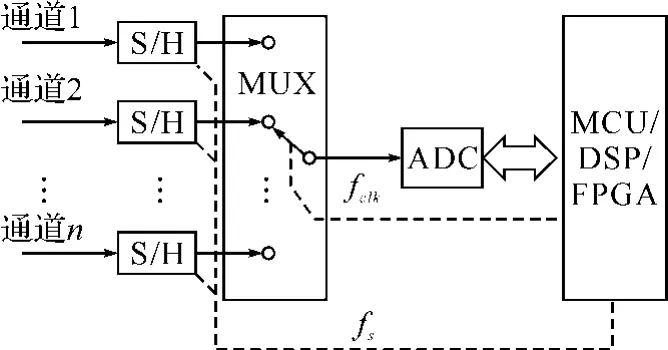

一种常见的多路信号同步采样方案如图1所示[7]。图1中的采样脉冲(设采样频率为fs)由通道开关轮巡信号(设频率为fclk)分频得到,且两者必须要保证严格的相位对准,这种方案通过多路信号复用同一个ADC的方式节约了系统成本,但是在基于传感器阵列的时延估计和目标定位系统中应用时存在以下缺点:1)时延估值要经开关信号轮巡周期补偿,增加了波束成形算法和时延估计算法的软件复杂度;2)假设信号带宽为fc,奎斯特采样频率fs=5fc,则fclk将正比于采样通道个数和fs,难以实现对传感器信号的大通道高速同步采样;3)图1所示方案的可靠性瓶颈限制在通道开关处,并不具有较强的容错性和鲁棒性。若能够实现fclk=fs下的多通道同步采样则可以避免以上问题。

图1 一种多通道同步采样系统的原理框图

3 本文的多通道同步采样的设计与实现

3.1 硬件电路设计

本文的被动声目标定位系统通常需要长期处于值更状态,对功耗、体积等需求较高,而SPI接口的ADC只需要三根信号线即可完成对输入模拟信号的采样,具有体积小、功耗低等优点,此类ADC常见于TI公司的 ADS8321、ADS8325、ADS7817、ADS7822等逐次逼近型AD转换芯片[8]。以 MSOP-8封装、16bit、差分输入 ADC芯片 ADS8321为例,其100kHz采样频率下的典型功耗只有4.5mW,静默状态下的最大电流为3μA,适合于长期连续工作;且被动声目标的宽带辐射噪声通常在10kHz以下的低频段,SPI接口的ADC可简单地通过改变驱动时钟DCLOCK的方式获得不同的奎斯特采样频率。

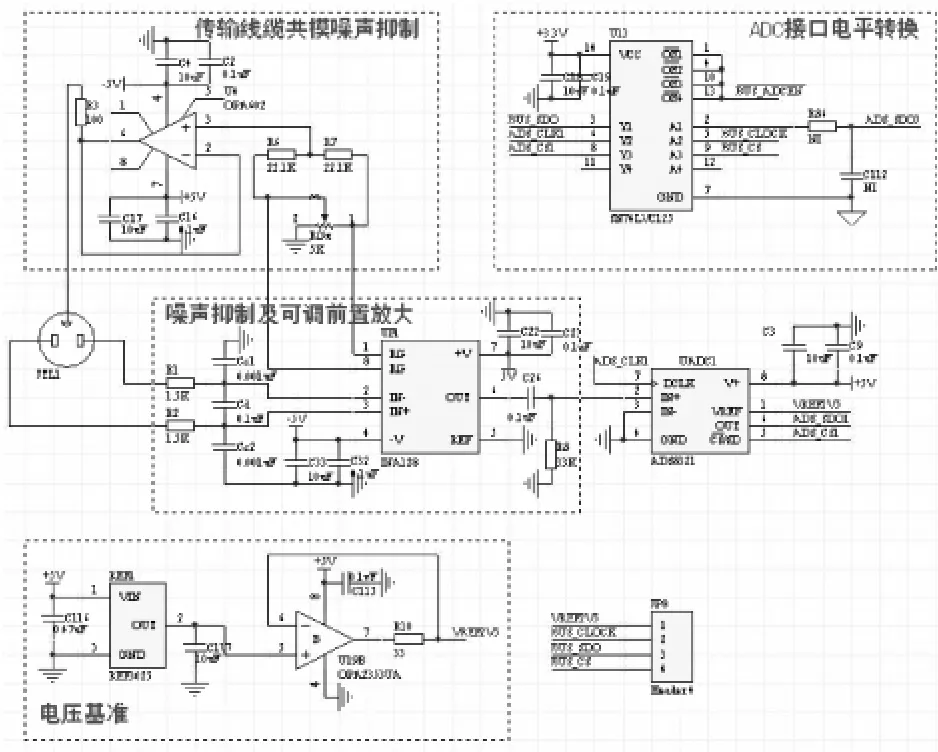

图2所示为基于ADS8321的AD转换及相关外围电路设计,主要包含以下几部分:

图2 SPI接口ADC及外围硬件电路设计

1)噪声抑制及可调增益放大

2)传输线缆共模噪声抑制

连接传输线缆的屏蔽层,以通用运放OPA602为核心组成噪声抑制电路,用于抑制长距离传输线缆上的共模噪声干扰[10];

3)电压基准

以基准电压芯片REF3025为核心,并在输出后级增加电压跟随器,提高其驱动能力,向多个ADC芯片提供高精度的2.5V基准电压;

4)ADC接口电平转换

以低电压三态输出高有效四总线缓冲门74LVC125为核心,向处于5V逻辑接口电平的ADS8321提供3.3V低电压接口,以兼容FPGA、MCU等控制单元的接口电压。

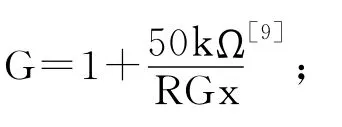

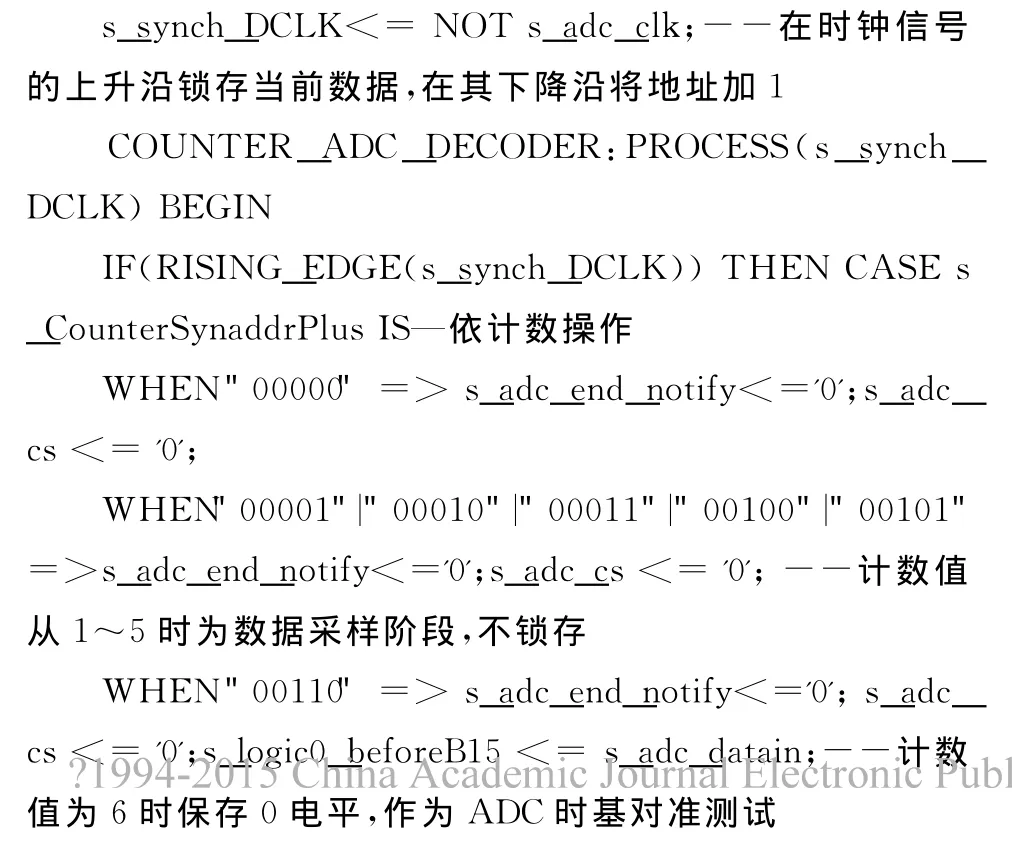

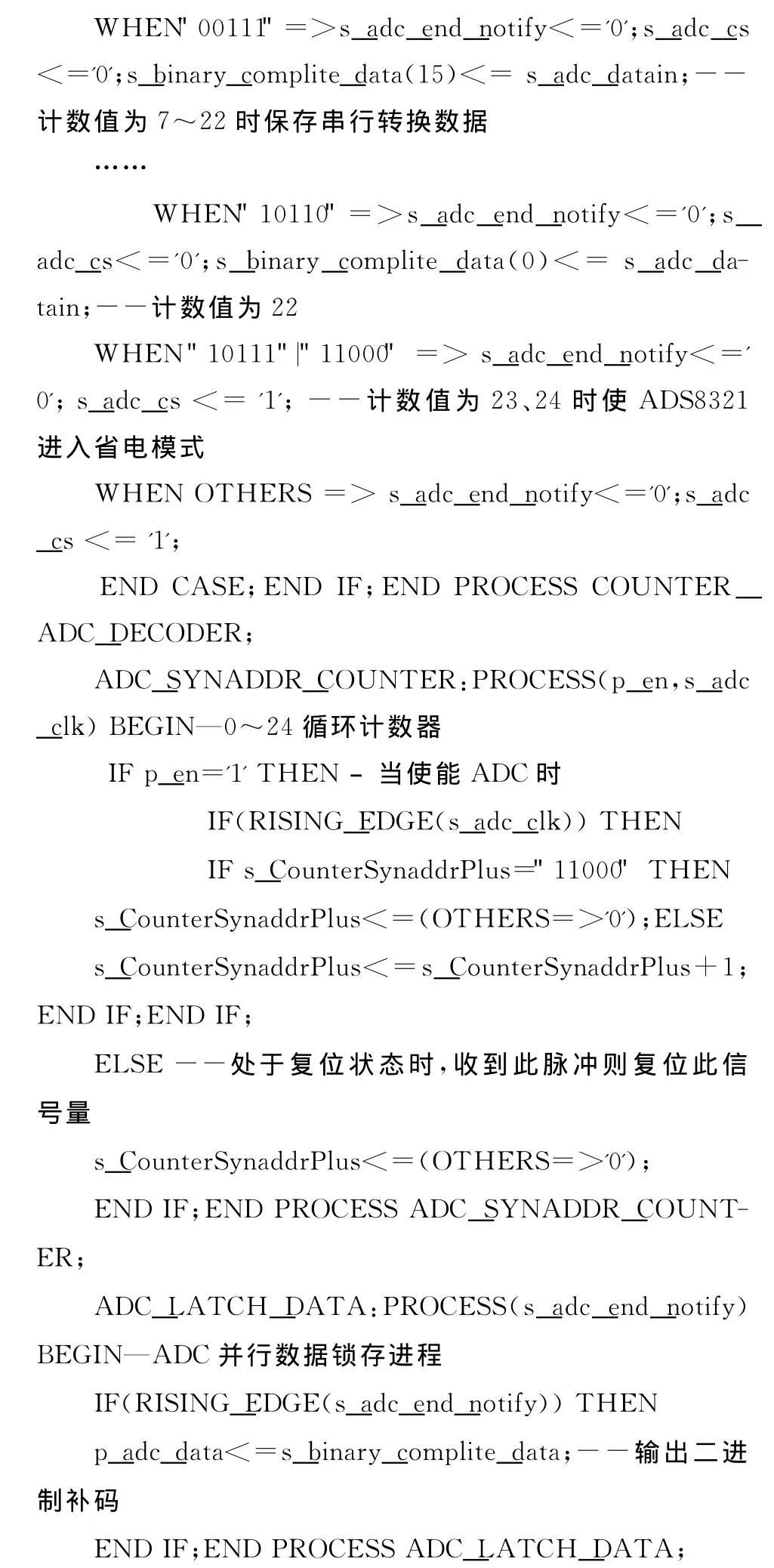

3.2 SPI接口ADC的FPGA驱动

图3 SPI接口ADC的工作时序图

3.3 多通道同步采样的FPGA辅助功能设计

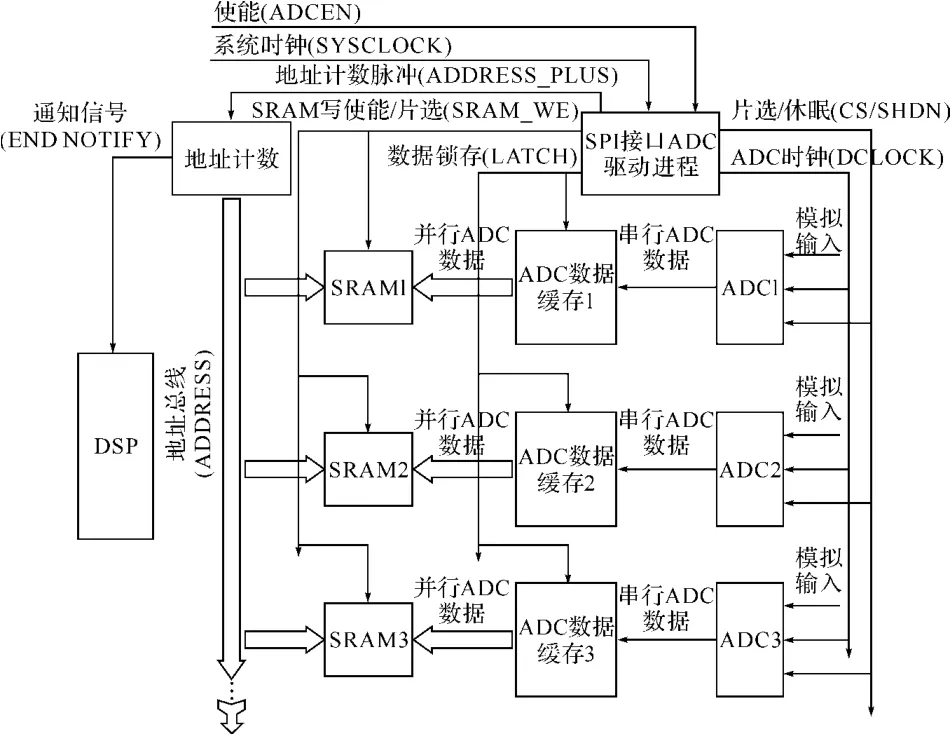

通常情况下,时延估计和目标定位都需要一定的时间累积增益,这就需要在FPGA内部或外围电路中部署一定容量的采样数据缓存空间。以三传感器阵元被动声目标定位系统为例,多通道同步采样的FPGA结构原理图如图4所示。

图4中所有ADC由同一个进程驱动,数据锁存信号也来自于同一个进程,以保证严格的采样时基对准,ADC的采样结果在缓存中做串-并转换后并行存储到对应输入通道的静态存储SRAM中;也可以采用多路信号复用单SRAM的方式,此时需要在ADC数据缓存后增加存储器按段寻址和数据重组进程。按照图4所示结构,当增加模拟输入通道数时只需要在相应的地址、ADC驱动等总线后依次扩充硬件即可,并不需要改变FPGA的软件设计,可扩展性较强。

图4 本文的多通道同步采样FPGA结构框图

4 功能验证

图5 SignalTapⅡ嵌入式逻辑分析仪采样波形

为进一步验证FPGA和ADS8321实际硬件电路的运行情况,使用SignalTapII嵌入式逻辑分析仪同步观察AD转换后的2路正弦信号,如图5所示(由于SignalTapII运行时需要占用FPGA片内寄存器资源,因此图中只采集数据总线和地址总线的部分信号)。其中FPGA芯片选用ALTERA公司Cyclone系列的EP1C12,该芯片内含有2个PLLs、12060LEs及239616Total RAMbits。图5中的信号SAMPLE_DATA1和SAMPLE_DATA2为SignalTapII捕获到的2路800Hz正弦波形,存储器写使能信号SRAM_WE和地址信号ADDRESS也能够按预期时序输出,且ADS8321的测试输出信号s_logic0_beforeB15(即AD转换数据前的一位零电平)也是正确的。

5 结语

本文给出了一种并行多通道同步采样设计方案,该方案以SPI接口的AD转换器和FPGA为核心,实现了并行多通道同步采样的时基硬同步,具有结构简单、速度快、可扩展性好等优点。波形仿真和SignalTapII嵌入式逻辑分析仪采样验证了设计的有效性。

[1]王宁,梁志瑞,赵飞.基于PC104和DSP的交流电量同步采集系统[J].电力自动化设备,2009,29(11):136~139

[2]阎振华,黄建国,张群飞.基于ADSP21160的多通道同步采样并行处理系统[J],计算机工程与应用,2005(12):129~131

[3]铁勇,刘洋.相关时延估计方法DSP实现研究[J].内蒙古大学学报,2007,38(6):689~692

[4]傅晓程,祁才君.ADS7864及其应用[J].仪表技术,2002(2):23~25

[5]崔玮玮,曹志刚,魏建强.声源定位中的时延估计技术[J].数据采集与处理,2007,22(3):90~100

[6]李红娟,孙超.加速度下的水声通信多普勒频移补偿方法[J].西北工业大学学报,2007,25(2):181~185

[7]张贵清,朱磊,颜露新,等.基于FPGA的多路同步实时数据采集方案设计与实现[J].测控技术,2005,24(12):26~29

[8]Designer's Guide.Application Reports[Z].Texas Instruments,2000:192~196

[9]李全利,王振春.一种基于DSP的三相交流采样技术[J].自动化技术与应用,2008,27(12):85~89

[10]周恒保,袁慎芳,邱雷.基于PXI总线的多通道程控电荷放大器设计[J].压电与声光,2010,32(4):664~666,670