基于SystemVerilog的I2C总线模块验证

2011-06-01申志飞易茂祥梅春雷

闫 涛,申志飞,易茂祥,梅春雷

(合肥工业大学电子科学与应用物理学院,安徽合肥 230009)

随着SOC的快速发展,数字逻辑设计复杂度随之提高,验证的难度也越来越大。调查显示,有1/2以上的SOC项目在第一次流片失败的主要原因是存在功能缺陷。

统计显示,验证设计很大难度。将复杂模块集成后,难以在验证中将芯片实际可能遇到的所有条件模拟执行。发现设计中的边界条件以及深层次的设计缺陷也是面临的关键挑战,因此需要先进的验证方法学研究和应用。Synopsys公司推出基于Systemverilog语言的VMM(Verification Methodology Manual)验证方法学则是较突出的一种,在业界也有广泛的应用,并逐渐取代了Verilog语言的传统验证方法,成为IC验证领域的一种发展趋势[1-2]。

SystemVerilog建立在 Verilog语言的基础上,是IEEE 1364 Verilog-2001标准的扩展增强,兼容Verilog 2001,并成为下一代硬件设计和验证的语言[3]。相对于传统的Verilog语言,SysemVerilog具有丰富语言能力,能描述复杂验证环境,包括带约束随机激励产生、面向对象编程和功能覆盖统计。这些特点使用户开发出能自动产生大量验证情节的测试平台。文中介绍了基于SystemVerilog语言的验证平台,并在分析I2C总线协议的基础上重点介绍事务产生及驱动模块的设计[4]。

1 SystemVerilog验证平台

验证平台主要是为了生成激励信号并将激励信号提供给DUT,再进一步分析DUT的响应是否正确。包括以下步骤:(1)产生激励。(2)把激励施加到DUT上。(3)捕获激励。(4)检验正确性。

1.1 基于Verilog的传统验证

传统的Verilog验证方法是用Verilog语言搭建验证平台。对DUT的功能验证只能用人工脚本编写Testcase来配置和控制DUT,以实现预定功能的测试。然而这需要消耗大量资源,而且还无法验证到没有预料到的缺陷。当验证完成后,仍只能依赖人工检测验证是否完备,除了消耗资源以外,还无法得到理想的功能覆盖率。显而易见,诸如此类的问题在基于Verilog的传统验证中是难以避免的[5]。

1.2 基于SystemVerilog的验证环境

使用SystemVerilog语言建立的激励生成器(generate),事务驱动器(drive),监控器(monitor),记分板(scoreboard)等完成上述步骤。

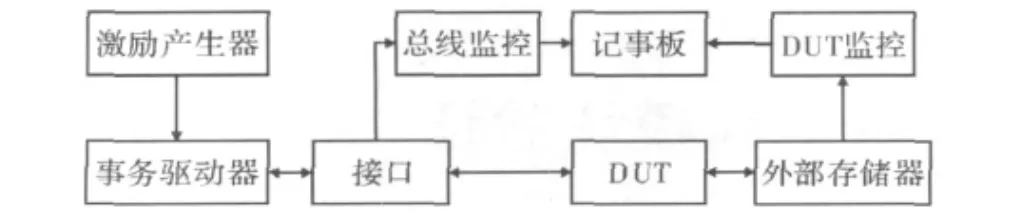

图1展示了I2C的SystemVerilog验证环境架构,包括DUT、接口和验证平台。其中验证平台由激励发生器、事务驱动器、总线监视、DUT监视器和记事板等组成。

图1 基于SystemVerilog的验证结构图

接口(interface)是SystemVerilog提供的一个新的、高层抽象的模块连接。接口在关键字interface和endinterface之间定义,它独立于模块。接口在模块中就像一个单一的端口一样使用。在最简单的形式下,一个接口可以认为是一组线网。通过使用接口,在进行一个设计时可以不需要首先建立各模块间的互连。随着设计的深入,设计细节也会变得越来越清晰,而接口内的信号也会表示出来。当接口发生变化时,这些变化会在使用该接口的所有模块中反映出来,而无需更改每个模块。一个接口可以像模块那样例化,也可以像信号一样连接到端口。SystemVerilog的接口还可以包含内建的协议检查以及被使用该接口的模块所共用的功能。

激励产生器是一个受约束的随机激励发生器,在验证环境开始工作时创建一个事务,随机化其值,然后将其放入信箱传递给驱动器。在SystemVerilog中可以用约束限制随机值的范围,使他们是有效的值,也可以通过其设置测试某些专用功能。

产生器和驱动器通过信道交换数据。信道可以看成一个具有源端和收端的FIFO。源端把数据放进信箱,收端从信箱获取数据。信箱可以有容量限制,也可以没有。当源端线程试图向容量饱和的信箱放入数值时,会发生阻塞直到信箱里的数据被移走。验证平台中信箱的容量为1,每次产生器只能放一笔数据在信箱,直到被驱动器移走才放入下一笔,这样就可以实现对象间通信的同步。

驱动器从发生器接收事务信息,在经过一定的处理后将其输送给DUT。信号监视器用于监控DUT的输入和输出,将其输送至记分板从而通过比较相关信号来验证DUT的设计是否正确。所有组件都是基于SystemVerilog设计,SystemVerilog语言的面向对象的特性大大提高了验证IP核的可重用性。

2 验证环境IP的设计

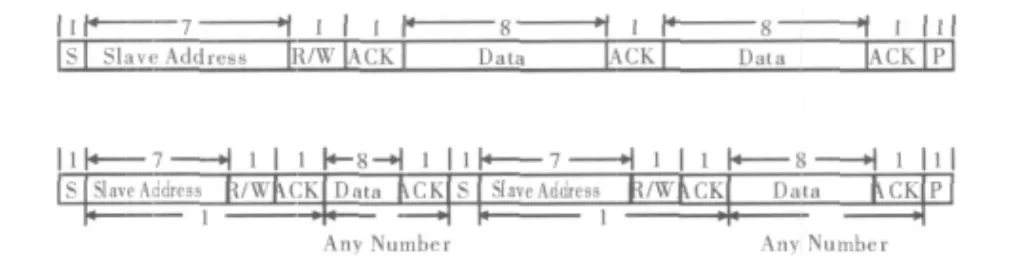

图2 I2C总线传输协议图

文中要验证的DUT是7位寻址的I2C总线模块,其传输协议如图2所示。I2C总线用于连接微控制器及外围设备。是微电子通信控制领域广泛采用的一种总线标准。S代表START,P为STOP,在传输过程中第一个Byte的头7位组成了从机地址,最低位(LSB)是第8位,它决定了传输的普通和带重复开始条件的7位地址格式方向。第一个Byte的最低位是“0”,表示主机会写信息到被选中的从机;“1”表示主机会向从机读信息,当发送了一个地址后,系统中的每个器件都在起始条件后将头7位与其地址比较,如果一样,器件会判定其被主机寻址,至于是从机接收器还是从机发送器,都由R/W位决定。而在数据传输过程中,发送到SDA线上的每个Byte必须为8位,每次传输可以发送的Byte数量不受限制。每个Byte后必须跟一个响应位,在响应的时钟脉冲期间发送器释放SDA线(高),首先传输的是数据的最高位(MSB)。

2.1 事务产生及驱动器的设计

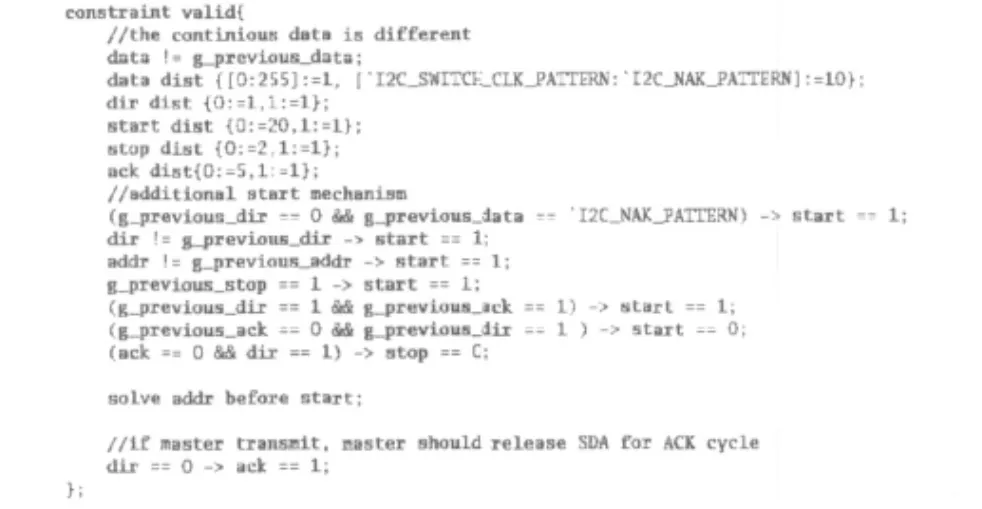

文中重点研究事务产生及事务驱动器的设计。事务产生器通过约束随机产生符合I2C协议的事务。在I2C总线模块验证模块中使用到的约束包括:

(1)合理的寻址范围。(2)改变R/W位之前必须STOP再重新 START。(3)收到 ACK为“0”时必须STOP等,这些约束可以保证生成正确的事务。然而,(1)连续发送不同的数据。(2)按一定比例产生R/W,ACK位的“0”,“1”等。这些约束则可以验证更多边沿特性,提高验证覆盖率。

还可以约束配置条件,例如生成一定数目的事务,以及发生错误的处理方法。总之,采用受约束的随机测试法自动产生的测试集是产生验证负责设计所需激励的唯一可行方法,SystemVerilog提供了多种产生随机激励的方法。图3为本次设计中所用到的一些约束条件。

图3 事务约束条件

事务驱动模块的工作,是通过信箱从事务产生器中取出事务,并根据特定的DUT输入信号的特性对其进行处理,再通过接口输送至DUT。因为驱动器的结构是取决于DUT,要根据此协议产生相应的事务,输送至I2C总线。事务驱动器相当于DUT的软核或者行为级描述。

验证环境作为主机时,发送至总线的事务依次需要START位,7位寻址信号和R/W位,R/W位决定主机对总线的读或写。收到响应的ACK位再写数据到总线或从总线上读数据,每次读周期后主机会发送响应ACK位,而每次写周期后会等待从机发送的响应ACK位。ACK位为1时,主机要发送STOP位,则传输终止。ACK为0则传输继续。在R/W位要改变时,传输必须重新开始,即收到或发出的ACK位为1,然后主机发送STOP。

验证环境作为从机时,DUT主机、START位、7位寻址信号和R/W位依次由DUT发出。而从机在发出对寻址信号的响应ACK位后,DUT会做类似验证环境为主机时的操作。主机或从机在操纵总线时,相应的从机或主机必须释放总线。

2.2 验证环境流程

图4为验证环境在实验中运行的流程,首先需要生成配置条件并把验证环境中的各模块像事务生成、驱动及监控器等连接起来,DUT复位后将会按照配置条件的运行。在测试结束后将会自动生成测试记录,通过此文本文件检查是否通过验证。

图4 验证环境流程图

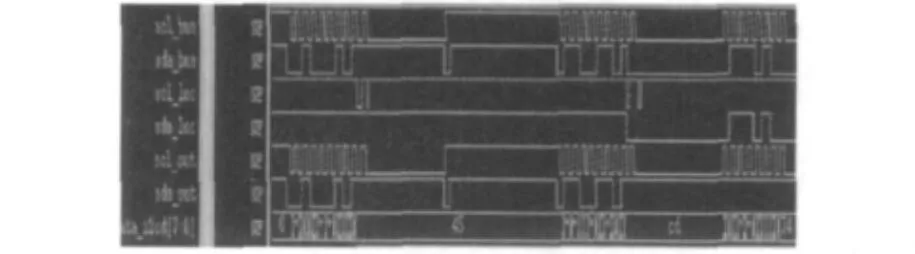

2.3 仿真波形分析

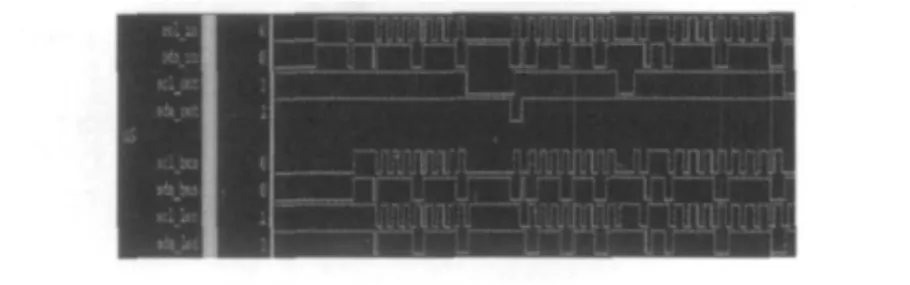

验证过程中产生的波形如图5和图6所示,图5中 scl_bus、sda_bus为总线信号,scl_loc、sda_loc 为验证环境的输出信号,sda_out、scl_out为DUT的输出信号。在此波形中DUT为主机,验证环境中的从机地址为0x66,则主机依次发送START位和7位寻址信号0x22时应答位为1。重新发送寻址信号0x66及R/W位1后,主机与从机建立起连接并由从机写数据至主机。从波形可以看出,主机和从机的区别即是主机控制总线时钟的生成。

图5 DUT做主机仿真波形

图6 DUT做从机仿真波形

在产生256个事务后,DUT的配置做相关改变,主要目的是把DUT的所有情况都遍历一遍,在总共产生20 000个事务后停止仿真。通过 VCS软件中的Coverage功能可以看到此次验证覆盖了所有的功能点,其中 line_coverage,condition_coverage,fsm_coverage 达到100%,toggle_coverage也几乎达到了100%。

从实验过程看出,基于SystemVerilog的方法在整个验证过程中不再需要人工干预,实现了事务的自动生成,驱动、信号的监控、比对,最终生成报告并退出仿真。在仿真次数和运行时间上,基于SystemVerilog的验证方法比使用Verilog的方法无论在仿真次数和运行时间上都大大减少。

文中设计的验证平台结构清晰,模块相对独立。针对文中的DUT,在其IP复用到其他系统芯片时,验证平台中的事务驱动器,监控器等都可直接重用,而接口模型可针对DUT不同的特性稍加修改。这样可以大大节省验证平台的开发时间,提高验证效率。

3 结束语

通过采用SystemVerilog方法设计的DUT验证平台与传统的验证平台相比更具有抽象层次、结构清晰,随机约束的方法可以预期到更多情况。基于SystemVerilog设计的验证平台,模块性强、易于理解和重用,验证过程是一个自动化过程,节省了人力资源和时间,提高了验证效率。

[1]贺珊,张多利,何伟.基于OpenVera的IIC总线接口功能验证平台的搭建[J].合肥工业大学学报:自然科学版,2007,30(3):261 -264.

[2]詹文法.测试平台的可重用性研究[D].合肥:合肥工业大学,2004.

[3]Aceellera.SystemVerilog 3.1a Language Reference Manual[M].Napa,California:Aceellera,2004.

[4]克里斯·斯皮尔.SystemVerilog验证—测试平台编写指南[M].张春,麦宋平,赵益新,译.北京:科学出版社,2009.

[5]夏宇闻.数字系统设计——Verilog实现[M].北京:高等教育出版社,2006.