FPGA设计中跨时钟域同步方法的研究

2011-05-11唐辉艳李绍胜

唐辉艳,李绍胜

(1.北京邮电大学 信息与通信工程学院,北京 100876;2.中国软件与技术服务有限公司,北京 100080)

随着电子自动化设计(EDA)技术的发展,现场可编程门阵列(FPGA)已经在许多方面得到广泛应用,比如将FPGA应用于通信领域,实现数字调制解调、编码解码,FPGA还在实现通信系统中的各种接口中起着重要作用,如PCI总线、SPI总线等。而在FPGA的接口设计中,同步决定了系统的稳定性与接收数据的准确性。但是实际的工程中,纯粹单时钟同步系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果在跨时钟域中采样就会产生亚稳态、采样丢失和采样数据错误等一系列问题,从而使系统无法正常运行。本文就此分析了在FPGA设计中跨时钟域导致的亚稳态现象以及2种同步方法,尤其是基于异步FIFO的同步方法。

1 跨时钟域中的亚稳态

在FPGA的设计中,当用不同域的时钟去采样数据时,如果采样的数据不满足setup时间和hold时间, 这样就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间内处于不确定的状态。在这段时间内Q端产生毛刺并不断震荡,最终固定在某一电压值。此电压值不一定等于原来数据输入端D的数值,这段时间称为决断时间,经过决断时间之后,Q端将稳定到0或1上,但空间是0还是1,这是随机的。

亚稳态的危害主要体现在破坏系统的稳定性。由于输出在稳定下来之前可能是毛刺、震荡、固定的某一电压值,因此亚稳态将导致逻辑误差,严重情况下输出0~1之间的中间电压值还会使下一个寄存器产生亚稳态,即导致亚稳态状态下,任何诸如环境噪声、电源干扰等细微扰动都将导致更恶劣的状态不稳定。这时这个系统的传输延迟增大,状态输出错误,在某些情况下甚至会使寄存器在2个有效判断之间长时间振荡。

只要系统中有异步元件,亚稳态就无法避免,因此,设计的电路要减少亚稳态导致的错误,要使系统对产生的错误不敏感。

2 同步方法

在异步设计中,完全避免亚稳态是不可能的。所以,设计思路应该是:尽可能降低亚稳态出现的概率,也就是尽可能地采取同步方法。

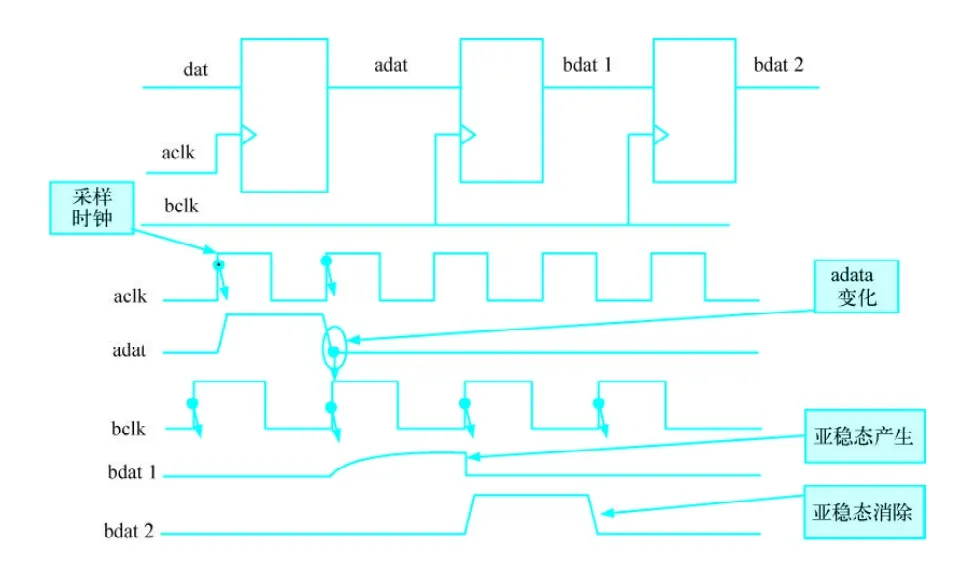

2.1 双锁存器法

为了避免进入亚稳态,通常采用的方法是使用2级寄存器,即一个信号要进入另外一个时钟域之前用另一时钟域的时候进行2次锁存,如图1。式,读写时钟采用2个不同的时钟,写时钟是外部进来的随路时钟,而读时钟采用本地锁相环锁出来的时钟。系统框图如图2。

图1 双锁存器法

图2 异步FIFO结构框图

其中,c lk_a是与data在同一时钟域的同步时钟,而c lk_b是另一时钟域的时钟,经c lk_a锁存后的数据再经c l k_b的正负沿锁2次以后,数据data_out基本就稳定了,理论上,采用这种方法可以有效地减少亚稳态继续传播的概率,但是并不能保证第2级输出的稳态电平就是正确电平。前面说过经过决断时间之后,寄存器输出的电平是一个不确定的稳态值。也就是说这种处理方法并不能排除采样错误的产生。当设计的系统对采样错误不敏感时,如一帧图像编码、一段语音编码等。而对于一些对错误采样比较敏感的系统,则不能采用这种方法来解决跨时钟域的数据采样问题。

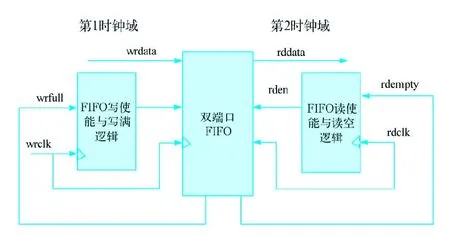

2.2 异步FIFO缓存同步法

使用异步FIFO来存放数据,可以达到数据同步的目的。把数据存放在FIFO的方法是:将上个时钟域提供的数据随路时钟作为写信号,将数据写入FIFO,然后使用本级的采样时钟(一般是数据处理的主时钟)将数据读出即可。这种做法的关键是数据写入FIFO要可靠,如果要使用FIFO,就要求有一个与数据相对延迟关系固定的随路指示信号,这个信号可以是数据的有效指示,也可以是上级模块将数据打出来的时钟。对于慢速数据,也可以采用异步RAM或者FIFO,但是不推荐这种做法。下面主要介绍基于异步FIFO和RAM解决跨时钟域异步问题的方法。

本文所设计的异步FIFO采用循环队列的方

图2中,异步FIFO的端口定义是:wrdata是往FIFO里面写的数据,这个可以视具体情况为2n bi t,wrc lk是写时钟,wr ful l信号是FIFO写满标志,rdc lk是读时钟,rdempty是读空标志,rdata是从FIFO里面读出来的数据。从图中可以看出,整个模块分成2个完全独立的时钟域:读时钟域和写时钟域,读/写操作完全由2个不相关的时钟来控制。在写时钟域,写使能信号是由写时钟来控制的,当外部数据有效的时候有效,写使能为高,直至该帧数据结束,本设计中,写满和读空标志非常重要,对于读/写使能的设计也起着决定性作用,写使能信号一定要在写满标志有效前就结束,将有效数据都写入FIFO,而读使能一定要在读空标志有效前将FIFO里面的数据读空,如果不这样,将会出现数据写覆盖和读错的现象。

本设计中,异步FIFO是调用IP核,空满标志是异步FIFO自己产生的,可用来控制FIFO的读/写使能信号,写使能信号在有效数据到来之后有效,持续到所有有效数据都写入FIFO并且写满标志未有效,这样就可以将所有的有效数据都写入FIFO中;为了防止数据还没有写完全就被读空的状态,特别是读时钟太快的时候,读使能是在当有效数据全被写入FIFO之后启动的,并且在读空之前一直有效,用这种方法就将读写时钟域完全隔离,写入FIFO的数据速率是可调的,当然用这种结构的数据长度是有限的,若数据长度很大时,则要根据读写时钟的频率来选择FIFO的深度,具体如下:若读时钟的频率大于或者等于写时钟的频率,就不用担心溢出问题,FIFO的长度可以任意选择,否则,若读时钟频率小于写时钟频率,只能将FIFO或者RAM的深度增加,使得数据在写满之前已经将数据读完,此时FIFO的深度和读使能信号的配合很重要。

2.3 仿真结果与结论

本结构采用Ver i log HDL硬件描述语言进行电路设计,调用异步FIFO核,在Cyc lone II系列的EP2C8Q208C8 FPGA上得以实现,在Model sim软件中进行功能仿真,并且将该结构用于笔者研究的一个项目中,在Quar tus II软件的在线逻辑分析仪(Signal Tap Logic Analyzer)上调试抓到的信号如图3。

从图3中可以看出,经过FIFO之后出来的数据和时钟完全同步,且在此设计中读写时钟是同频率的,所以FIFO的写入数据速率和读出数据速率也是一致的,不过,由于时钟域的同步是需要时间的,这里设置了128个wrc lk用来缓存写入数据,故从FIFO中读出来的数据相对于写入的数据有一定的延时,这里的延时是128个wrc lk,不同的设计中可以设置成不同的延时。本设计中写时钟和读时钟都是120 M,结果证明这种设计是正确的。

3 结束语

本文讨论了在FPGA中跨时钟域引起的亚稳态现象及其解决方法,重点介绍异步FIFO缓存方法,并且在FPGA中用Ver i log HDL语言实现,经验证该方法能稳定有效地解决跨时钟域的亚稳态问题。能安全实现数据跨越时钟域的传递,并能起到数据缓存的作用,因此是一种较好的方法。

[1] Mutter sbach J.,Villiger T., Kaeslin H, et al.Globally asynchronous locally synchronous architectures to simplify the design of on-chip systems[A] IEEE ASIC/SOC Conference 1999[C],15 -18 Sept.1999: 317-321.

[2] William J. Dally. John W. Plultin. Digital Systems Engineering[C].Cambridge University Press,1998, Page(s): 468.

[3]A. Chakraborty, M.R. Greenstreet interface[C]. Asic/Soc Conference, 2002, 15th Annual.

[4]朱永峰,陆生礼,茆邦琴. SoC设计中的多时钟域处理[J].电子工程师,2003(11):60-61.

[5] 杜 旭,左 剑,夏晓菲,ASIC系统中跨时钟域配置模块的设计与实现[J]. 微电子学与计算机,2004,21(6):173-177.

[6] 宋红东,胡 晨,杨 军. 一种用于高可靠性同步器电路的D触发器设计[J].电子器件,2003,26(1):99-103.