数字锁相技术的研究与实现

2011-05-11胡建萍张欣舒

胡建萍,张欣舒

(杭州电子科技大学电子信息学院,浙江杭州310018)

0 引言

锁相环(phase-locked loop)技术在调制和解调、调频和解调、频率合成电路和时钟同步等很多领域应用极其广泛。以前的锁相环通常采用模拟锁相环设计,由于容易受到电路物理特性影响等原因,导致故障率相对较多,逐渐被数字锁相环技术取代,同时随着集成电路技术的发展,采用可编程逻辑器件FPGA(Field Programmable Gate Array)设计数字系统,把整个数字系统的功能集成到一款芯片实现系统SOC已变得越来越普及。因此,本文采用FPGA控制为核心,设计数字锁相环DPLL(digital phase-locked loop),其可靠性高、体积小的优点,在系统设计中具备极大的实用价值。

1 锁相环的基本原理

锁相环主要由鉴相器、环路滤波器和振荡器构成,用于实现系统输出时钟和某一外部时钟相位同步。锁相环可以对输出信号频率自动跟踪,仅当输出信号的频率与输入信号的频率相同时,输出电压与输入电压相位差值固定,即被锁住,得到最终输出时钟,如图1所示。

鉴相器主要用于对fin和fout进行比较。当环路锁定时,鉴相器输出正比于这两个信号相位差的直流电压Ud。它的实现方式有很多,包括模拟式和数字式。在本次设计中,采用异或门(XOR)数字鉴相器。

图1 锁相环基本结构

数字锁相环中使用的环路滤波器与模拟锁相环中使用的功能一样,主要用于对误差电压Ud进行低通滤波,因此环路滤波器参数对环路性能影响极大。同时,它还有校正环路的功能,对环路的稳定、噪声的滤除和环路带宽都有极大的影响,因此非常重要。

压控振荡器VCO为频率可调的振荡器,输出信号的频率随着输入控制电压的变化发生变化,主要构成方式包括调谐振荡器、多谐振荡器两种。当由于某种原因导致压控振荡器的频率发生变化,使得输出fout相位发生变化,此时fin和fout的相位变化通过在鉴相器中与参考时钟相位进行比较,输出与相位误差信号成正比的误差电压Ud,经过环路滤波器后,得到缓慢变动数值,使得压控振荡器的输出频率恢复到稳定状态,从而实现相位的锁定。

随着对数字技术研究的不断进步,锁相电路中的器件也逐步开始数字化。

2 系统功能设计

设计中采用Verilog HDL进行编程,这种设计方法可以不必考虑特定的制造工艺而在抽象层对电路进行描述,通过使用Altera公司Quartus II软件的逻辑综合工具能够将设计自动转换为任意一种制造工艺版图。如果需要移植到新的系统中,仅需要根据新的工艺对电路的时序和面积进行优化,即可生成新工艺的门级网表。

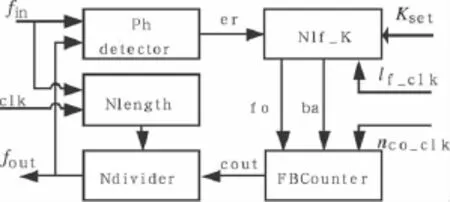

如图2所示为数字锁相FPGA设计原理图,整个系统的工作方式:Phdetector模块用于比较输入信号fin和输出信号fout的相位差,输出误差信号er;Nlf_K模块用于消除相位误差信号er中的高频分量,产生标志信号;FBCounter模块用于根据进位标志信号(fo)和借位标志信号(ba)进行输出脉冲调整;Nlength模块用于对输入信号周期进行计数,自动量化输出N值;Ndivider模块用于对输入信号进行N分频。

图2 锁相环FPGA设计原理图

3 FPGA的选择

本设计采用 Altera公司的 Cyclone EP1C6Q240 FPGA芯片,Cyclone系列芯片,可以内嵌各种IP核,实现强大的控制处理功能。同时这一系列芯片是目前市场上性价比最高且价格最低的FPGA芯片,所以很适用于成本敏感和大批量生产的产品设计,如通信类、消费类、视频处理、测试和测量等各种产品领域。

此系列芯片设计灵活、系统集成能力高,Cyclone EP1C6Q240主要特性包括:

(1)工艺技术:采用300 mm晶元,基于TSMC公司130 nm工艺,小尺寸,低功耗。

(2)低成本架构:器件架构成本最低,可支持5980个逻辑单元(LE),完全可以满足设计的运算需求。

当主电路过流时,电流互感器检测到大电流,反馈给KA,达到KA的电流整定值时,KA将带动YR跳闸,此时,QF3-4断开,QF1-2闭合,绿灯亮。或者手动分闸,分闸继电器KM触点闭合,会给YR提供可以跳闸的电流,完成跳闸。

(3)嵌入式存储器:内嵌M4K存储器块,可支持20块存储块,用于实现单端口 RAM、双端口 RAM、ROM以及同步FIFO(先入先出)和异步FIFO。

(4)I/O支持:185个用户最大可用IO管脚。

4 各功能模块设计

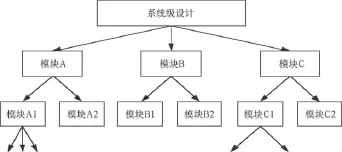

在Verilog HDL设计过程中,应该采用自顶向下Top-Down的原则进行程序设计,如图3所示。通过把硬件系统划分为若干基本模块A,B,C等,然后继续对每个基本模块A,B,C等继续进一步划分为下一层模块,直到每个模块的功能相对独立,基本简单为止。在此设计过程中,需要对每个模块都要经过仿真验证后再继续下一层次设计,最后采用模块调用的方式完成整个系统的描述。

图3 自顶向下设计Top-Down原理

正是由于设计的仿真和调试过程都是从高层次开始,因此很容易在设计初期发现设计上的问题,避免进一步的损失。自顶向下的设计方法方便了系统划分和项目管理,使得百万门甚至千万门的复杂数字电路设计成为可能,避免了重复性的劳动,提高了设计的效率。

4.1 Phdetector模块的设计

目前常用的数字鉴相器有很多种类,比如异或门(XOR)鉴相器和RS触发器鉴相器,锁相环中鉴相器主要用于检测输入信号和输出信号的相位差,本模块设计采用异或门鉴相器方式,用于计算输入信号fin和输出信号fout的相位差并转换为电平信号,同时输出误差信号er至Nlf_K模块作为计数方向控制信号。主要代码如下所示:

4.2 Nlf_K模块的设计

对于数字环路滤波器功能模块的设计,本次采用模数可设置、可逆计数器构成。该计数器为10位(模数通过外部k值设置信号Kset设置)可逆计数器。当整个锁相环系统正常工作,使得鉴相器输出相位差为0时,那么鉴相器输出为一个占空比为50%的方波,因此,当可逆计数器在相同时间间隔之内进行加计数或减计数时,只要外部k值设置信号值保持足够大,那么整个计数器将不会产生超出或溢出的现象。

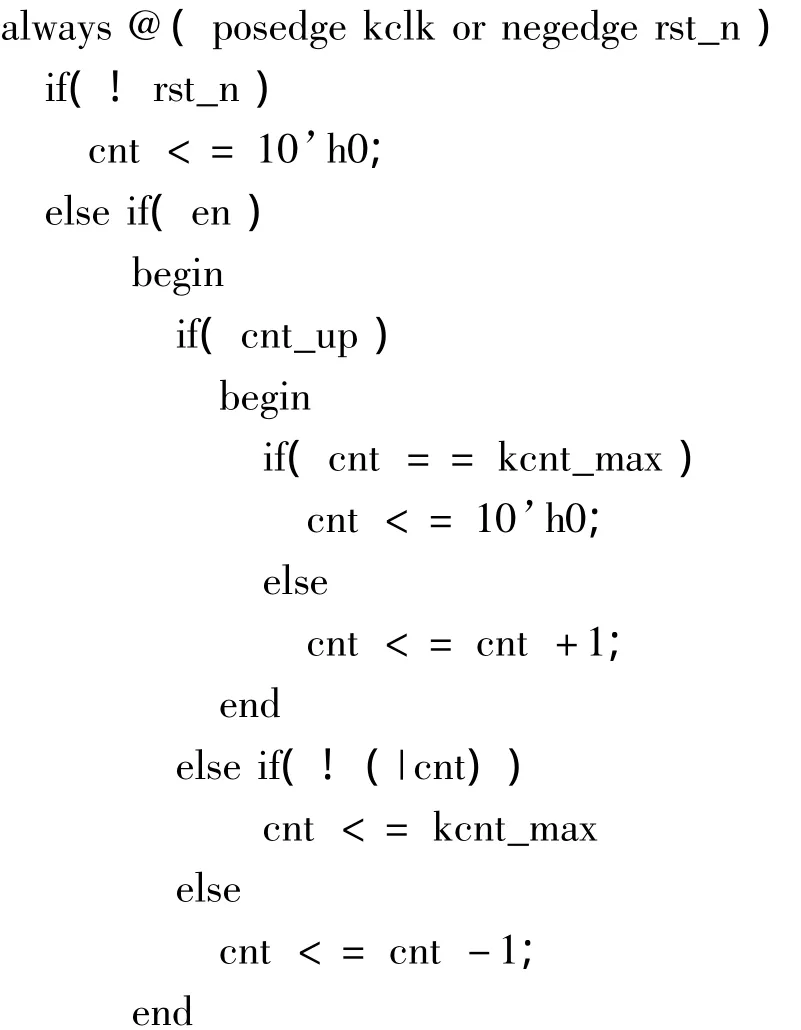

当整个锁相环系统锁定时,输入信号fin和输出信号fout经过鉴相器输出相位误差信号为0时,此时可逆计数器进行加计数和减计数的周期相同,因此不会产生进位或借位脉冲,仅对其时钟进行二分频;反之当锁相环没有锁定时,如果误差信号er为低电平时,表示fin和fout时钟极性相同,此时计数器进行加计数,当可逆计数器到达Kset预设模值时,表示输出信号超前,输出减脉冲信号,可逆计数器复位为k值设置状态;当误差信号er为高电平时,表示fin和fout时钟极性相反,可逆计数器每周期减1,当可逆计数器到达0时,表示输出信号滞后,输出增脉冲信号,可逆计数器复位为k值设置状态;从而实现了环路滤波的功能。主要代码如下所示:

4.3 Nlength模块的设计

4.4 FBCounter模块的设计

数控振荡器主要组成部分由输出频率稳定的时钟源、计数器和比较器构成,输出取样脉冲序列,由数字环路滤波器输出的校正电平信号控制。

对于数控振荡器功能模块的设计,主要根据环路滤波器功能模块给出的借位标志信号(ba)、进位标志信号(fo)对输出脉冲序列进行调整。当借位标志信号(ba)为高时,加减计数器模块少输出一个脉冲,从而降低输出频率;当进位标志信号(fo)为高时,加减计数器模块多输出一个脉冲,从而提高输出频率;当这两个信号为低时,加减计数器模块对时钟进行二分频输出,具体实现硬件结构如图4所示。

图4 FBCounter模块硬件结构

4.5 Ndivider模块的设计

该模块为除N的计数器,用于对上级模块输出的脉冲信号(cout)在系统时钟下进行分频,由于fout=clk/2N=fc,故通过改变N值得到相应的环路中心频率fc,同时得到输出信号fout。

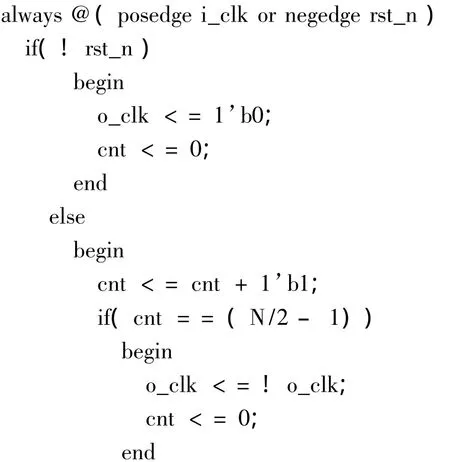

分频器的实现原理主要是通过对计数器进行计数,到达分频的一半时时钟进行翻转达到分频的目的,2N分频器主要用于对时钟信号进行偶数分频,例如2分频、4分频、8分频和16分频。主要代码如下所示:

4.6 测试结果及分析

使用QuartusII软件对设计进行综合、布局布线,得到最终下载至FPGA的bit流,进行下载测试。整个锁相环系统占用芯片逻辑资源的5%(5980个LE单元),占用I/O管脚11%(185个管脚),在EP1C6 FPGA中仅占用了少量资源,并且时序条件满足,完全可以达到高动态数字锁相环的要求。实验测试选择的FPGA型号是在现有应用条件下选择,只要内部资源满足使用,当然选用成本越低的芯片越好,同时需考虑资源余量以便功能升级测试使用。

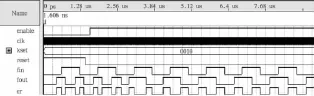

如图5所示为采用QuartusII软件进行时序仿真,通过对整个锁相环源程序进行仿真后,发现本设计基本符合预定要求。仿真图中可以看到系统会自动对输出信号fout进行调节,使其在很短的几个周期时间内既可以跟上输入fin的频率,相位差值固定,快速达到同步状态,实现锁相功能。

图5 数字锁相环时序仿真

5 结论

本文主要就数字锁相技术进行了研究,在本设计中,以Altera公司的EP1C6Q240芯片作为测试系统的核心器件,采用Verilog语言编程实现了高动态数字锁相环设计方案。经过实际测试,完全能够满足实际使用,具有很高的兼容性和应用价值。

[1]黄良沛,罗忠诚.利用锁相环实现大功率电机变频转工频的研究[J].电气应用,2005,(02):95-97,104.

[2]朱明亮,吴成柯,李云松.基于数字锁相技术的视频同步显示[J].电视技术,2006,(12):43-45.

[3]余发强,徐东明,张云军.应用于CDR电路的DPLL设计与实现[J].科技信息,2010,(01):78-79.

[4]王福昌,鲁 昆.锁相技术[M].武汉:华中理工大学出版社,1997.

[5]沈 军,郭 勇,李志鹏.基于FPGA的DPLL设计与仿真实现[J].微计算机信息,2007,(14):201-203.