AD9230在中频数字系统中的应用

2011-05-08胡广洲王锦石鲍庆鹏李浩茹

胡广洲 王锦石 鲍庆鹏 李浩茹 王 娟

(东北石油大学华瑞学院,黑龙江 哈尔滨 150027)

随着数字信号处理技术的不断发展和芯片处理速度的不断提高,采用数字中频技术的方案越来越成熟。中频数字接收机主要由ADC,FPGA组成。其中ADC是模拟和数字信号处理的桥梁,在很大程度上决定了系统的整体性能。传统模数转换电路已难以满足系统对采样精度、速率的要求,针对这种情况,本文提出一种新的解决方案,采用AD9230给系统提供高质量的采样精度及速率。

1 高性能模数转换器AD9230

本系统要处理五路中频信号,采样精度为12bit,需采样速率为200MHz。考虑到系统结构对器件尺寸的要求及采样精度、速率的要求,本系统选用了ADI公司生产的12bit单通道高性能、低功耗和容易使用的模数转换器AD9230。该产品转换速率高达250MSPS,为宽带载波和宽带系统提供杰出的动态性能。[1]

它在单芯片内集成了包括跟踪保持(T/H)和基准电压等所必需功能以提供完整的信号转换解决方案。在1.8V电源供电下,它的功耗仅有425mW。AD9230需1.8V模拟和数字电源电压以及一个差分时钟支持全部功能。其数字输出与LVDS(ANSI-644)兼容,它还可提供数据时钟输出以适合输出数据定时。

AD9230还含有内置基准电压源和采样保持,两个并行低压差分信号(LVDS)输出模式容易与现场可编程门阵列(FPGA)连接以及双数据速率模式(DDR)将需要的并行输出数据印制线数量减半。使用DCO来为输出数据提供时钟,帮助捕捉AD9230的数据,它等于采样时钟速率。在单数据速率模式(SDR),数据必须在DCO上升沿获取。在双数据速率模式(DDR),数据必须在DCO下降沿获取。SDR为默认模式,通过设置寄存器0x14<3>可以对DDR进行配置。

2 AD9230外围电路的设计

中频数字接收机采用的是射频直接带通采样,然后把数据送入FPGA中,采样后的数据经过FPGA的后续处理,计算出I、Q量。数字电路软件具有可编程的灵活性,可现场编程。整个硬件系统仅采用一片FPGA来处理,并采用五片单通道A/D芯片同时同步采样的运行模式。其中FPGA为主控芯片,通过FPGA对整个系统进行通信和控制,大大提高了系统的运行速度。主要器件型号为:

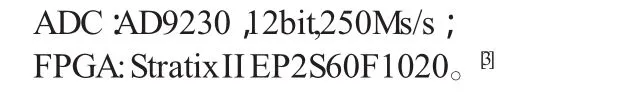

由于AD9230的输入信号要求是差分信号,这样就需要一种能将信号转换成差分信号的电路。如图1所示。

使用一个宽带变压器、匹配电阻及耦合电容的电路,能够较好的保持高速ADC的高动态范围,同时又使增益突起和带宽降低效应减至最小。

图1 ADT1-1WT连接电路图

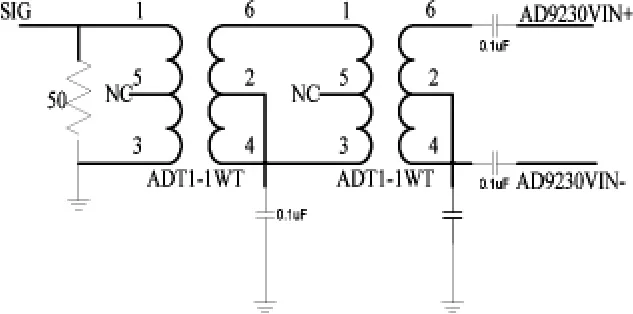

AD9230对模拟输入的采样是在时钟输入的上升沿进行的,为获得最佳性能,AD9230采样时钟输入(CLK+和CLK-)应采用差分信号。这里采用出色防抖动性能的AD9516系列时钟驱动器AD9230提供差分时钟信号。电路如图2所示。[2]

图2 差分PECL采样时钟

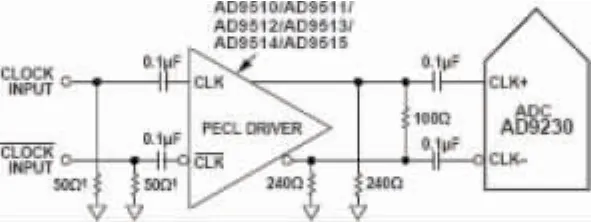

AD9230具有一个占空因数稳定器(DCS),可以对未采样的边沿重新计时,为内部时钟信号提供额定的50%占空因数。这样可以提供宽泛的时钟占空因数而不影响AD9230的性能。当启动DCS时,噪声和失真性能几乎是平坦的。根据系统的要求具体电路连接如图3所示。

图3 AD9230外围电路连接图

AD9230需要用户在RBIAS引脚和地面之间放置一个10千欧姆电阻。该电阻应具有百分之一的容差,用于设置ADC内核的主电流参考。

PWDN芯片掉电引脚。通过使PWDN为高,AD9230处于待机模式或关电模式。重置PWDN使之为低可使AD9230回到正常的运行模式。

SCLK/DFS(串行时钟)用于时ADC呈现的读写数据同步。SDIO/DCS(串行数据输入/输出)为一个双向引脚,允许数据发送或从内部ADC内存地址寄存器读取数据。

CSB为有效的控制,可启动或禁止读写周期。

RESET器件复位。

CML引脚提供一个优化内部偏置电压的参考基准。

3 测试结果分析

3.1 时钟抖动对ADC信噪比的影响

测试时钟对ADC的性能影响,我们需要获得输出信号的SNR。利用Altera公司Quartus软件中的SignalTap模块经过JTAG接口在FPGA中抓取ADC输出的实际数字信号。SignalTap是一种嵌入式逻辑分析仪,系统级软硬结合的调试工具,能够获取、显示可编程片上系统(SOPC)的实时信号,易于观察硬件和软件的交互作用,实现更高的精度。通过我们的实践证明,在FPGA上用这种方法抓取数字信号更便捷,更准确。

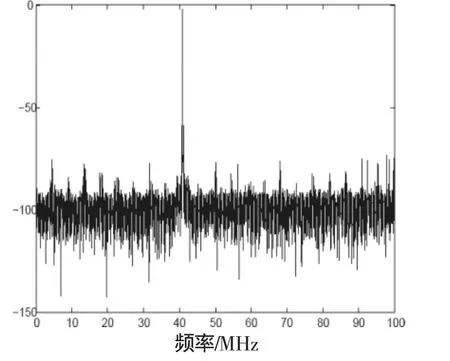

将抓取的ADC实际数据导入到MATLAB中,对数据进行处理得到ADC输出数字信号的幅频特性,如图4所示。

图4 ADC输出数字信号的幅频特性

输入信号频率为150MHz,由图可知,SNR约为65.87dB,满足系统要求。

结束语

通过对ADC相应参数的测试,证明AD9230的采样精度以、速率及其他参数性能良好。相信不仅在中频数字接收机中,对于其他用到高速ADC的系统如数据通信、测量测试等领域,这种解决方案也具有很好的应用前景。

[1]AD9230AnalogDevicesHandbook.2007.

[2]AD9516AnalogDevicesHandbook.2007.

[3]Altera公司.DataBook,2004.