LMS自适应滤波器的FPGA实现

2011-04-12陈昌孝何明浩申正义王志斌

陈昌孝 何明浩 申正义 王志斌

(空军雷达学院信息对抗系 武汉 430019)

0 引 言

随着大规模集成电路设计技术和制造工艺的不断进步,现场可编程门阵列(FPGA)目前已经进入45nm时代,随着其包含功能的不断扩展,现代的FPGA不仅包含有大量的逻辑和布线资源,而且还包含有许多高性能的专用功能单元,如:PowerPC440处理器、PCIe接口控制器、GMAC控制器、专用DSP处理单元以及高达6.5G的高速串行传输接口等.同时,FPGA所具有的静态可重复编程和动态系统可重构特性,使得硬件的功能可以像软件一样通过编程来修改,极大地提高了电子系统设计的灵活性和通用性,缩短了产品的上市时间并降低了电子系统的开发成本[1].

自适应滤波器的设计与实现一直是信号处理领域的研究热点之一,已经被广泛应用于通信、语音、图像处理、生物医学和工业控制等领域[2].长期以来,自适应滤波算法大多基于DSP芯片,利用汇编或高级语言程序代码来实现,这种方式在对实时性要求不高的场合能很好的满足性能要求,但在实时性要求较高以及电磁环境较恶劣的场合,这种方式在处理速度和抗干扰性能等方面已无法满足需要.

本文正是在此基础上提出一种软硬件协同完成LMS自适应算法的系统架构,可以同时满足系统的灵活性与实时性的要求.

1 自适应滤波与LMS算法

自适应滤波的基本原理如图1所示.

图1 自适应滤波的基本原理

其基本功能为:在部分信号特征未知的条件下,根据某种最佳准则,从已知的部分信号特征决定的初始条件出发,按某种自适应算法进行递推,在完成一定次数的递推之后,以统计逼近的方式收敛于最佳解.当输入信号的统计特性未知,或者输入信号的统计特性变化时,自适应滤波器能够自动地迭代调节自身的滤波器参数,以满足某种准则的要求,从而实现最优滤波.因此,自适应滤波器具有自我调节和跟踪能力,在非平稳环境中,自适应滤波可以很好地跟踪信号的变化.调节和跟踪能力,在非平稳环境中,自适应滤波可以很好地跟踪信号的变化.

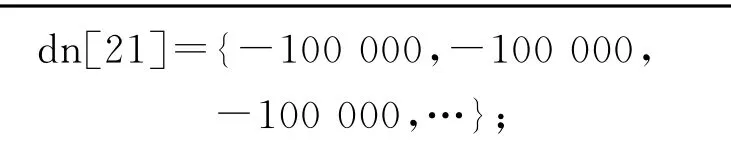

滤波器的输出由式(1)给出

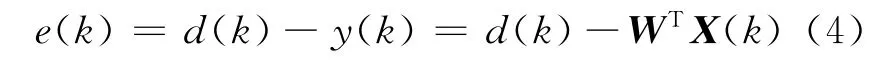

误差信号为

W的叠代公式为

μ值的取值范围为:0<μ<1/λmax.μ越大,收敛越快,但容易振荡;μ值小,收敛慢,但比较平稳.

2 算法的硬件实现

2.1 SOPC解决方案简介

本文采用基于FPGA的SOPC(system on a programmable chip)系统作为自适应滤波器的硬件实现平台,并行运算代替常规的DSP程序串行算法,不仅提高了系统的响应速度,而且有很强的抗干扰能力.SOPC采用Xilinx公司的一种灵活、高效的SOC 解决方案[3].MicroBlaze CPU[4-10]是一种采用流水线技术、单指令流的RISC处理器,其大部分指令可以在一个时钟周期内完成.MicroBlaze处理器又是一种软核CPU,专门针对Xilinx的可编程逻辑器件,以及片上可编程系统的设计思想做了相应优化.作为一种可配置的通用RISC处理器,它可以与用户自定义逻辑结合构成SOC系统,并下载到Xilinxd的可编程器件中去,结合外部闪存,以及大容量存储器,可构成一个功能强大的32位嵌入式处理器系统.系统框图见图2.

图2 LMS算法的系统实现方案

2.2 设计实现

1)MicroBlaze子系统的设计和实现.MicroBlaze子系统的设计相对简单,只需将x(n)和d(n)存在数组中,进行这样的操作循环:(1)向FSL总线写x(n);(2)向FSL总线写d(n);(3)向FSL总线写μ(n);(4)从FSL总线读e(n).

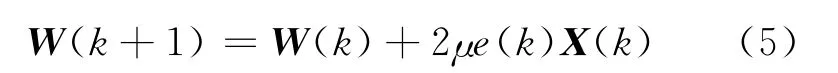

2)LMScore子系统的设计和实现.通过改进FSL总线外设为一个LMS核,完成框图中所述的任务.LMS外设核的状态机状态转换见图3.

图3 LMS核的状态转移图

为了实现所需的自适应滤波器的功能,所设计FSL总线外设的时序如表1所列.

表1 FSL总线外设的时序设计

3 试验结果

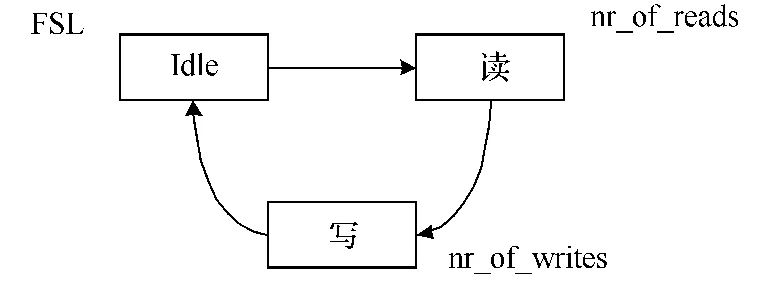

假设使用21个输入x(n)和期望值d(n).

测试数据1:

第二组测试数据:

使用matlab程序画出图形(e(n)使用指数坐标),得到结果见图4.

可见,在期望输出为恒定值,输入为恒定值,初始误差较大的前提下,e(n)基本上是指数趋势收敛的.

图4 测试1、测试2中误差的变化(指数纵坐标)

4 实际设计中的问题考虑

4.1 系统扩展性测试

由于设计试验平台的硬件限制,在Spartan开发板 上只实现了1阶(b0,b12个抽头系数)滤波器.那么这样的设计有没有可能在硬件资源更强大的系统中实现呢?为此,对扩展到8阶的系统进行ISE环境中的行为仿真:设输入为x(n)=1,1,1,1,1,…;期望输出为d(n)=5 000,5 000,5 000,5 000,5 000,…抽头系数初始值为:b0=7;b1=17;b2=32;b3=46;b4=52;b5=46;b6=32;b7=17;b8=7.这样的初始值是一个满足线形相位特性的低通滤波器.得到的仿真波形见图5.

图5 8阶系统的行为仿真波形

画出误差的变化趋势如图6所示(由于e(n)出现了负数,不再使用指数坐标).

图6 8阶系统误差变化

可见,误差较快的收敛到4和-5之间循环.所有的抽头系数都能够自适应的更新.可见,这个设计具有扩展的潜力,但是需要优化时序设计和资源使用.

4.2 硬件实现的折衷

在实际设计中,由于设计本身存在的问题以及Spartan3硬件资源的限制,采用了如下的折衷方案.

1)全部计算使用整数(包括自然数,负数,零),排除使用小数.

2)LMS核的主要操作数据b0,b1,…,y(n),d(n),e(n)均使用integer数据类型.

3)在verilog描述中直接使用*作为乘法运算符,不使用IP库.

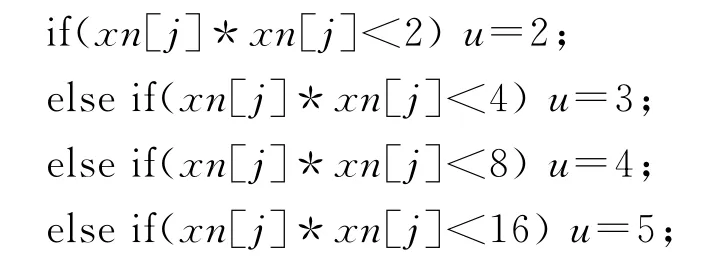

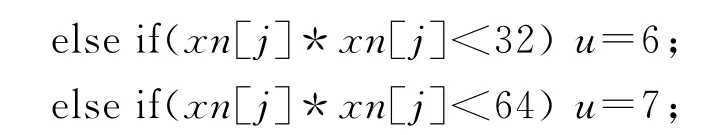

4)在进行μ(n)归一化时,传到总线上的数据不使用带有小数的μ(n)=μ0/|x(n)|2,而是在MicroBlaze端根据x(n)的值进行估计,将乘法转换为一个移位操作 .在MicroBlaze端,可以假设所有输入x(n)均为自然数,进行这样的估计:

由于设计存在的时序问题和乘法器的综合占用了较多的系统资源,虽然在行为仿真中可以实现较高阶数的滤波,在实际的硬件中只实现了2个抽头的1阶滤波.

5 结束语

自适应滤波器的硬件实现一直是数字滤波器研究的热点,本文采用基于FPGA的SOPC系统作为自适应滤波器的硬件实现平台,实现了LMS算法的自适应滤波陷波器,实验结果表明,该平台达到了自适应滤波算法所要求的准确性和实时性,并且与单独采用数字信号处理实现的系统相比,具有更快的执行速度、抗干扰能力和配置的灵活性,与采用分立芯片的DSP+FPGA方案相比,集成度更高,开发调试更加快速,成本相对低,是自适应滤波器硬件实现方式的发展趋势之一.

[1]Haykin S.Adaptive filter theory[M].fourth ed.Beijing:Publishing House of Electronics Industry,2003.

[2]任爱锋,初秀琴.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004.

[3]Chang Choo.An embedded adaptive filtering system on FPGA[DB/OL].Prasannalakshmi Padmanabhan,Susmita Mutsuddy Department of Electrical Engineering,San Jose State University.http://www.engr.sjsu.edu/choo/gspx06chooetal.pdf.

[4]Spartan-3starter kit board user guide[Z].Xilinx,Inc.UG130(v1.1),May 2005.

[5]Embedded system tools reference manual[Z].Xilinx,Inc.UG111(v3.0),Aug2008.

[6]MicroBlaze processor reference guide[Z].Xilinx,Inc.UG081(v4.0),Aug 2008.

[7]Platform studio user guide[Z].Xilinx,Inc.UG113,Aug 2008.

[8]Rosinger H P.Connecting customized IP to the microBlaze soft processor using the fast simplex link(FSL)channel[Z].XAPP529,May 2004.

[9]Fast simplex Link(FSL)bus(v2.00a)[Z].Xilinx,Inc.DS449,Aug 2008.

[10]皇甫堪.现代数字信号处理[M].北京:电子工业出版社,2010.