基于FPGA的100BASE-TX工业以太网中继器的设计与实现

2011-03-28周学勋

周学勋

(南车时代电气技术中心,湖南株洲412001)

以太网中继器是连接网络线路的一种装置,常用于两个网络节点之间物理信号的双向转发工作。由于存在损耗,在线路上传输的信号功率会逐渐衰减,衰减到一定程度时将造成信号失真,因此会导致接收错误,中继器就是为解决这一问题而设计的。中继器是最简单的网络互联设备,负责在两个节点的物理层上传递信息,完成信号的复制、调整和放大功能,以此来延长网络的长度。

1 系统架构

以太网中继器采用专用以太网物理层PHY芯片来实现以太网接口部分,控制部分采用FPGA来实现,PHY芯片和FPGA采用MII接口相连接,其系统功能框图如图1所示。

图1 系统功能框图Fig.1 Block diagram of system function

以太网中继器用来对以太网物理层的信号进行双向转发。如图1所示,当以太网接口1接收到数据时,模拟数据信号由双绞线从以太网接口1的M12连接器进入隔离变压器,经过变压器的隔离后进入PHY芯片,滤波,整形,4B/5B解码,从MII(Media Independent Interface)变为4位数据并行输出,进入FPGA。FPGA进行以太网MAC帧的检测与再生后以4位并行数据输出到以太网接口2的PHY芯片的MII接口,并行数据经过PHY芯片的4B/5B编码,转化为MLT3[1](多电平传输)格式模拟信号,预整形,发送到隔离变压器,信号经变压器隔离后,输出到M12连接器。当来自以太网接口2接收到数据时,模拟数据信号由双绞线从以太网接口2的M12连接器进入隔离变压器,经过变压器的隔离后进入PHY芯片,滤波,整形,4B/5B解码,从MII(Media Independent Interface)变为4位数据并行输出,并行信号进入FPGA。FPGA进行以太网MAC帧的检测与再生后以4位并行数据输出到以太网接口1的PHY芯片的MII接口,并行数据经过PHY芯片的4B/5B编码,转化为MLT3(多电平传输)格式模拟信号,预整形,发送到隔离变压器,信号经隔离变压器,到M12连接器。由于所设计的中继器设置为100 M全双工方式,所以对于PHY芯片来说,双向数据转发过程相互独立,互不影响。

2 逻辑实现

IEEE802.3标准[2]规定一个完整的MAC帧包括7字节的同步码(10101010)、一个字节的帧起始标志符(10101011)、6个字节的目的地址、6个字节的源地址、2个字节的数据长度、46~1500字节的数据和4字节的校验码等字段组成。完整的以太网帧如图2所示。

图2 IEEE 802.3以太网帧格式Fig.2 Ethernet frame format based on IEEE 802.3

MII接口主要包括4个部分[3]:一个是从MAC层到PHY的发送数据接口;二是从MAC层到PHY层的接收数据接口;三是从物理层到MAC层的状态指示信号;四是MAC层和物理层之间传送控制和状态信息的MDIO接口,在本中继器的设计中,MDIO接口无需使用。PHY芯片端的各信号定义如表1所示(对于FPGA一端,信号定义相同,方向相反)。

表1 信号定义Tab.1 Signal definition

IEEE802.3标准允许PHY芯片在接收以太网帧时,丢失一部分同步码,因此FPGA必须将来自某一个以太网接口PHY芯片MII接口的以太网帧进行帧同步码和帧起始标志符的检测与恢复再生,并将再生的帧同步码和帧起始标志符以及数据实时转发给另外一个端口。由于中继器是双向数据转发,因此在FPGA内部设计了两套完全相同的子模块,分别用于各自方向的转发。FPGA实现这一功能的功能框图如图3所示。

2.1 同步检测模块

同步检测模块负责对来自PHY芯片MII接口的RXD[3:0]数据进行同步信息的提取和帧起始标志符(SFD)的识别,并将帧起始标志符之后的有效数据暂存到双口RAM中。由于中继器只是物理层的设备,因此无需对所接收到的数据进行CRC校验,所以在设计同步检测模块时,将图2所示的以太网帧目的地址字段及该字段以后的所有字段都认为是有效数据。

图3 FPGA功能框图Fig.3 Function block diagram of FPGA

同步检测模块状态转换图如图4所示:

1)当中继器上电开始工作,状态机初始化为IDLE状态。

2)当来自某一以太网接口PHY芯片的MII接口信号RXDV信号有效时,表示需要接收以太网帧,状态机转换到检测以太网帧同步码及起始标志符状态。当检测到非“1010”或“1011”时,返回到IDLE状态,放弃当前帧传输,等待下一帧。

3)当检测到以太网帧同步码及起始标志符后,进入帧有效数据存储状态,将帧有效数据存储到FPGA内部双口RAM中。

4)当检测到RXDV信号无效后,表示帧数据已经接收完毕,状态机跳转到IDLE状态,等待接收下一帧数据。

2.2 同步再生模块

同步再生模块负责提取双口RAM中的有效数据,并在有效数据前添上新的帧同步码和起始标志符,增加新的同步信息。

同步再生模块状态转换图如图5所示。

1)当中继器上电工作后,状态机初始化为IDLE状态。

2)当接收状态机检测到帧起始标志符“10101011”后,就置TXEN信号有效,发送状态机转换到发送以太网帧同步码“10101010”状态及发送以太网帧起始标志符“10101011”状态。

3)当发送完以太网帧起始标志符“10101011”后,转换到发送有效数据状态。读取双口RAM中的数据,并同步发送。

图5 发送状态机Fig.5 Send state machine

4)当发送完有效数据后,置TXEN信号无效。状态机跳转到IDLE状态,等待下一帧的发送。

2.3 双口RAM模块

双口RAM模块负责暂存帧有效数据及数据交互。在FPGA从某一以太网端口接收数据时,在控制模块的控制下将接收到的数据存储到双口RAM中,当发送使能信号TXEN有效时,由控制模块将双口RAM中的数据读出,从输出端口输出。双口RAM采用调用Xilinx成熟的IP核来实现,它具有2套可读可写的RAM(A和B),RAMA与接收端的数据及控制信号相连,RAMB与发送端的数据及控制信号相连,RAM只做数据的输入,RAMB只做数据的输出。由于以太网最大帧长度为1 518个字节,所以必须将双口RAM的地址深度须设为3 k,以保证有足够的容量来缓存一帧以太网数据;而PHY芯片MII接口的数据信号为4 bit的并行数据,因此双口RAM的数据线宽度设为4 bit。因为中继器的数据传输是双向的,所以在FPGA里面设置两个相同的双口RAM,使两个方向相互独立,各自存储自己所负责方向的帧有效数据。

2.4 控制模块

控制模块用于控制同步检测模块和同步再生模块的工作,产生满足PHY芯片的相应时序,并控制双口RAM的读写时序,是整个中继模块FPGA程序的核心。当同步检测模块检测到帧起始标志符后,向控制模块发出一个preamble_en信号,报告已经检测到帧起始分解符,控制模块收到该信号后,启动双口RAM的写控制,将同步检测模块接收到的4位并行数据存储到双口RAM中,同时置发送信号TXEN有效,通知同步再生模块启动发送数据过程,同步再生模块收到TXEN信号后,开始生成帧同步码和帧起始标志符并发送,帧起始标志符发送完毕后,通知控制模块启动双口RAM的读控制,将双口RAM中的有效数据读出并紧随着帧起始标志符发送出去。在整个数据通信过程中,控制模块检测各种出错指示信号,一旦接收或发送出错信号有效,则立即停止当前数据的传输,等待下一帧数据的传输。

3 功能验证

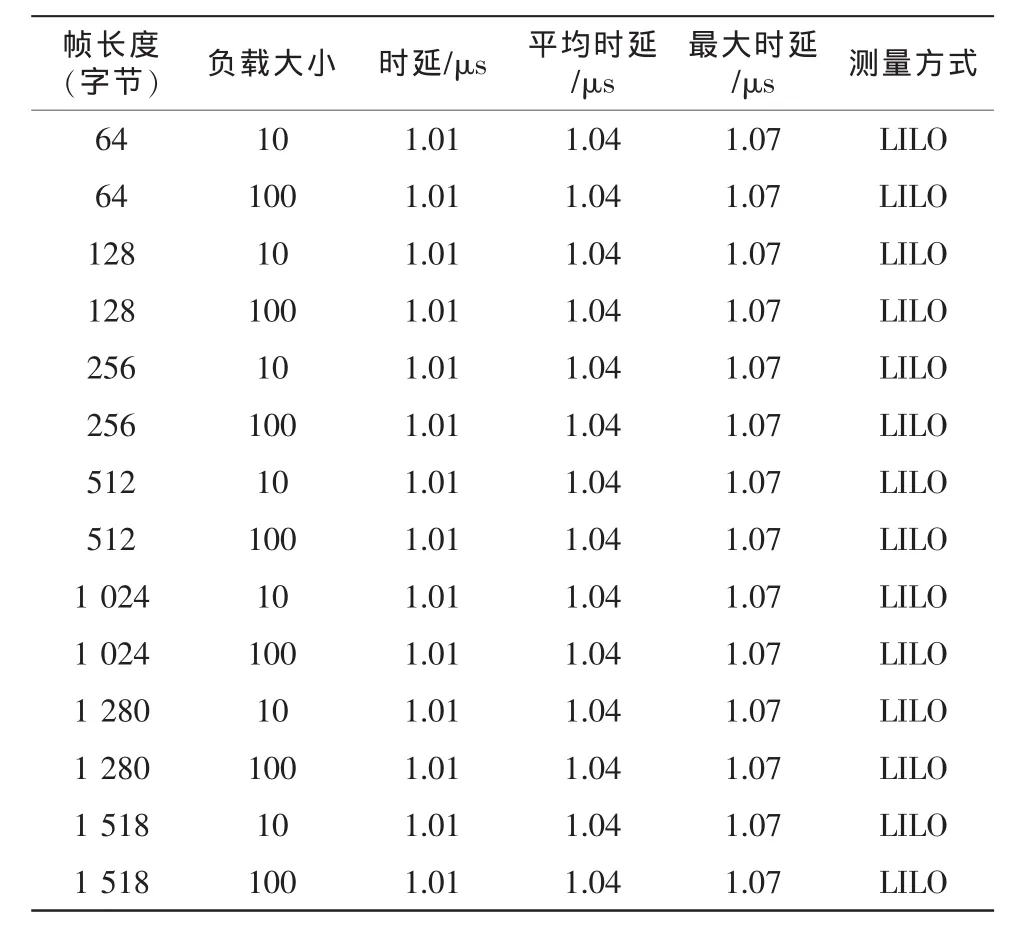

为了验证所设计的以太网中继器的性能,按照RFC2544标准[4]对其进行性能测试。主要测试其延时性能。而RFC1242标准[5]中对延时定义如下:对于存储转发设备来说,当输入帧的最后一位到达输入端口时,时间间隔开始计算,当输出帧的第一位在输出端口上可见时,时间间隔计算结束;对于按位转发设备来说,当输入帧的第一位到达输入端口时,时间间隔开始计算,当输出帧的第一位在输出端口上可见时,时间间隔计算结束。中继器属于按位转发设备,因此测量时,需选取LILO方式。使用专业的网络测试仪,对中继器进行测试,测得的时延指标如表2所示。

表2 测试结果Tab.2 Test results

从表2的测试结果来看,中继模块的平均时延稳定在1.04 μs,不随帧长度大小和流量大小改变而改变。

4 结束语

本文通过对以太网物理层通信过程进行分析,设计了一种基于FPGA的工业以太网中继器,给出了中继器的总体设计方案,并详细介绍了FPGA的算法及实现过程,最后通过专业的以太网测试仪对所设计的以太网中继器进行测试,验证了该中继器的性能,满足设计要求。

[1] 冯永茂,徐秀知,陈宇,等.基于快速以太网物理层的实时高速数字视频传输[J].电子器件,2007,30(1):144-147,151.FENG Yong-mao,XU Xiu-zhi,CHEN Yu,et al.Real time high speed digital video transmission with fast ethernet PHYs[J].Chinese Journal of Electron Devices,2007,30(1):144-147,151.

[2] LAN/MAN Standards Committee,IEEE Std 802.3.Carrier sense multiple access with collision detection(CSMA/CD)access method and physical layer specifications[S].New,2005.

[3] 许俊,林水生.基于FPGA的以太网MII接口扩展设计与实现[J].电子设计应用,2005(5):110-113.XU Jun,LIN Shui-sheng.Implementation of Ethernet MII based on FPGA[J].Electronic Design and Application World,2005(5):110-113.

[4] The Internet Society,RFC2544.Benchmarking methodology fornetwork interconnect devices[S].1999.

[5] The Internet Society,RFC1242.Benchmarking terminology for network interconnection devices[S].1991.

[6] 王廷尧.以太网技术与应用[M].北京:人民邮电出版社,2005.