基于FPGA的罗兰C前端IIR数字带通滤波器设计

2011-03-28李靖宇李豹曹可劲瞿洋

李靖宇,李豹,曹可劲,瞿洋

(1.海军工程大学导航工程系,湖北武汉430033;2.海军91821部队广东潮州515700)

罗兰C系统是我国独立控制的唯一大型陆基无线电导航系统,是我国卫星导航定位授时(PNT)的重要备份手段,是全球罗兰C系统网的重要组成部分。其工作频率为90~110 kHz[1]。由于其工作在低频段,存在水下接收的可能,近年来,利用磁天线接收罗兰C信号实现水下隐蔽定位成为研究热点[2]。而射频前端的数字带通滤波器是实现数字化实时处理接收机的重要部分。针对这些需求,笔者提出了采用级联形式在FPGA上通过Verilog语言编程实现罗兰C数字带通滤波器的方法。在经典滤波器中,IIR数字滤波器具有很高的滤波效率,所需的阶数不仅比FIR滤波器低,而且可以利用模拟滤波器的设计成果[4]。在对信号的相位要求不是很高时可以使用IIR滤波器,用级联形式设计的IIR滤波器的工作量相对较小,而且所用存储单元少,经济效益高。

1 利用MATLAB综合函数设计IIR带通滤波器

1.1 IIR滤波器结构

IIR滤波器是一种递归滤波器,具有反馈结构,如图1所示。

图1 IIR滤波器直接型结构Fig.1 The direct structure of IIR filter

其系统差分方程可描述为:

其系统传递函数描述为:

可以对IIR数字滤波器的传递函数H(Z)进行分子,分母的多项式分解,这样就可以得到其级联形式,级联形式结构如图2所示。

图2 IIR滤波器级联结构示意图Fig.2 The cascaded structure of IIR filter

其中,每一级的二阶子系统的传输函数形式为:

级联形式具有一定的独立性,极点与零点的组合以及Hk(z)的连接顺序等具有相当大的自由度。与直接型结构相比,对系数敏感度低的滤波器,不容易受系数误差影响的滤波器更适合采用级联型结构。级联结构在硬件实现中可以共用存储器和延迟单元,减少所需元件数量,简化结构[4]。

1.2 IIR 滤波器的MATLAB实现

利用MATLAB综合函数可以很容易地求出满足要求的带通滤波器参数。

其中wp和ws分别为通带截止频率和阻带截止频率,由于是带通滤波器所以两个都应该为二维向量。Rp和Rs分别为通带最大衰减和阻带最小衰减。wn为3 db边缘频率,此亦为二维向量。B和A即为式(2)中的分子,分母的系数向量。即:

A=[1,α1,…,αN];B=[b0,b1,…,bM](5)

求出滤波器参数B,A之后可以利用MATLAB函数将其转化成级联形式:

[sos,g]=tf2sos(B,A);

此例中产生的sos为一个4×6的矩阵:g=0.000 001 274 722 974;滤波器增益。

每行为一个二阶子系统的参数,对应为:[bk0,bk1,bk2,1,ak1,ak2],k=1,2,3,4;

由于最终要采用FPGA硬件实现,为了使设计简便及资源得以充分利用,应该对系数进一步的量化,将系数由小数转化为整数,根据需要主要考虑量化精度和系统资源两方面,本文采用将二阶网络系数乘以2N(N=5)并取整实现[8]。

2 参数取整后对滤波性能的影响分析

由于参数取整处理带来的舍入误差会对滤波器的零点,极点造成影响,从而影响滤波器的稳定性。因此有必要将参数取整后的级联方式转回标准形式,再利用MATLAB综合函数对其滤波效果进行测试。如果滤波效果不能满足要求,即取整舍入误差造成的影响较大,应将2的幂次升高,但如果2的幂次过高,势必会占用过多的硬件资源,因此要综合考虑,以满足滤波要求,且滤波器稳定工作为前提。

2.1 测试信号的设计

fs=1e6;采样率1 M;

t=0:1/fs:1e-3;时间1 ms

x=15*sin(2*pi*100e3*t)+15*sin(2*pi*115e3*t)+15*sin(2*pi*85e3*t);

x1=round(x);信号点取整。测试信号波形如图3所示:

图3 测试信号波形图Fig.3 The diagram of tested signal

测试信号采用3个不同频段的信号叠加产生,用此信号作为滤波器的输入信号,对滤波器的滤波效果进行测试,验证滤波器能否滤除频带外的信号。

2.2 滤波性能比较

为了方便利用MATLAB函数进行滤波性能比较,需将滤波器的级联形式化成标准形式,注意增益仍旧用g而不是G,表示滤波器的增益和原来取整之前的相等,便于幅频响应的比较。

[B1,A1]=sos2tf(S,g);

[h,w]=freqz(B,A,256,'whole',fs);

[h1,w1]=freqz(B1,A1,256,'whole',fs);

由图4可以看出,滤波器参数取整后的幅频响应曲线几乎和取整之前重合,证明参数乘以25再取整后的舍入误差对滤波器幅频响应的影响极小,可以忽略。

2.3 级联式差分方程的应用

硬件程序设计前,在MATLAB下写出级联形式的差分方程,模拟硬件程序的运算过程,验证算法的准确性,并可以观察运算过程中数值的大小,方便硬件设计中定义高效准确的数据位宽,提高设计的针对性与准确性。

图4 幅频响应比较图Fig.4 Comparison of amplitude frequency response

x2(1)=0;x2(2)=0;....x5(1)=0;x5(2)=0;差分方程初始化

for i=1:998

x_t=(S(1)*x1(i+2)+S(5)*x1(i+1)+S(9)*x1(i))/32;均匀分配增益,防止溢出

y_t=S(17)*x2(i+1)+S(21)*x2(i);

x2(i+2)=(x_t-y_t)/32;将参数a0归一化

...

x5(i+2)=(x_t3-y_t3)/32;

end

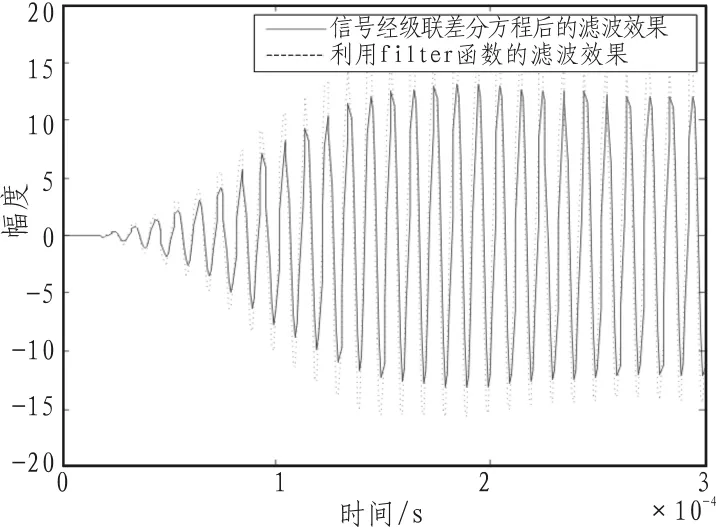

由图5可见在参数取整后用级联式差分方程模拟硬件程序滤波效果和调用filter函数的输出效果在波形上也几乎一致,只是由于增益上取整后的一点差异,信号幅度略有降低,对频域并无影响,且滤波器稳定,没有发散,由此可知上述取整满足设计要求,可以考虑下步硬件程序实现。

图5 滤波效果比较Fig.5 Comparison of filter performance

3 硬件程序实现及测试

Quartus是Altera公司在21世纪初推出的FPGA/CPLD开发环境,其优点是功能强大,界面友好,使用便捷,设计完成后还可以进行时序仿真。本例采用了在Quartus下自顶向下的工程设计,设计完成后进行了仿真测试。

3.1 建立工程和bdf文件

创立工程,在工程下建立bdt文件。如图6:U1模块为计数器模块,U2为ROM模块,ROM内部存储的初始值来自预先建立的mif文件,mif文件的初始值可以自行设定,作为滤波器的输入信号源,U3为带通滤波器模块。

图6 框图文件Fig.6 Block diagram file

3.2 Verilog程序编写

分别为各模块添加Verilog程序,其中ROM模块是调用的宏模块,可以自动生成.V程序。

U3模块的滤波器主程序:

module filter100k

(rst,clock,in,out,out1,out2,out3);

//Port Declaration

input clock;

...

output[15:0]out;

...

wire[15:0]y1_out;

...

//the first step parameter;

parameter b_1_0=32;

...

parameter a_1_0=32;

...

sub2

sub2_1(.clock(clock),.rst(rst),.a1_0(a_1_0),.a1_1(a_1_1),.a1_2(a_1_2),.b1_0(b_1_0),.b1_1(b_1_1),.b1_2(b_1_2),.x_in(in),.y_out(y1_out));

...

assign out2={out[15],out[6:0]};

end module

由于在sub2子程序设计中涉及到乘法和除法(移位)运算,需要将中间变量寄存器,输入和输位宽定义足够大,防止运算过程中产生溢出,但又要考虑到提高运算速度和硬件资源问题。为了有针对性的进行设计,可以在MATLAB的工作窗口中观察级联差分方程运算过程中中间变量值的大小,针对实际输入信号的幅度,准确高效地设置位宽。在FPGA硬件中,负数是用二进制补码表示,除法(移位)运算在移位过程中会影响到符号位,导致输出结果发生错误,所以移位过程中,应采取保留符号位进行移位。

3.3 建立矢量源文件进行仿真

工程编译成功后,建立一个矢量源文件(vwf)进行波形仿真。将实际采集的罗兰C信号存入mif文件,作为滤波器的输入信号。实际的滤波仿真效果如图7所示。

图7 实际采集罗兰C数据滤波仿真结果Fig.7 Simulation result of practical Loran Cdata

由图7可见,经过滤波器后可以从杂乱的采集信号中选择出清晰的罗兰C信号,说明滤波器设计满足要求。

4 结束语

本文以巴特沃斯带通滤波器为例,描述了IIR数字带通滤波器从MATLAB设计到FPGA实现的整个过程,避开了有限字长效应等复杂理论的讨论,从设计中遇到的一些关键性问题出发,在MATLAB下进行了滤波效果的仿真比较,最终在Quartus下用Verilog语言实现了滤波器的硬件程序设计,并用实际采集数据进行了滤波效果仿真。基于级联方式的IIR滤波器是较为容易实现的高效方式,当利用硬件实现滤波时,可以共用存储器和延迟单元,利于减少所需元件数量,可以简化结构,降低成本。同时代码简短,可大大节省滤波器设计时间。用这一方法设计的带通滤波器将用在利用磁天线接收水下信号的LoranC数字化接收机中。

[1] 吴苗,朱涛,李方能,等.无线电导航原理及应用[M].北京:国防工业出版社,2008.

[2] 崔国恒,曹可劲,许江宁,等.磁天线水下接收罗兰C信号可行性研究[J].弹箭与制导学报,2010,30(6):180-182.CUI Guo-heng,CAO Ke-jin,XU Jiang-ning,et al.The research on feasibility of receiving LoranC signal underwater based on H-field antenna[J].Journal of projectiles,Rockets,Missiles and Guidance,2010,30(6):180-182.

[3] 胡广书.数字信号处理[M].2版.北京:清华大学出版社,2003.

[4] 田耘,徐文波,张延伟.无线通信FPGA设计[M].北京:电子工业出版社,2008.

[5] 夏宇闻.Verilog数字系统教程[M].2版.北京:北京航空航天大学出版社,2008.

[6] 屈星,唐宁,严舒,等.基于FPGA的IIR数字滤波器的设计与仿真[J].计算机仿真,2009,26(8):304-308.QU Xing,TANG Ning,YAN Shu,et al.Design of digital filter based on FPGA[J].Computer Simulation,2009,26(8):304-308.

[7] 周润景,苏良碧.基于QuartusII的数字系统VerilogHDL设计实例详解[M].北京:电子工业出版社,2010.

[8] 童位理.基于FPGA的IIR数字滤波器的快捷设计[J].电子元器件应用,2007,9(5):36-40.TONG Wei-li.Shortcut design of IIR digital filter based on FPGA[J].Electronic Component&Device Applications,2007,9(5):36-40.