巧用卡诺图设计多输出组合逻辑电路

2011-03-23贵州电子信息职业技术学院电子工程系吴政江

贵州电子信息职业技术学院电子工程系 吴政江

我们知道,设计组合逻辑电路通常按以下步骤进行。第一,对实际问题进行逻辑抽象,并定义输入逻辑变量和输出逻辑变量;第二,根据所要实现的逻辑功能列真值表;第三,根据真值表求逻辑表达式,并根据所选用的门电路类型进行化简;第四,根据逻辑表达式画逻辑电路图。由于设计组合逻辑电路,通常以电路简单,所用的器件最少为目标,所以第三步化简就显得至关重要。而逻辑函数的化简又有公式法和卡诺图法两种。公式化简法比较繁琐,不仅需要记住大量的公式,而且化简的结果是不是最简的还无法判断。卡诺图化简法比较简单,容易掌握,而且只要填得正确,圈得正确,化简的结果就一定是最简的与或式。更有甚者,利用卡诺图之间的相互关系,可以方便地设计最简的多输出组合逻辑电路。在此,笔者以在“数字电子线路”教学中所用的课程设计过程来说明这一问题。

一、课程名称:八进制数字符号显示器

二、仪器及元器件选择

1.数字电路实验箱 1台

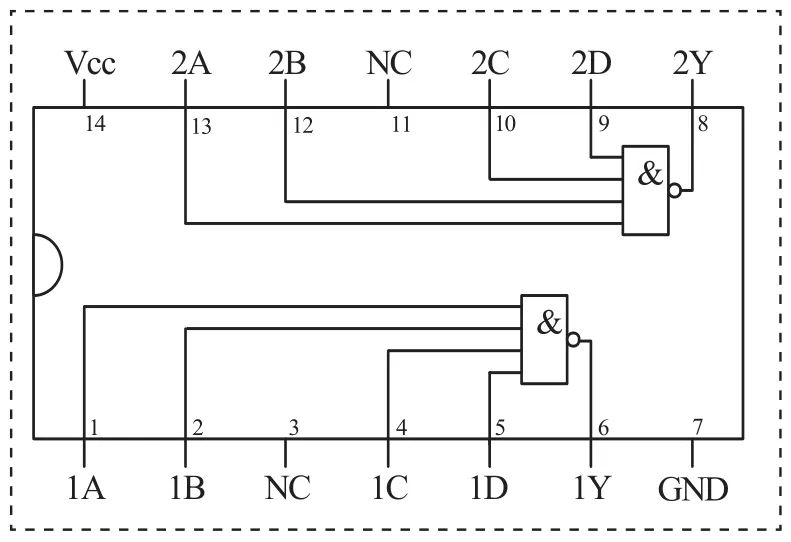

2.74LS20或T063(二-四输入与非门) 2块

3.SN7400或T065(四-二输入与非门) 最多6块

4.共阴极七段字形显示器 1块

5.导线 约60根

三、要求

1.输入:用八个逻辑开关K0~K7作逻辑符号输入。

2.输出:用共阴极七段字形显示器显示八进制数字符号0~7。

3.编码器:用T063,字形译码电路用T065。

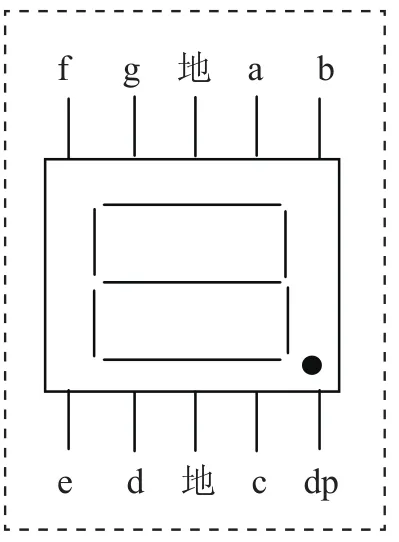

T063或74LS20、T065或SN7400以及共阴极七段字形显示器的内部结构及引脚排列分别如图1、图2和图3所示。

图1 74LS20(T063)内部结构与引脚排列图

图2 T065(或SN7400)内部结构与引脚排列图

图3 七段字形显示器

四、设计过程

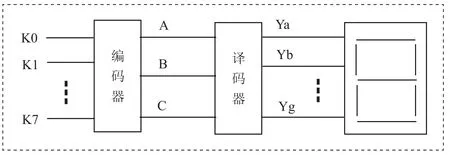

先用T063作编码器对8个开关信号K0~K7进行编码,输出为3位二进制数A、B、C,再用T065作字形译码器对A、B、C进行译码,最后用译码器输出驱动共阴极七段字形显示器显示8个八进制符号0~7。其结构框图如图4所示。设编码器输入高电平有效,则真值表如表1所示。由表1可得逻辑表达式:

表1 编码器真值表

图4 八进制数字符号显示器结构框图

可看成低电平有效,因而K0~K7不必加反相器。

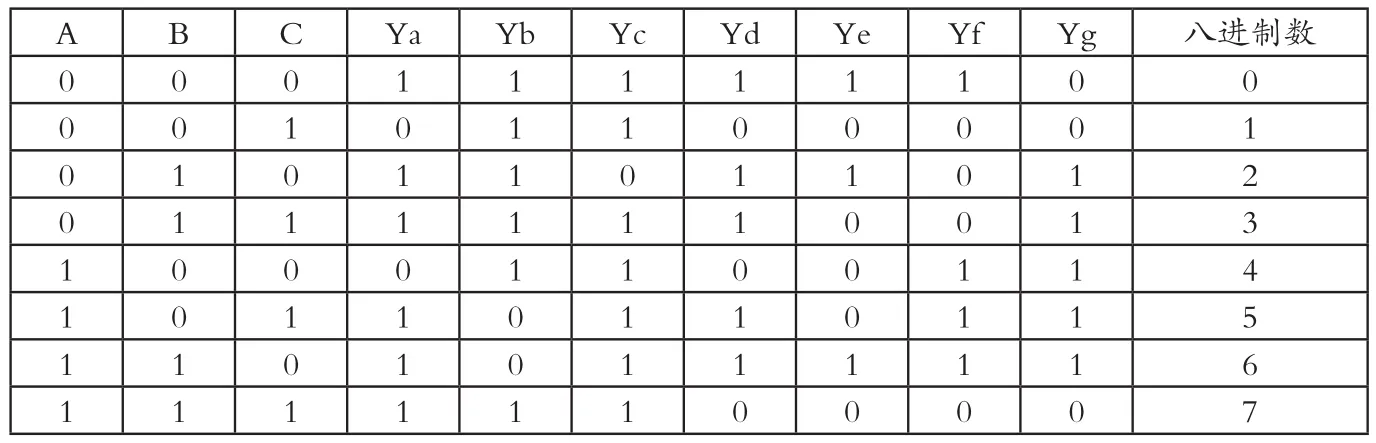

字形显示译码器真值表如表2所示。

表2 字形译码器真值表

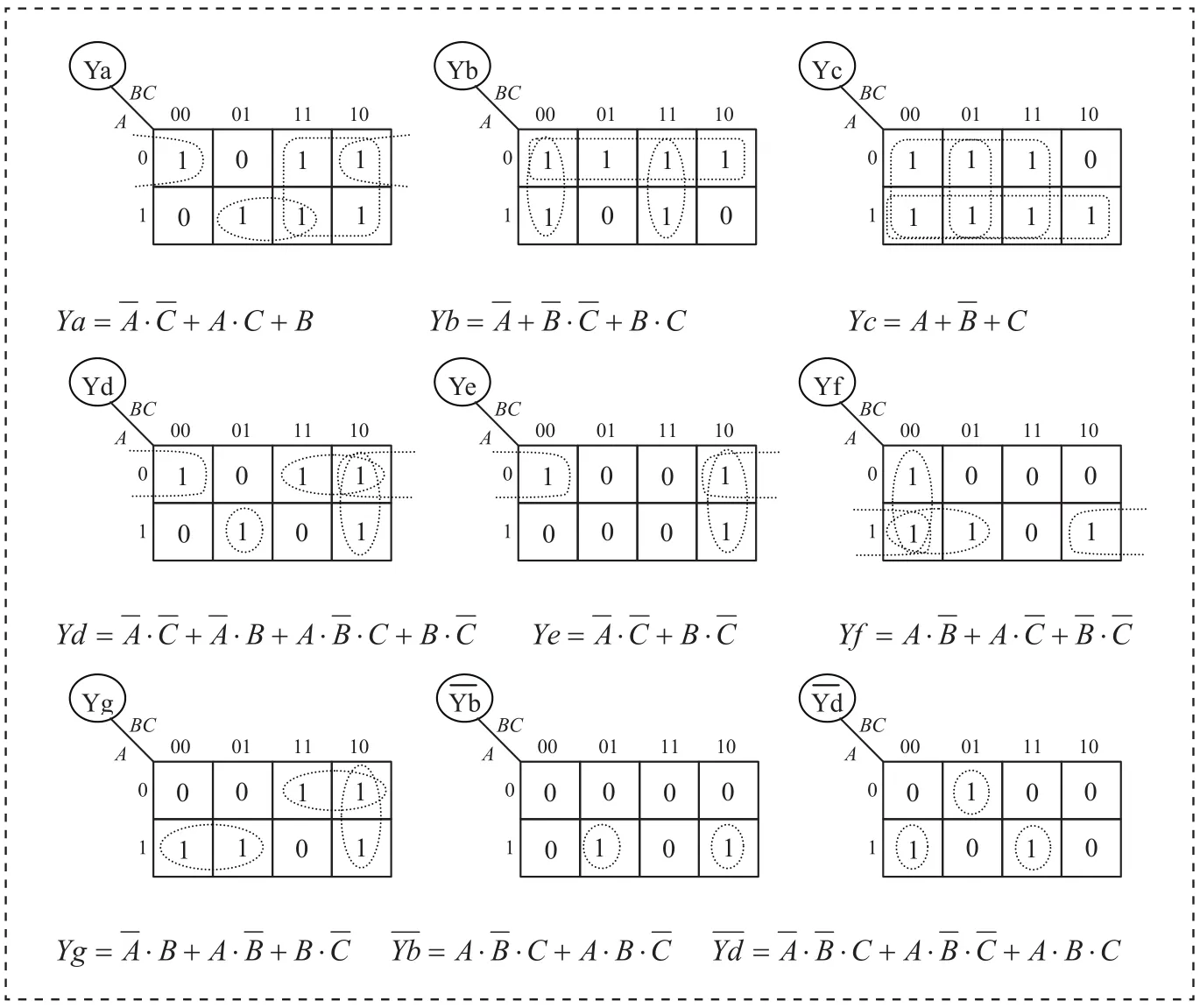

由表2可得各段卡诺图及其化简结果(最简与或式)如图5所示。

图5 各段卡若图及其最简与或式

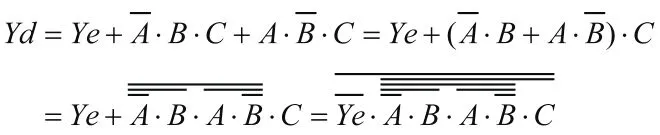

由于T065是四-二输入与非门,所以应将各段用摩根定理化简成二输入与非门的形式。又为减少元器件,应尽量找出各段之间的公共部分以及各段之间的关系。观察Ya与Yd段卡若图可知,两卡若图只有一个最小项m7不同,其余各项均相同。所以Ya=Yd+m7。Yd段加上最小项m7后,又可与最小项m2、m3、m6圈成一个卡若圈而合并成B。因此最终得:(共需3个与非门,包括两个反相器)

最后,

整个电路的逻辑原理图如图6所示。图中Rg为限流电阻。其目的是避免因亮度太大而烧坏七段字形显示器内部的发光二极管。Rg的阻值可按如下方法选取。TTL逻辑电路输出高电平电压通常为3.6V。发光二极管(LED)的工作电压一般为1.5V~3.2V,取2V,驱动电流需几毫安至十几毫安,取10mA。则限流电阻Rg可计算如下:从而可选标称值为150Ω的电阻作为限流电阻。当然,也可以在Ya~Yg七段处各接一个限流电阻。

图6 八进制数字符号显示器逻辑原理图

从以上设计过程可看出,在用卡若图设计多输出组合逻辑电路时,首先需用摩根定理等公式将逻辑表达式化为所用器件的形式(如二输入与非式)。其次,为使所用的元器件最少,电路最简单,应尽量寻找各输出端的公共部分。此外,还应寻找各输出端的相互关系,也就是各卡若图之间的相互关系。而各卡若图之间的关系不外乎有以下三种。第一种,原卡若图加上所缺的最小项(如Ya=Yd+B)。第二种,原卡若图取反后加上所缺的最小项(如)。第三种,相等,即两个或两个以上输出端的卡若图完全相同。本文未涉及第三种情况,读者可查阅有关资料。但应注意,卡若图之间的关系不能递归调用。如Ya用了Yd加上其它项,反过来Yd就不能再用Ya加上其它项了。否则,电路将不能正常工作。

五、电路调试

整个电路调试在数字电路实验箱上分三步进行。第一步,先调试编码器。在数字电路实验箱上用T063或74LS20按图6左边编码器部分搭接编码器电路,并将其输出A、B、C分别连接三个LED指示灯。通电前先将K0~K7八个逻辑开关拨到高电平Vcc。通电后分别将K0~K7八个开关拨到低电平(地)观看三个LED指示灯的亮灭情况。若K0接地,三个LED指示灯均不亮,K1接地,C灯亮,K2接地,B灯亮,……,K7接地,A、B、C三个指示灯均亮,则编码器正确。第二步,再调试译码器。在数字电路实验箱上用T065或SN7400按图6右边译码器部分搭接译码器电路,并将其输入A、B、C分别连接三个逻辑开关。通电后拨动A、B、C三个逻辑开关,若数码管的显示情况与表2相符,则译码器正确。第三,最后将编码器与译码器连接进行统调。将编码器的三个输出端A、B、C与译码器的三个输入端A、B、C对应进行连接。通电后拨动K0~K7八个逻辑开关,观察数码管的显示情况。若K0接地,数码管显示0,若K1接地,数码管显示1,……,K7接地,数码管显示7,则整个电路正确。